运动控制领域,通常需要外扩FPGA实现高速脉冲收发、高速探针锁存、比较输出等功能,ARM和FPGA之间的接口通常选择并口(Localbus)或SPI接口。

FET153-S核心板引出了并口接口,但OK153-S开发板并口作为其它外设使用,无法进行测试,这里我们测试SPI是否可行。

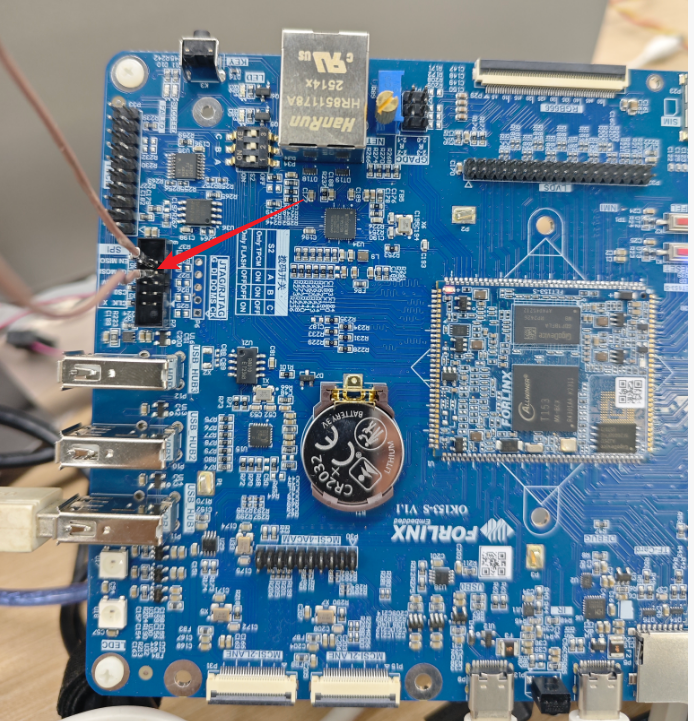

硬件方面,我们将MISO和MOSI引脚短接,模拟FPGA返回数据,如下所示,

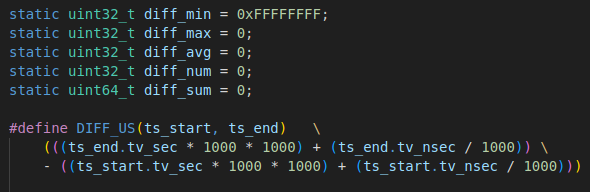

修改spidev_test.c中的transfer函数,计算ioctl函数的执行时间,并打印执行时间统计信息,

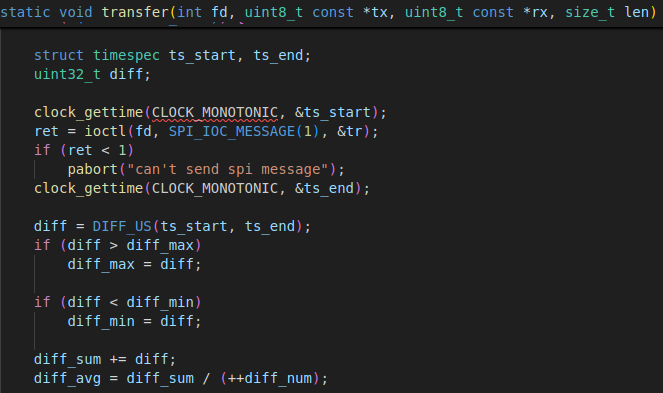

注意:红色方框中的usleep(1000)函数必须加入,一方面是模拟1ms的周期任务,另一方面没有睡眠函数,spidev_test会一直占用cpu,linux调度器会惩罚该进程,导致测试不准确。

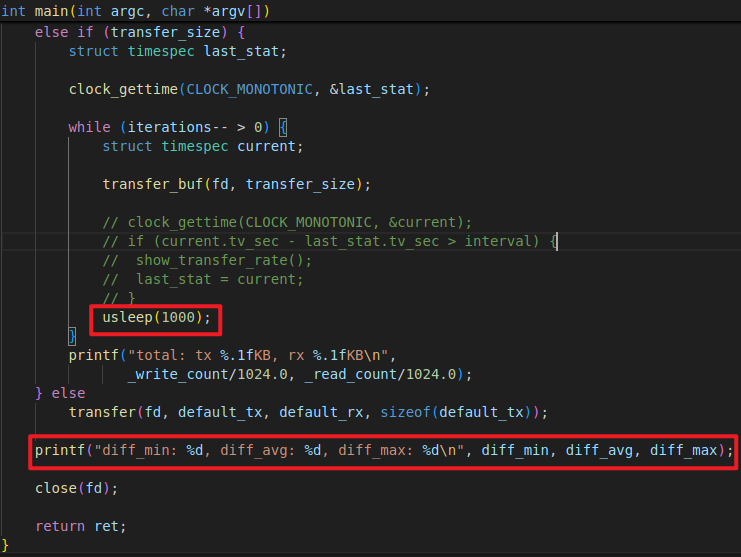

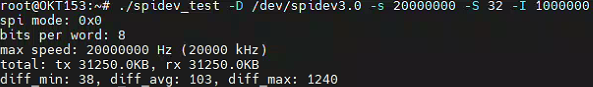

spi clk主频设置为20M,每次传输32个字节,测试100w次传输的结果如下所示,

通过以上测试,发现20M频率下,传输32个字节最大执行时间为1.24ms。

在运动控制领域,任务周期通常为1ms、2ms、4ms,1.24ms的通讯执行时间远超过了任务周期,会导致数据采集不够实时。

为了解决目前的延迟,进行如下优化:

将spi3外设中断绑定到其它cpu

将线程化的spi3中断优先级提高到80

将后台的[spi3]内核线程优先级也提高到80

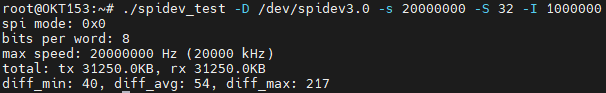

再进行测试,

总结,spi3外设经过优化后,传输一次数据时间最大需要217us,已完全满足实时系统的需要。

更多回帖