本文主要交流设计思路,在本博客已给出相关博文约九十篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。

1)初始化功能测试

系统在上电复位后, 首先由 PCIE 集成块执行链路训练, 链路训练在百毫秒级别

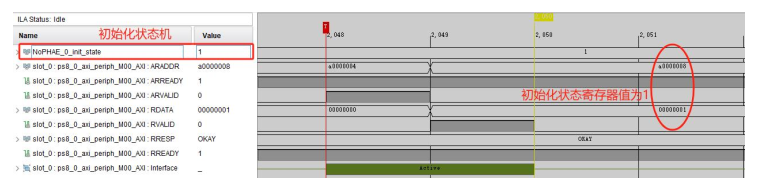

时间内完成, 链路训练成功后, 读取初始化状态寄存器值, 上电复位后通过 ILA 抓

取的初始化状态机和系统控制模块 axi_lite 接口信号如图 1 所示。 此时初始化状态

机(NoPHAE_init_state) 值为 1, 处于 PCIe 链路训练状态。 读取地址为 0xA0000008,

该地址为初始化状态寄存器, 读取值为 1, 表示链路训练成功。

图1 链路训练状态波形图

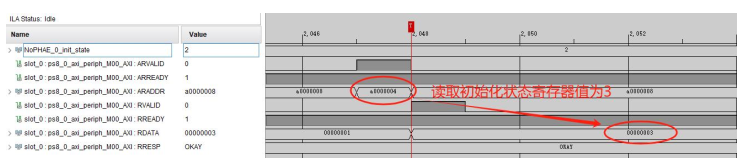

PCIe 初始化完成时的信号波形如图 2 所示。 读取地址为 0xA0000004 的初始化状态寄存器, 读取值为 3, 表示 PCIe 初始化完成。

图2 PCIe 初始化完成波形图

更多回帖