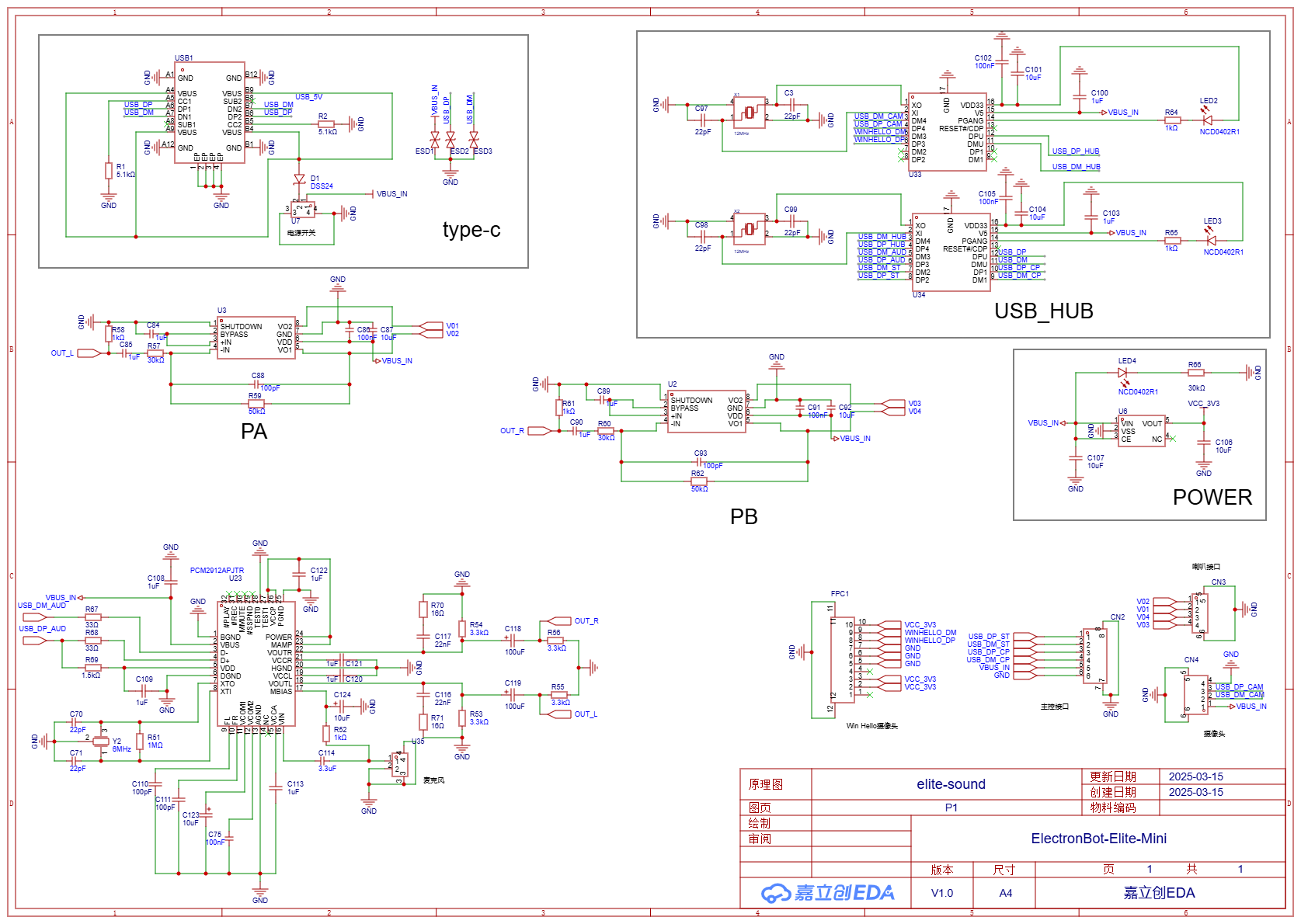

针对PCM2912APJTR设计的USB声卡出现哒哒声的问题,以下是可能原因及改进建议的详细分析:

一、电源问题(高频噪声/纹波干扰)

电源滤波不足

- 现象:模拟电源(AVDD)或数字电源(DVDD)的滤波电容缺失或容值不合理。

- 检查点:

- 确保芯片的电源引脚(如AVDD、DVDD)就近放置 10μF电解电容 + 0.1μF陶瓷电容 组合,且电容接地路径短。

- USB输入的5V电源需增加 共模电感 或 磁珠(如600Ω@100MHz) 隔离高频噪声。

- 改进建议:

- 在USB 5V输入端增加TVS二极管(如SMAJ5.0A)抑制浪涌,并添加π型滤波电路(如10μF+磁珠+0.1μF)。

电源隔离不充分

- 现象:数字电源(DVDD)与模拟电源(AVDD)未隔离,导致数字噪声耦合到模拟部分。

- 改进建议:

- 使用 磁珠或0Ω电阻 将AVDD与DVDD分开供电,并在PCB布局中保持两者电源线不交叉。

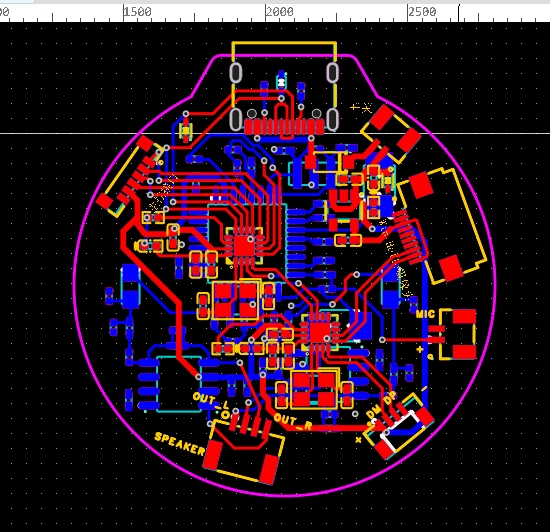

二、地线设计问题

地平面分割不当

- 现象:数字地(DGND)和模拟地(AGND)直接大面积连接,导致地回流路径混乱。

- 改进建议:

- 采用 单点接地 策略,通过 0Ω电阻或磁珠 将AGND和DGND在芯片下方连接。

- 避免音频信号线跨越地平面分割缝隙。

地线环路

- 现象:USB外壳地(SHIELD)与信号地(GND)直接连接,形成地环路。

- 改进建议:

- USB外壳地通过 1MΩ电阻并联1000pF电容 连接到信号地,防止低频噪声耦合。

三、时钟信号干扰

晶振布局问题

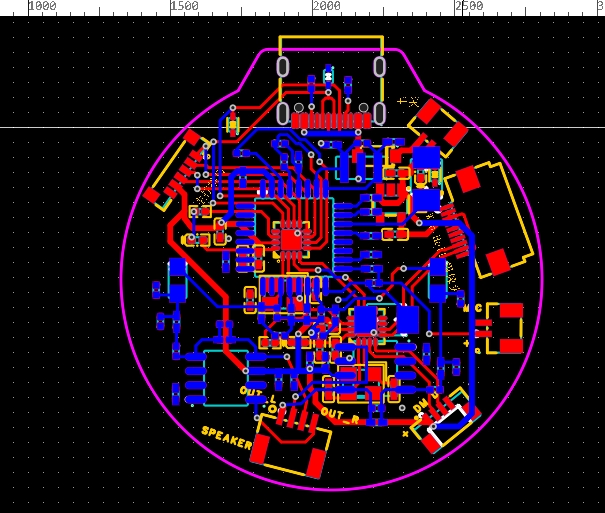

- 现象:晶振(12MHz)走线过长或靠近数字信号线,导致时钟噪声耦合到音频信号。

- 改进建议:

- 晶振尽量靠近芯片XTAL引脚,下方禁止走其他信号线,周围铺地铜并打地过孔。

- 检查晶振负载电容(典型值12-22pF)是否匹配芯片规格。

时钟信号完整性

- 现象:晶振输出波形畸变(如过冲、振铃)。

- 改进建议:

- 使用示波器测量时钟信号,必要时在晶振输出端串联 22Ω电阻 抑制反射。

四、PCB布局与信号线问题

音频信号线受干扰

- 现象:音频输出线(LOUT/ROUT)与USB差分线(D+/D-)或电源线平行走线。

- 改进建议:

- 音频信号线与其他高频信号(如USB、时钟)保持 3倍线宽间距 ,并用地铜包围隔离。

- 音频输出线尽量短,避免使用过孔,必要时在信号线上串联 10Ω电阻 抑制振铃。

USB差分线阻抗控制

- 现象:USB差分线未做90Ω阻抗匹配,导致信号反射。

- 改进建议:

- 计算差分线宽和间距(如FR4板材,线宽0.2mm,间距0.15mm),参考 USB 2.0阻抗设计规范 。

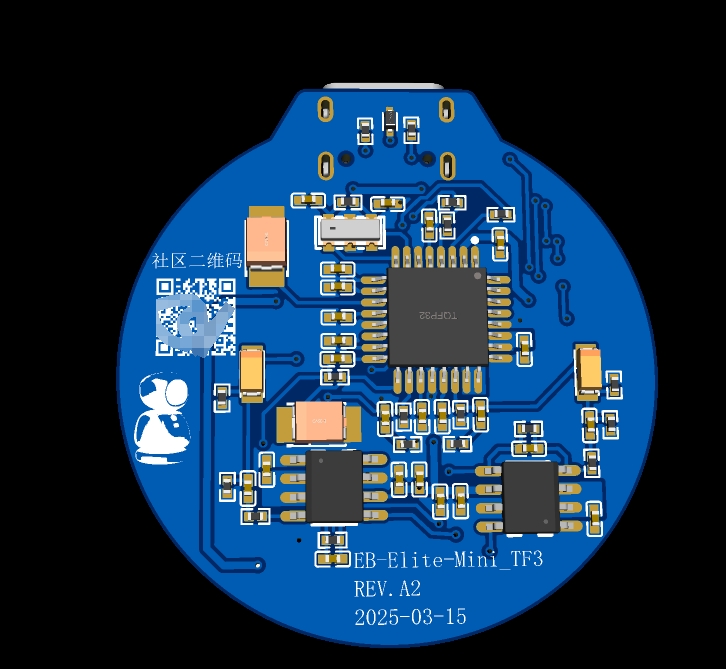

五、焊接与元件选型

焊接质量问题

- 现象:芯片引脚虚焊或电容极性反接。

- 检查点:

- 用放大镜检查PCM2912A引脚焊接,重点排查AGND、AVDD等关键引脚。

- 确认电解电容极性(如钽电容反接会短路)。

元件参数错误

- 现象:参考电路中的RC滤波参数与官方设计不符(例如MIC偏置电阻错误)。

- 改进建议:

- 核对数据手册中推荐的元件值(如MIC_BIAS电阻通常为2.2kΩ)。

六、调试工具建议

示波器测量

- 测量AVDD电压纹波(应<50mVpp),若纹波过大,需优化电源滤波。

- 检查音频输出端波形,观察哒哒声是否伴随周期性脉冲干扰。

热成像检测

- 使用热像仪排查是否有元件异常发热(如虚焊导致接触电阻过大)。

七、修改案例参考

- 某成功案例改进方案:

原设计哒哒声因AVDD滤波电容距离芯片过远(>5mm),修改后将10μF电容移至芯片背面(通过过孔直连),噪声消失。

通过以上逐项排查,重点优先检查 电源滤波 和 地线设计,这两个问题在初学者设计中占比超过70%。如果仍无法解决,建议提供更清晰的PCB走线截图(尤其是电源、地、时钟区域),以便进一步分析。

针对PCM2912APJTR设计的USB声卡出现哒哒声的问题,以下是可能原因及改进建议的详细分析:

一、电源问题(高频噪声/纹波干扰)

电源滤波不足

- 现象:模拟电源(AVDD)或数字电源(DVDD)的滤波电容缺失或容值不合理。

- 检查点:

- 确保芯片的电源引脚(如AVDD、DVDD)就近放置 10μF电解电容 + 0.1μF陶瓷电容 组合,且电容接地路径短。

- USB输入的5V电源需增加 共模电感 或 磁珠(如600Ω@100MHz) 隔离高频噪声。

- 改进建议:

- 在USB 5V输入端增加TVS二极管(如SMAJ5.0A)抑制浪涌,并添加π型滤波电路(如10μF+磁珠+0.1μF)。

电源隔离不充分

- 现象:数字电源(DVDD)与模拟电源(AVDD)未隔离,导致数字噪声耦合到模拟部分。

- 改进建议:

- 使用 磁珠或0Ω电阻 将AVDD与DVDD分开供电,并在PCB布局中保持两者电源线不交叉。

二、地线设计问题

地平面分割不当

- 现象:数字地(DGND)和模拟地(AGND)直接大面积连接,导致地回流路径混乱。

- 改进建议:

- 采用 单点接地 策略,通过 0Ω电阻或磁珠 将AGND和DGND在芯片下方连接。

- 避免音频信号线跨越地平面分割缝隙。

地线环路

- 现象:USB外壳地(SHIELD)与信号地(GND)直接连接,形成地环路。

- 改进建议:

- USB外壳地通过 1MΩ电阻并联1000pF电容 连接到信号地,防止低频噪声耦合。

三、时钟信号干扰

晶振布局问题

- 现象:晶振(12MHz)走线过长或靠近数字信号线,导致时钟噪声耦合到音频信号。

- 改进建议:

- 晶振尽量靠近芯片XTAL引脚,下方禁止走其他信号线,周围铺地铜并打地过孔。

- 检查晶振负载电容(典型值12-22pF)是否匹配芯片规格。

时钟信号完整性

- 现象:晶振输出波形畸变(如过冲、振铃)。

- 改进建议:

- 使用示波器测量时钟信号,必要时在晶振输出端串联 22Ω电阻 抑制反射。

四、PCB布局与信号线问题

音频信号线受干扰

- 现象:音频输出线(LOUT/ROUT)与USB差分线(D+/D-)或电源线平行走线。

- 改进建议:

- 音频信号线与其他高频信号(如USB、时钟)保持 3倍线宽间距 ,并用地铜包围隔离。

- 音频输出线尽量短,避免使用过孔,必要时在信号线上串联 10Ω电阻 抑制振铃。

USB差分线阻抗控制

- 现象:USB差分线未做90Ω阻抗匹配,导致信号反射。

- 改进建议:

- 计算差分线宽和间距(如FR4板材,线宽0.2mm,间距0.15mm),参考 USB 2.0阻抗设计规范 。

五、焊接与元件选型

焊接质量问题

- 现象:芯片引脚虚焊或电容极性反接。

- 检查点:

- 用放大镜检查PCM2912A引脚焊接,重点排查AGND、AVDD等关键引脚。

- 确认电解电容极性(如钽电容反接会短路)。

元件参数错误

- 现象:参考电路中的RC滤波参数与官方设计不符(例如MIC偏置电阻错误)。

- 改进建议:

- 核对数据手册中推荐的元件值(如MIC_BIAS电阻通常为2.2kΩ)。

六、调试工具建议

示波器测量

- 测量AVDD电压纹波(应<50mVpp),若纹波过大,需优化电源滤波。

- 检查音频输出端波形,观察哒哒声是否伴随周期性脉冲干扰。

热成像检测

- 使用热像仪排查是否有元件异常发热(如虚焊导致接触电阻过大)。

七、修改案例参考

- 某成功案例改进方案:

原设计哒哒声因AVDD滤波电容距离芯片过远(>5mm),修改后将10μF电容移至芯片背面(通过过孔直连),噪声消失。

通过以上逐项排查,重点优先检查 电源滤波 和 地线设计,这两个问题在初学者设计中占比超过70%。如果仍无法解决,建议提供更清晰的PCB走线截图(尤其是电源、地、时钟区域),以便进一步分析。

举报

举报

举报

举报