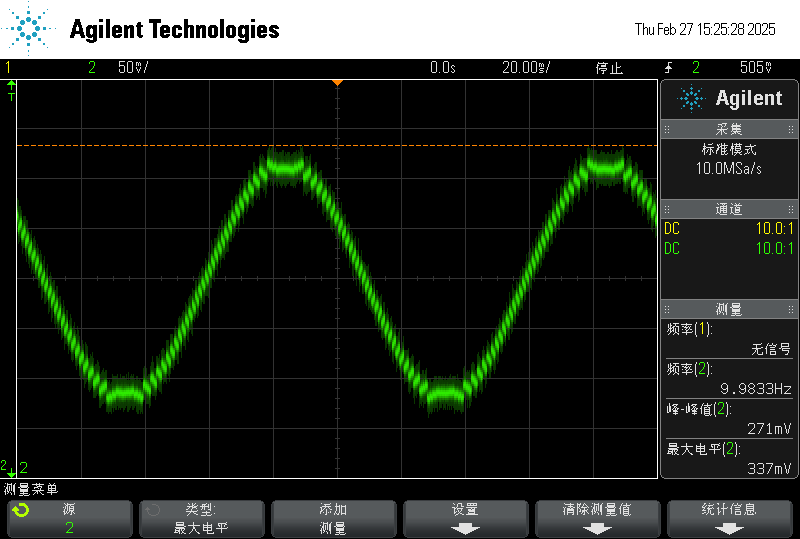

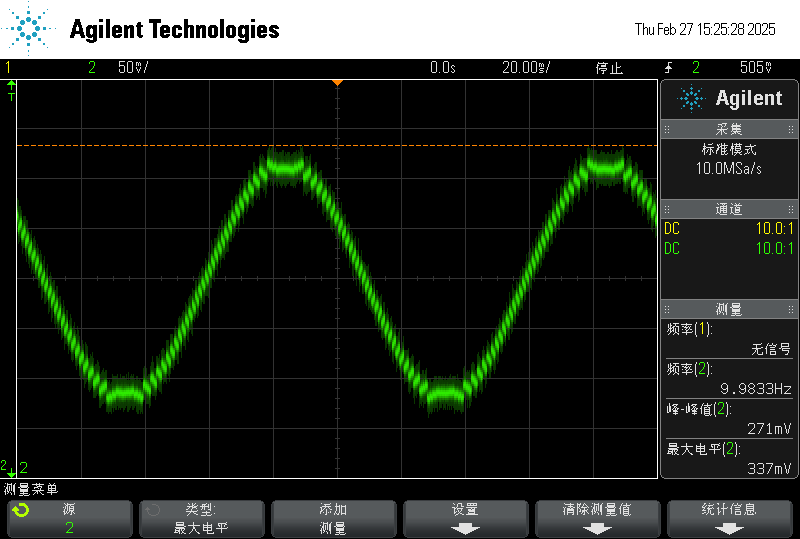

从你的描述来看,DAC(AD9142A)输出的正弦波在示波器上出现了分段现象,且每四段就有一个阶跃,形成“台阶”状失真。这种现象可能与以下几个方面的原因有关:

1. DDS(直接数字频率合成)输出问题

- DDS分辨率不足:DDS的输出分辨率可能不足以平滑地生成低频信号。DDS的核心是一个相位累加器,其输出通过查找表(LUT)映射到正弦波值。如果相位累加器的位数不足,或者查找表的深度不够,会导致输出波形出现阶梯状失真。

- 相位累加器溢出:DDS的相位累加器在达到最大值后会溢出,重新开始计数。如果溢出处理不当,可能会导致输出波形出现不连续的阶跃。

2. DAC(AD9142A)的问题

- DAC的分辨率:AD9142A是一个高速DAC,但如果DAC的分辨率不足(例如,位数不够高),在输出低频信号时,量化误差会更加明显,导致波形出现阶梯状失真。

- 时钟同步问题:DAC的时钟与DDS的时钟可能存在同步问题,导致输出波形出现不连续的阶跃。特别是在低频时,时钟同步问题更容易被观察到。

3. FPGA控制问题

- FPGA的时序控制:FPGA在控制DAC时,可能存在时序问题,导致数据在传输过程中出现错误或不连续。特别是在低频时,时序问题更容易导致波形失真。

- 数据缓冲问题:如果FPGA与DAC之间的数据缓冲区设计不当,可能会导致数据丢失或不连续,从而在输出波形上形成阶跃。

4. 信号处理问题

- 插值滤波器:AD9142A内部通常会有插值滤波器,用于平滑DAC的输出信号。如果插值滤波器的设置不当,可能会导致输出波形出现阶梯状失真。

- 信号带宽限制:DAC的输出信号带宽可能受到限制,特别是在低频时,信号带宽不足会导致波形失真。

5. 高频输出问题

- 高频输出点数不足:在高频时,DDS的输出点数可能较少(如你提到的8个点),这会导致输出波形不够平滑。DDS的输出点数与输出频率成反比,频率越高,输出点数越少。

可能的解决方案:

- 提高DDS的分辨率:检查DDS的相位累加器位数和查找表深度,确保它们足够高,以生成平滑的低频信号。

- 优化DAC的时钟同步:确保DAC的时钟与DDS的时钟同步,避免时钟抖动或相位差导致的波形失真。

- 检查FPGA的时序控制:确保FPGA在控制DAC时,数据传输的时序正确,避免数据丢失或不连续。

- 调整插值滤波器:检查AD9142A的插值滤波器设置,确保它能够有效平滑输出信号。

- 增加高频输出点数:在高频时,可以通过增加DDS的输出点数来改善波形平滑度,但这可能会增加系统资源消耗。

总结:

你描述的现象可能与DDS、DAC、FPGA控制等多个方面有关。建议从DDS的分辨率、DAC的时钟同步、FPGA的时序控制等方面入手,逐步排查问题。特别是低频时的阶梯状失真,通常与DDS的分辨率和DAC的量化误差有关,而高频时的输出点数不足则可以通过优化DDS的输出参数来改善。

从你的描述来看,DAC(AD9142A)输出的正弦波在示波器上出现了分段现象,且每四段就有一个阶跃,形成“台阶”状失真。这种现象可能与以下几个方面的原因有关:

1. DDS(直接数字频率合成)输出问题

- DDS分辨率不足:DDS的输出分辨率可能不足以平滑地生成低频信号。DDS的核心是一个相位累加器,其输出通过查找表(LUT)映射到正弦波值。如果相位累加器的位数不足,或者查找表的深度不够,会导致输出波形出现阶梯状失真。

- 相位累加器溢出:DDS的相位累加器在达到最大值后会溢出,重新开始计数。如果溢出处理不当,可能会导致输出波形出现不连续的阶跃。

2. DAC(AD9142A)的问题

- DAC的分辨率:AD9142A是一个高速DAC,但如果DAC的分辨率不足(例如,位数不够高),在输出低频信号时,量化误差会更加明显,导致波形出现阶梯状失真。

- 时钟同步问题:DAC的时钟与DDS的时钟可能存在同步问题,导致输出波形出现不连续的阶跃。特别是在低频时,时钟同步问题更容易被观察到。

3. FPGA控制问题

- FPGA的时序控制:FPGA在控制DAC时,可能存在时序问题,导致数据在传输过程中出现错误或不连续。特别是在低频时,时序问题更容易导致波形失真。

- 数据缓冲问题:如果FPGA与DAC之间的数据缓冲区设计不当,可能会导致数据丢失或不连续,从而在输出波形上形成阶跃。

4. 信号处理问题

- 插值滤波器:AD9142A内部通常会有插值滤波器,用于平滑DAC的输出信号。如果插值滤波器的设置不当,可能会导致输出波形出现阶梯状失真。

- 信号带宽限制:DAC的输出信号带宽可能受到限制,特别是在低频时,信号带宽不足会导致波形失真。

5. 高频输出问题

- 高频输出点数不足:在高频时,DDS的输出点数可能较少(如你提到的8个点),这会导致输出波形不够平滑。DDS的输出点数与输出频率成反比,频率越高,输出点数越少。

可能的解决方案:

- 提高DDS的分辨率:检查DDS的相位累加器位数和查找表深度,确保它们足够高,以生成平滑的低频信号。

- 优化DAC的时钟同步:确保DAC的时钟与DDS的时钟同步,避免时钟抖动或相位差导致的波形失真。

- 检查FPGA的时序控制:确保FPGA在控制DAC时,数据传输的时序正确,避免数据丢失或不连续。

- 调整插值滤波器:检查AD9142A的插值滤波器设置,确保它能够有效平滑输出信号。

- 增加高频输出点数:在高频时,可以通过增加DDS的输出点数来改善波形平滑度,但这可能会增加系统资源消耗。

总结:

你描述的现象可能与DDS、DAC、FPGA控制等多个方面有关。建议从DDS的分辨率、DAC的时钟同步、FPGA的时序控制等方面入手,逐步排查问题。特别是低频时的阶梯状失真,通常与DDS的分辨率和DAC的量化误差有关,而高频时的输出点数不足则可以通过优化DDS的输出参数来改善。

举报

举报

举报

举报

举报

举报

举报

举报