您好!关于ADS8320的采样率问题,您提到的数据手册中的信息是正确的。ADS8320的采样率确实与外部时钟频率(fclk)有关。根据您提供的信息,我们可以得出以下结论:

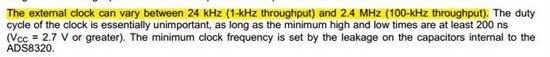

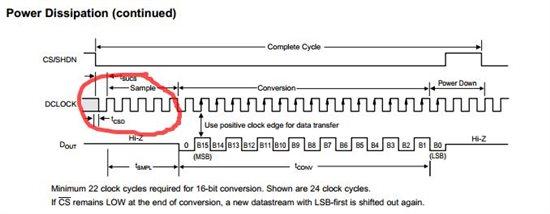

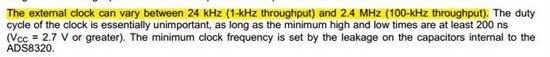

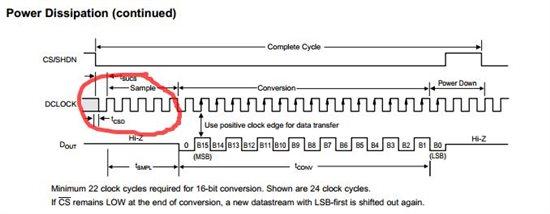

1. 当外部时钟频率在24 kHz(1-kHz 吞吐量)和2.4 MHz(100-kHz 吞吐量)之间变化时,采样率(fsample)与外部时钟频率(fclk)之间的关系是 fsample = fclk / 24。

2. 在您提到的/CS拉低后,DCLOCK前5个周期信号的频率是fclk的情况下,采样率fsample确实等于fclk/24。

因此,您的结论是正确的。在这种情况下,ADS8320的采样率fsample等于外部时钟频率fclk除以24。希望这能帮助您解决问题。如果您有其他疑问,请随时提问。

您好!关于ADS8320的采样率问题,您提到的数据手册中的信息是正确的。ADS8320的采样率确实与外部时钟频率(fclk)有关。根据您提供的信息,我们可以得出以下结论:

1. 当外部时钟频率在24 kHz(1-kHz 吞吐量)和2.4 MHz(100-kHz 吞吐量)之间变化时,采样率(fsample)与外部时钟频率(fclk)之间的关系是 fsample = fclk / 24。

2. 在您提到的/CS拉低后,DCLOCK前5个周期信号的频率是fclk的情况下,采样率fsample确实等于fclk/24。

因此,您的结论是正确的。在这种情况下,ADS8320的采样率fsample等于外部时钟频率fclk除以24。希望这能帮助您解决问题。如果您有其他疑问,请随时提问。

举报

举报

举报

举报

举报

举报