高速先生成员--姜杰

高速先生经常被Layout攻城狮问到这样的问题:“PCB上PIN尺寸看起来差不多的连接器,为啥SI攻城狮给出的阻抗优化方式不一样?是不是他们在故弄玄虚?”

根据高速先生的经验来看,大概率是他们看到了你们看不到的东西……

需要对阻抗进行优化的连接器,信号速率一般都不会低。比如,高速先生最近遇到的一个比较典型的案例:同一PCB上的两种连接器,一个最高支持16Gbps信号,一个可以支持到25Gbps的信号,下文为了方便起见,分别简称为16G连接器和25G连接器。

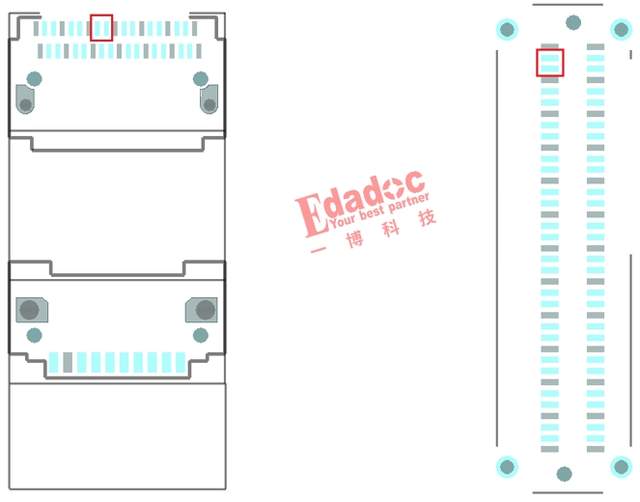

如果只看PCB上面的器件封装(红色方框是其中的一对高速管脚),想必大家都没办法区分哪个连接器支持的速率更高。

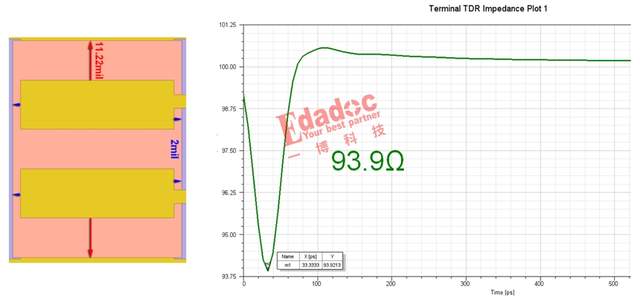

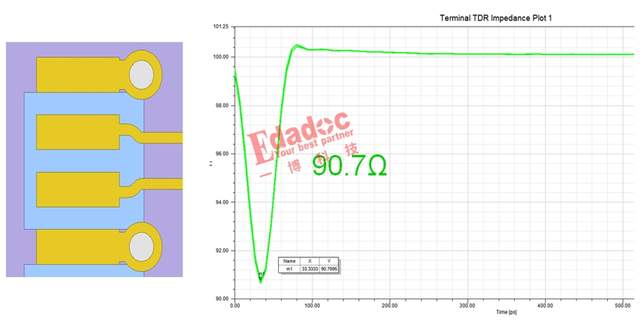

开始我们的研究,两种连接器布局面均在TOP层,差分信号特征阻抗要求100欧姆。直接看看二者在同一PCB上的阻抗表现如何。

首先出场的是25G连接器,反焊盘挖空第2层和第3层,参考第4层GND平面,此时的差分管脚阻抗可以做到93.9欧姆。

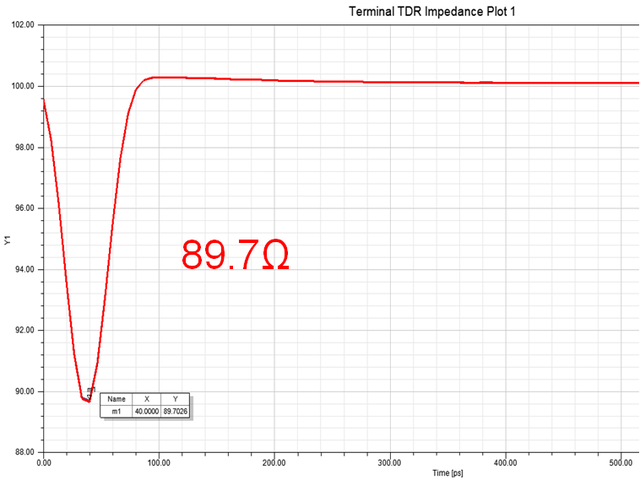

同样的反焊盘方案,用在16G连接器上,阻抗就只有89.7欧姆了。与25G连接器有4.2欧姆的差异,做过高速设计的同学应该都清楚这意味着什么。

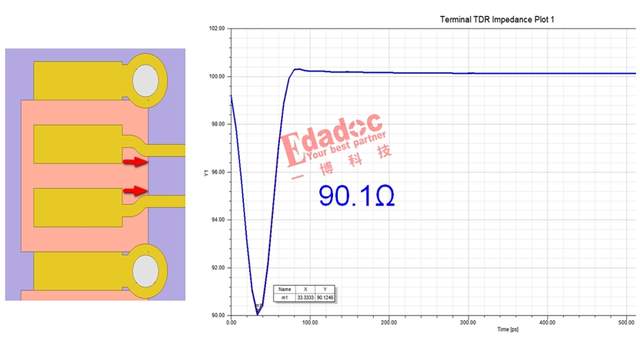

为了抢救一下16G连接器的阻抗,先把高速信号PIN的反焊盘尺寸扩大:反焊盘加宽5mil,其他不变的情况下,阻抗由89.7欧姆增加到90.1欧姆,不能说没有,聊胜于无。

别急,还有一招,增加PIN到参考平面的间距。具体到本案例,就是在反焊盘加宽5mil的基础上,继续挖空第4层和第5层,参考第6层GND平面!不得不说,为了优化阻抗也是拼了,完全不顾走线层面的一通猛挖。

看到结果,大家悬着的心,终于死了——只有0.6欧姆的阻抗提升。

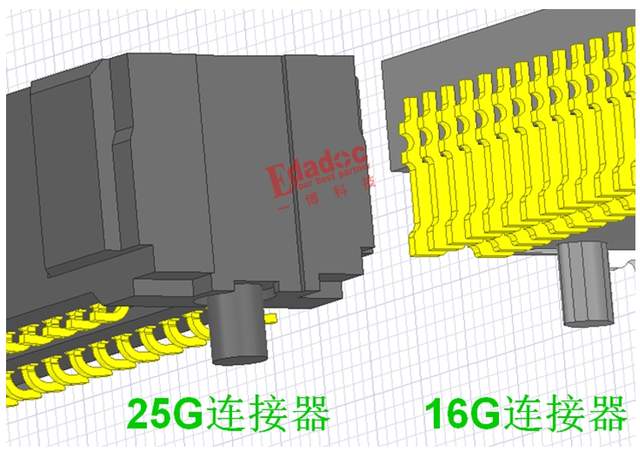

到底什么原因导致16G连接器的阻抗难以提升?是时候请出两个连接器的本尊了。

不知大家看出什么没有?没错,连接器3D模型的管脚差异比在PCB上看平面图可大多了,相比25G连接器的“三寸金莲”,16G连接器简直就是不折不扣的“大脚怪”。想想线宽和铜厚对阻抗的影响,大家应该都能猜到粗细管脚的阻抗差异。

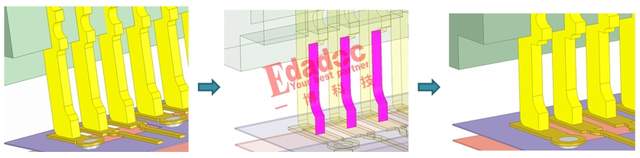

当然,高速先生是喜欢用数据说话的,既然怀疑是16G连接器的大脚拖了阻抗的后腿,那就直接把管脚变细:沿着红色侧面,把管脚内缩5mil。

果不其然,甚至都不用参考第6层,与25G连接器一样参考第4层地平面,阻抗一样能做到93.5欧姆!

回到本文开头的问题,Layout攻城狮之所以会产生困惑,就在于PCB设计软件上展示的PIN通常只是器件的焊盘,只有看到器件的3D模型(结构图)或者实物,才能发现真正的管脚差异。

当然了,实际设计过程中,Layout攻城狮基本动不了器件的封装尺寸,不过,不能改不代表不需要关注,在低头走线的过程中,也要抬头看看器件的3D模型。从二维到三维,维度提高,格局自然打开。

更多回帖