首先,我们需要查看提供的电路图网址,以了解ADS1256 EVM板子中J2模块的详细信息。然后,我们将讨论24位ADC测试中时钟模块的外围电路设计。

1. 对于24位ADC的测试,时钟模块的外围电路设计:

在24位ADC测试中,时钟模块的外围电路设计需要满足以下要求:

a. 时钟精度:24位ADC通常需要较高的时钟精度,以确保数据的准确性。因此,时钟源应具有较低的相位噪声和抖动。

b. 时钟频率:根据ADC的采样率要求,选择合适的时钟频率。24位ADC的采样率通常较高,因此需要一个高速的时钟源。

c. 时钟稳定性:时钟稳定性对于ADC的性能至关重要。因此,需要使用低相位噪声和低抖动的时钟源,并确保时钟路径的完整性。

d. 时钟分频:根据ADC的采样率要求,可能需要对时钟进行分频。可以使用PLL(相位锁定环)或其他分频器来实现。

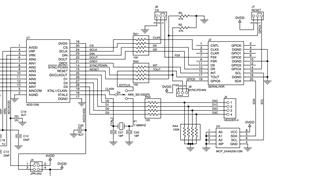

2. ADS1256 EVM板子中电路图J2模块:

经过查看电路图,J2模块是一个连接器,用于连接外部设备。具体作用和芯片型号如下:

a. 作用:J2模块是一个连接器,用于连接外部设备,如传感器、电源等。它提供了一个接口,使得外部设备可以与ADS1256 EVM板子进行通信和数据传输。

b. 芯片型号:在电路图中,J2模块没有明确标注芯片型号。通常,连接器不需要特定的芯片型号,因为它只是一个物理接口。但是,您可以参考电路图上的其他信息,如引脚分配和电气特性,以确定J2模块的具体型号和规格。

总之,对于24位ADC测试,时钟模块的外围电路设计需要满足高精度、高频率、高稳定性和适当的分频要求。而ADS1256 EVM板子中的J2模块是一个连接器,用于连接外部设备,具体型号和规格可以参考电路图上的其他信息。

首先,我们需要查看提供的电路图网址,以了解ADS1256 EVM板子中J2模块的详细信息。然后,我们将讨论24位ADC测试中时钟模块的外围电路设计。

1. 对于24位ADC的测试,时钟模块的外围电路设计:

在24位ADC测试中,时钟模块的外围电路设计需要满足以下要求:

a. 时钟精度:24位ADC通常需要较高的时钟精度,以确保数据的准确性。因此,时钟源应具有较低的相位噪声和抖动。

b. 时钟频率:根据ADC的采样率要求,选择合适的时钟频率。24位ADC的采样率通常较高,因此需要一个高速的时钟源。

c. 时钟稳定性:时钟稳定性对于ADC的性能至关重要。因此,需要使用低相位噪声和低抖动的时钟源,并确保时钟路径的完整性。

d. 时钟分频:根据ADC的采样率要求,可能需要对时钟进行分频。可以使用PLL(相位锁定环)或其他分频器来实现。

2. ADS1256 EVM板子中电路图J2模块:

经过查看电路图,J2模块是一个连接器,用于连接外部设备。具体作用和芯片型号如下:

a. 作用:J2模块是一个连接器,用于连接外部设备,如传感器、电源等。它提供了一个接口,使得外部设备可以与ADS1256 EVM板子进行通信和数据传输。

b. 芯片型号:在电路图中,J2模块没有明确标注芯片型号。通常,连接器不需要特定的芯片型号,因为它只是一个物理接口。但是,您可以参考电路图上的其他信息,如引脚分配和电气特性,以确定J2模块的具体型号和规格。

总之,对于24位ADC测试,时钟模块的外围电路设计需要满足高精度、高频率、高稳定性和适当的分频要求。而ADS1256 EVM板子中的J2模块是一个连接器,用于连接外部设备,具体型号和规格可以参考电路图上的其他信息。

举报

举报

举报

举报