您好,根据您的描述,ADS54J60在低采样率下无法完成同步的问题可能与以下几个方面有关:

1. JESD204B协议兼容性:首先,请确保您的FPGA和ADS54J60之间使用的JESD204B协议版本是兼容的。不同的JESD204B协议版本可能有不同的同步机制和要求。

2. 时钟频率范围:ADS54J60可能对时钟频率有一定的要求。在您的情况下,当信号源输出频率降低到600MHz以下时,同步信号(RX_SYNC)拉低。这可能是因为ADS54J60在低频率下无法正常工作。请查阅ADS54J60的数据手册,了解其对时钟频率的要求。

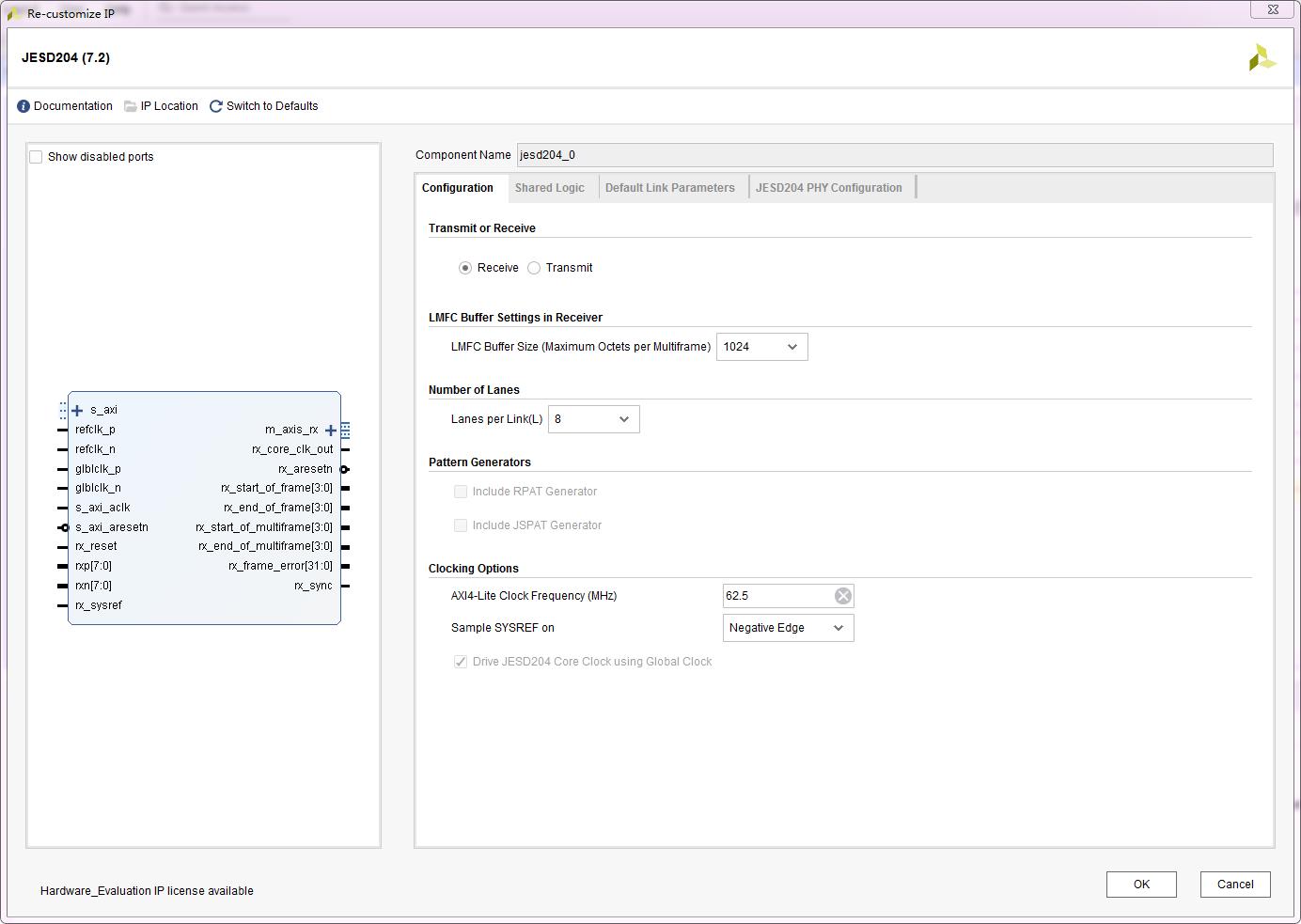

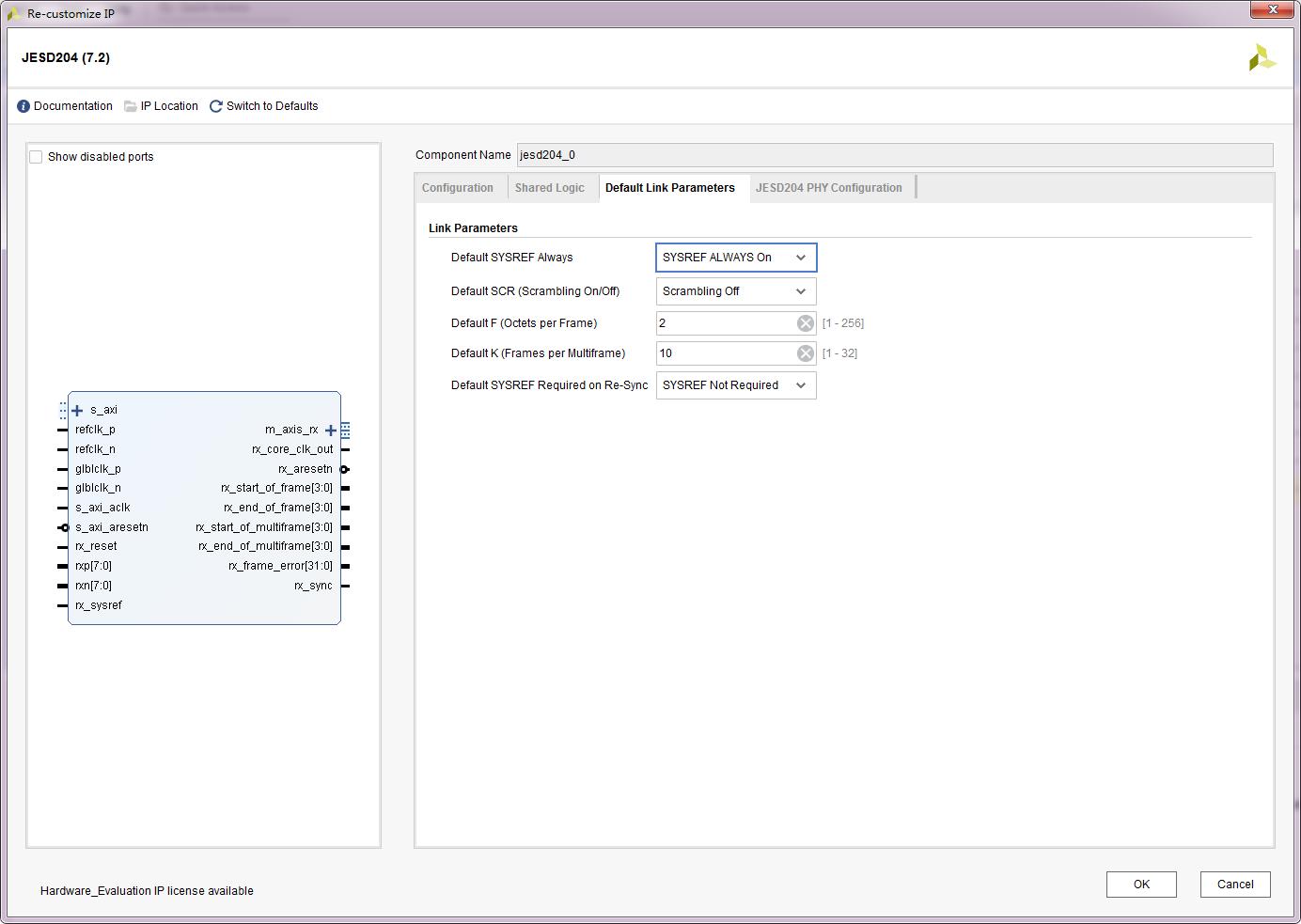

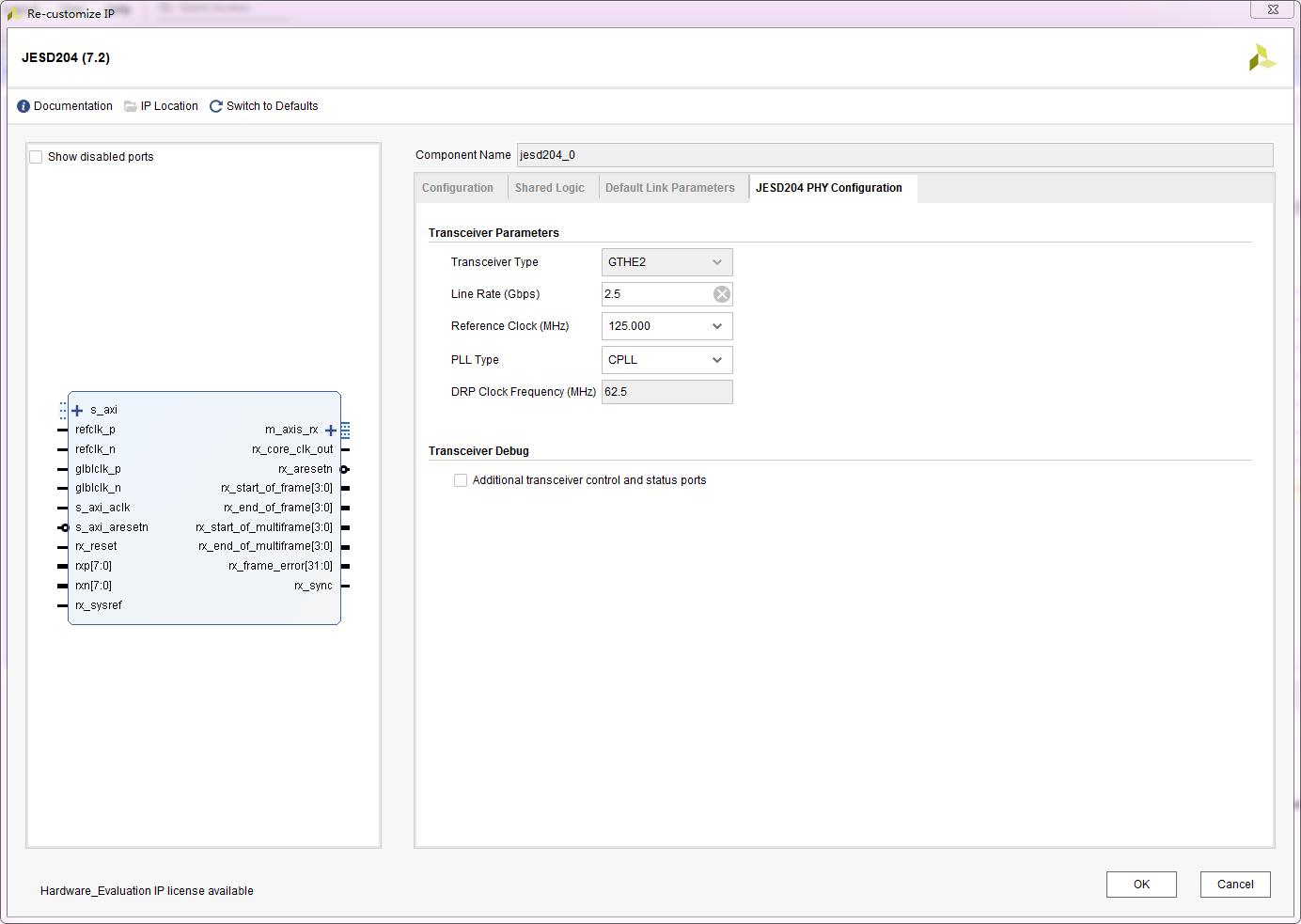

3. FPGA配置:您提到修改了FPGA的JESD204B IP核相关参数。请确保这些参数设置正确,以满足ADS54J60的工作要求。错误的配置可能导致同步问题。

4. 信号完整性:在降低采样率时,信号完整性可能会受到影响。请检查您的信号链路,确保信号在低采样率下仍然保持稳定和可靠。

5. FPGA和ADS54J60之间的通信:当204B同步信号拉低后,即使调高信号源采样率,同步信号依然不能拉高。这可能表明FPGA和ADS54J60之间的通信存在问题。请检查FPGA和ADS54J60之间的接口,确保它们之间的通信正常。

综上所述,要解决这个问题,您需要检查JESD204B协议兼容性、时钟频率范围、FPGA配置、信号完整性以及FPGA和ADS54J60之间的通信。希望这些建议能帮助您解决问题。

您好,根据您的描述,ADS54J60在低采样率下无法完成同步的问题可能与以下几个方面有关:

1. JESD204B协议兼容性:首先,请确保您的FPGA和ADS54J60之间使用的JESD204B协议版本是兼容的。不同的JESD204B协议版本可能有不同的同步机制和要求。

2. 时钟频率范围:ADS54J60可能对时钟频率有一定的要求。在您的情况下,当信号源输出频率降低到600MHz以下时,同步信号(RX_SYNC)拉低。这可能是因为ADS54J60在低频率下无法正常工作。请查阅ADS54J60的数据手册,了解其对时钟频率的要求。

3. FPGA配置:您提到修改了FPGA的JESD204B IP核相关参数。请确保这些参数设置正确,以满足ADS54J60的工作要求。错误的配置可能导致同步问题。

4. 信号完整性:在降低采样率时,信号完整性可能会受到影响。请检查您的信号链路,确保信号在低采样率下仍然保持稳定和可靠。

5. FPGA和ADS54J60之间的通信:当204B同步信号拉低后,即使调高信号源采样率,同步信号依然不能拉高。这可能表明FPGA和ADS54J60之间的通信存在问题。请检查FPGA和ADS54J60之间的接口,确保它们之间的通信正常。

综上所述,要解决这个问题,您需要检查JESD204B协议兼容性、时钟频率范围、FPGA配置、信号完整性以及FPGA和ADS54J60之间的通信。希望这些建议能帮助您解决问题。

举报

举报

举报

举报