您好,

输出两个点的时间间隔也就是更新时间,它是由数字接口的更新时间(update time)或

稳定时间( settling time)决定,哪个时间长由哪个决定。

计算数字接口的更新时间:

假设

SPI SCLK 的时钟频率为50MHz,根据Figure

7-1时序图,更新一个24bits的样本,需要的最小时间为tCSHIGH+tCSS+23tsclk+tCSH=505ns;

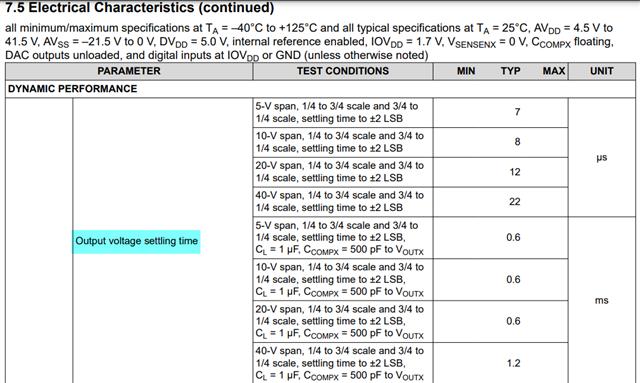

DAC81402的 settling

time如下截图,给出的是 DAC 从1/4全刻度范围步进至3/4*全刻度 的稳定时间, 这不是最快的稳定时间。如果 DAC 仅步进1

LSB,则更新时间会更短,因为 DAC 的小信号稳定速度要快得多。它同时与负载电容CL有关,CL越大settling time越长;可以看出 其settling

time是us级的,

因此,DAC81402的更新时间不受数字接口的限制,而是取决于稳定时间:

举报

举报

举报

举报

更多回帖