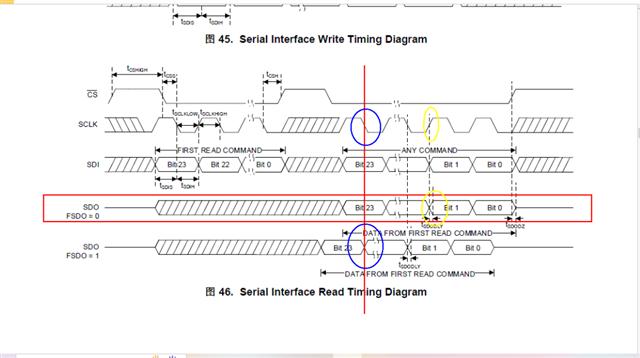

在这个问题中,我们需要分析DAC81416的FSDO定义和时序图,以确定为什么在FSDO=0时,SDO的bit位在时钟下降沿有效,但定义中写的是上升沿。

首先,我们来看一下FSDO的定义:

Fast SDO bit (half-cycle speedup). When 0, SDO updates during SCLK rising edges. When 1, SDO updates during SCLK falling edges.

根据这个定义,当FSDO=0时,SDO应该在SCLK的上升沿更新。然而,时序图显示在FSDO=0时,SDO的bit位在时钟下降沿有效。这似乎与定义相矛盾。

为了解决这个问题,我们需要考虑以下几个因素:

1. 时序图和定义可能存在错误或不一致。在这种情况下,我们需要查找官方文档或联系制造商以获取正确的信息。

2. 时序图可能表示的是实际的硬件行为,而定义可能表示的是预期的行为。在这种情况下,我们需要根据实际硬件行为来调整我们的理解和预期。

3. 可能存在一个误解或混淆。在这种情况下,我们需要重新审视问题和相关文档,以确保我们正确理解了FSDO和SDO的行为。

综上所述,为了解决这个问题,我们需要进一步调查和验证时序图和定义的一致性。如果时序图和定义确实存在矛盾,我们需要根据实际硬件行为来调整我们的理解和预期。同时,我们也可以联系制造商以获取正确的信息和支持。

在这个问题中,我们需要分析DAC81416的FSDO定义和时序图,以确定为什么在FSDO=0时,SDO的bit位在时钟下降沿有效,但定义中写的是上升沿。

首先,我们来看一下FSDO的定义:

Fast SDO bit (half-cycle speedup). When 0, SDO updates during SCLK rising edges. When 1, SDO updates during SCLK falling edges.

根据这个定义,当FSDO=0时,SDO应该在SCLK的上升沿更新。然而,时序图显示在FSDO=0时,SDO的bit位在时钟下降沿有效。这似乎与定义相矛盾。

为了解决这个问题,我们需要考虑以下几个因素:

1. 时序图和定义可能存在错误或不一致。在这种情况下,我们需要查找官方文档或联系制造商以获取正确的信息。

2. 时序图可能表示的是实际的硬件行为,而定义可能表示的是预期的行为。在这种情况下,我们需要根据实际硬件行为来调整我们的理解和预期。

3. 可能存在一个误解或混淆。在这种情况下,我们需要重新审视问题和相关文档,以确保我们正确理解了FSDO和SDO的行为。

综上所述,为了解决这个问题,我们需要进一步调查和验证时序图和定义的一致性。如果时序图和定义确实存在矛盾,我们需要根据实际硬件行为来调整我们的理解和预期。同时,我们也可以联系制造商以获取正确的信息和支持。

举报

举报

举报

举报

举报

举报