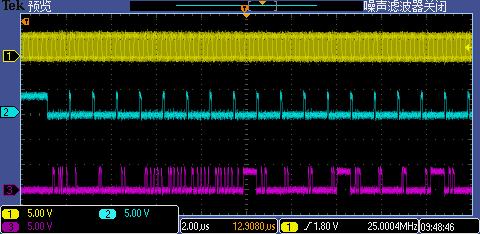

根据您的描述,DAC71416在25MHz的SCLK时钟下,一半端口没有输出,但在12.5MHz时钟下所有端口都正常工作。这可能是由于以下几个原因:

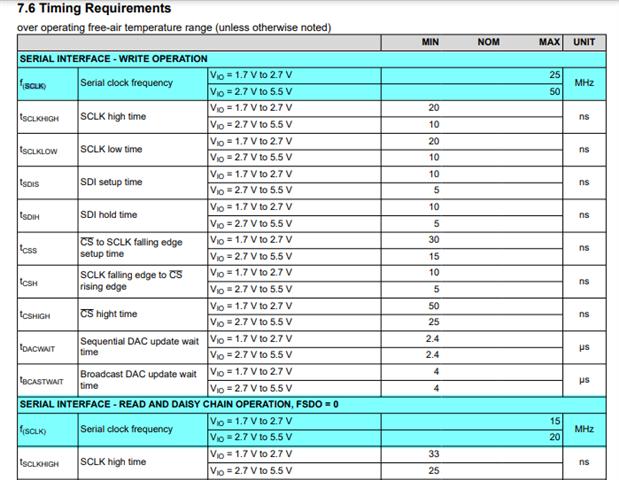

1. 时钟频率过高:虽然DAC71416的数据手册上提到它可以支持高达50MHz的时钟频率,但在实际应用中,可能由于电路设计、布线、信号完整性等因素导致实际工作频率低于理论值。在这种情况下,降低时钟频率可以提高系统的稳定性和可靠性。

2. 信号完整性问题:在高速SPI通信中,信号完整性是一个重要的考虑因素。可能存在信号反射、串扰、时序误差等问题,导致部分端口无法正常工作。在这种情况下,可以尝试优化电路设计,例如增加去耦电容、调整布线等,以提高信号完整性。

3. 电源噪声:高速SPI通信对电源稳定性要求较高。如果电源噪声较大,可能导致部分端口无法正常工作。可以尝试增加电源滤波器、优化电源布局等措施,以降低电源噪声。

4. 芯片质量问题:虽然不太可能,但也不能完全排除芯片质量问题。可以尝试更换其他同型号的DAC71416芯片,看是否仍然存在问题。

综上所述,建议您首先降低时钟频率,以确保系统的稳定性和可靠性。然后,逐步排查信号完整性问题、电源噪声问题等,以找到问题的根本原因。如果问题仍然存在,可以考虑更换其他同型号的DAC71416芯片进行测试。

根据您的描述,DAC71416在25MHz的SCLK时钟下,一半端口没有输出,但在12.5MHz时钟下所有端口都正常工作。这可能是由于以下几个原因:

1. 时钟频率过高:虽然DAC71416的数据手册上提到它可以支持高达50MHz的时钟频率,但在实际应用中,可能由于电路设计、布线、信号完整性等因素导致实际工作频率低于理论值。在这种情况下,降低时钟频率可以提高系统的稳定性和可靠性。

2. 信号完整性问题:在高速SPI通信中,信号完整性是一个重要的考虑因素。可能存在信号反射、串扰、时序误差等问题,导致部分端口无法正常工作。在这种情况下,可以尝试优化电路设计,例如增加去耦电容、调整布线等,以提高信号完整性。

3. 电源噪声:高速SPI通信对电源稳定性要求较高。如果电源噪声较大,可能导致部分端口无法正常工作。可以尝试增加电源滤波器、优化电源布局等措施,以降低电源噪声。

4. 芯片质量问题:虽然不太可能,但也不能完全排除芯片质量问题。可以尝试更换其他同型号的DAC71416芯片,看是否仍然存在问题。

综上所述,建议您首先降低时钟频率,以确保系统的稳定性和可靠性。然后,逐步排查信号完整性问题、电源噪声问题等,以找到问题的根本原因。如果问题仍然存在,可以考虑更换其他同型号的DAC71416芯片进行测试。

举报

举报

举报

举报

举报

举报