在调试ADC09QJ1300的过程中,如果发现建链不稳定的情况,可以尝试以下几个步骤来解决:

1. 检查硬件连接:

- 确保所有连接都正确无误,包括AD9517时钟芯片、ADC、FPGA等。

- 检查LVPECL电平是否匹配,确保信号完整性。

- 检查差分对连接是否正确,避免短路或接触不良。

2. 检查时钟配置:

- 确认AD9517时钟芯片产生的两路150MHz时钟是否稳定,可以使用示波器检查时钟波形。

- 确认ADC的输入时钟150MHz是否经过CPLL后产生600MHz的采样时钟,可以使用示波器检查采样时钟波形。

3. 检查JESD配置:

- 确认JESD配置是否正确,包括JMODE8模式、66/64b编码、4lane模式等。

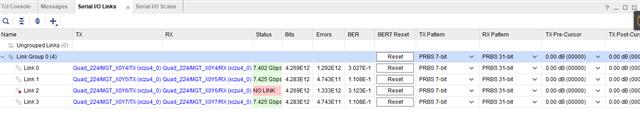

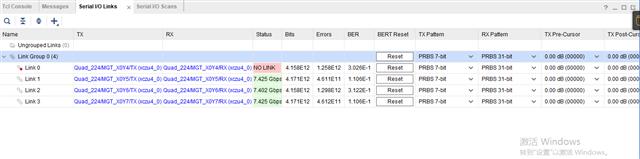

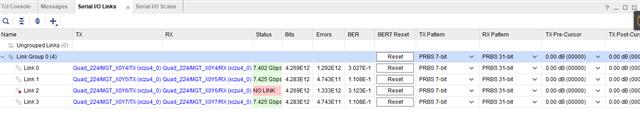

- 确认lane速率是否为7.425G,可以使用示波器检查lane速率。

4. 检查FPGA配置:

- 确认FPGA的gth口rx是否正确配置,包括速率、编码等。

- 检查FPGA的ibert是否正确配置,包括误码率、眼图等。

5. 检查信号完整性:

- 使用示波器检查ADC的D0+/-~D3+/-共4路差分对信号,确保信号完整性。

- 检查信号是否有过冲、欠冲、反射等问题,这些问题可能导致建链不稳定。

6. 检查PRBS31信号:

- 确认发送给FPGA的PRBS31信号是否正确,可以使用示波器检查PRBS31信号波形。

- 检查PRBS31信号是否有误码,可以使用误码检测工具检查。

7. 检查FPGA代码:

- 确认FPGA代码是否正确实现,包括JESD接口、gth口rx等。

- 检查FPGA代码是否有bug,可能导致建链不稳定。

8. 逐步调试:

- 逐步检查每个部分,包括硬件连接、时钟配置、JESD配置、FPGA配置等,找到问题所在。

- 逐步调整配置,直到找到稳定的建链。

通过以上步骤,应该可以找到导致建链不稳定的原因,并进行相应的调整,以实现稳定的建链。

在调试ADC09QJ1300的过程中,如果发现建链不稳定的情况,可以尝试以下几个步骤来解决:

1. 检查硬件连接:

- 确保所有连接都正确无误,包括AD9517时钟芯片、ADC、FPGA等。

- 检查LVPECL电平是否匹配,确保信号完整性。

- 检查差分对连接是否正确,避免短路或接触不良。

2. 检查时钟配置:

- 确认AD9517时钟芯片产生的两路150MHz时钟是否稳定,可以使用示波器检查时钟波形。

- 确认ADC的输入时钟150MHz是否经过CPLL后产生600MHz的采样时钟,可以使用示波器检查采样时钟波形。

3. 检查JESD配置:

- 确认JESD配置是否正确,包括JMODE8模式、66/64b编码、4lane模式等。

- 确认lane速率是否为7.425G,可以使用示波器检查lane速率。

4. 检查FPGA配置:

- 确认FPGA的gth口rx是否正确配置,包括速率、编码等。

- 检查FPGA的ibert是否正确配置,包括误码率、眼图等。

5. 检查信号完整性:

- 使用示波器检查ADC的D0+/-~D3+/-共4路差分对信号,确保信号完整性。

- 检查信号是否有过冲、欠冲、反射等问题,这些问题可能导致建链不稳定。

6. 检查PRBS31信号:

- 确认发送给FPGA的PRBS31信号是否正确,可以使用示波器检查PRBS31信号波形。

- 检查PRBS31信号是否有误码,可以使用误码检测工具检查。

7. 检查FPGA代码:

- 确认FPGA代码是否正确实现,包括JESD接口、gth口rx等。

- 检查FPGA代码是否有bug,可能导致建链不稳定。

8. 逐步调试:

- 逐步检查每个部分,包括硬件连接、时钟配置、JESD配置、FPGA配置等,找到问题所在。

- 逐步调整配置,直到找到稳定的建链。

通过以上步骤,应该可以找到导致建链不稳定的原因,并进行相应的调整,以实现稳定的建链。

举报

举报

举报

举报

举报

举报

举报

举报