LMC555是一款常用的定时器集成电路,其传播延时(propagation delay)通常在几十纳秒到几百纳秒之间。要将LMC555的传播延时降低到10ns以内,可以尝试以下几种方法:

1. 优化电源设计:确保LMC555的电源电压稳定且纹波较小,这有助于降低传播延时。可以使用低纹波的线性稳压器或高质量的开关稳压器,并在LMC555的电源引脚附近添加去耦电容。

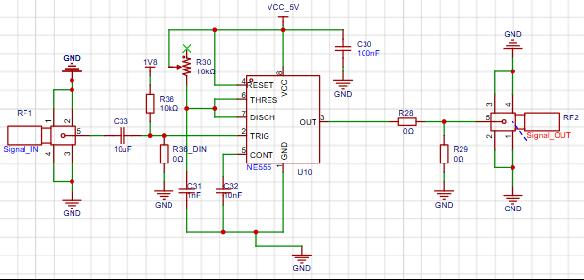

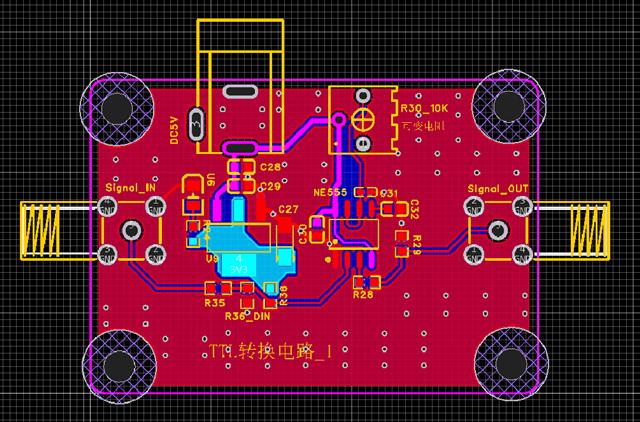

2. 优化电路布局:在PCB设计时,尽量减小LMC555的引脚与外部元件之间的连线长度,以减少信号传输延迟。同时,尽量将相关元件放置在LMC555附近,以减少信号路径长度。

3. 使用高速版本的LMC555:市场上有一些高速版本的LMC555,如LMC555M,其传播延时可能比标准版本的LMC555更低。可以考虑使用这些高速版本的LMC555来降低传播延时。

4. 调整触发电路参数:在单稳态触发电路中,可以通过调整电阻和电容的值来影响触发时间和传播延时。可以尝试减小电阻值和电容值,以降低触发时间和传播延时。但请注意,这可能会影响电路的稳定性和可靠性。

5. 使用其他高速定时器:如果以上方法仍无法满足10ns以内的传播延时要求,可以考虑使用其他高速定时器集成电路,如74系列的74HC系列或74AC系列等。这些高速定时器的传播延时通常在几纳秒到十几纳秒之间,可能更适合您的需求。

请注意,降低传播延时可能会影响电路的稳定性和可靠性,因此在优化传播延时时,请确保电路仍能满足其他性能要求。

LMC555是一款常用的定时器集成电路,其传播延时(propagation delay)通常在几十纳秒到几百纳秒之间。要将LMC555的传播延时降低到10ns以内,可以尝试以下几种方法:

1. 优化电源设计:确保LMC555的电源电压稳定且纹波较小,这有助于降低传播延时。可以使用低纹波的线性稳压器或高质量的开关稳压器,并在LMC555的电源引脚附近添加去耦电容。

2. 优化电路布局:在PCB设计时,尽量减小LMC555的引脚与外部元件之间的连线长度,以减少信号传输延迟。同时,尽量将相关元件放置在LMC555附近,以减少信号路径长度。

3. 使用高速版本的LMC555:市场上有一些高速版本的LMC555,如LMC555M,其传播延时可能比标准版本的LMC555更低。可以考虑使用这些高速版本的LMC555来降低传播延时。

4. 调整触发电路参数:在单稳态触发电路中,可以通过调整电阻和电容的值来影响触发时间和传播延时。可以尝试减小电阻值和电容值,以降低触发时间和传播延时。但请注意,这可能会影响电路的稳定性和可靠性。

5. 使用其他高速定时器:如果以上方法仍无法满足10ns以内的传播延时要求,可以考虑使用其他高速定时器集成电路,如74系列的74HC系列或74AC系列等。这些高速定时器的传播延时通常在几纳秒到十几纳秒之间,可能更适合您的需求。

请注意,降低传播延时可能会影响电路的稳定性和可靠性,因此在优化传播延时时,请确保电路仍能满足其他性能要求。

举报

举报

举报

举报

举报

举报