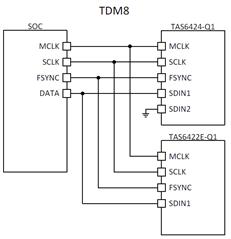

在系统设计中选择TAS6424E+TAS6422E的AMP方案,将MCLK与SCLK接到一起可能会带来一些限制和问题。以下是一些可能的限制和问题:

1. 时钟同步问题:将MCLK(主时钟)与SCLK(采样时钟)接到一起可能会导致时钟同步问题。在TDM(时分复用)接口中,时钟同步对于数据传输的稳定性和可靠性至关重要。如果MCLK和SCLK的频率不匹配,可能会导致数据传输错误。

2. 数据传输速率限制:将MCLK与SCLK接到一起可能会限制数据传输速率。在TDM接口中,数据传输速率通常受到时钟频率的限制。如果MCLK和SCLK的频率不匹配,可能会导致数据传输速率降低。

3. 信号干扰:将MCLK与SCLK接到一起可能会导致信号干扰。在电路设计中,信号线之间的距离和布局对信号干扰有很大影响。如果MCLK和SCLK的信号线距离过近,可能会导致信号干扰,从而影响数据传输的稳定性和可靠性。

4. 硬件设计复杂度:将MCLK与SCLK接到一起可能会增加硬件设计的复杂度。在电路设计中,需要考虑信号线的布局、电源分配、地线布局等因素。将MCLK与SCLK接到一起可能会增加这些因素的复杂度,从而导致硬件设计难度增加。

5. 系统稳定性:将MCLK与SCLK接到一起可能会影响系统的稳定性。在TDM接口中,时钟信号的稳定性对于数据传输的稳定性和可靠性至关重要。如果MCLK和SCLK的信号不稳定,可能会导致系统稳定性降低。

为了解决这些问题,可以考虑以下方案:

1. 使用独立的时钟源:为MCLK和SCLK分别使用独立的时钟源,以确保时钟同步和数据传输的稳定性。

2. 使用时钟分配器:使用时钟分配器将MCLK和SCLK分配到不同的信号线上,以减少信号干扰。

3. 优化信号线布局:在电路设计中,优化信号线的布局,以减少信号干扰和提高系统稳定性。

4. 使用高速接口:如果可能,可以考虑使用高速接口(如SPI、I2C等)来替代TDM接口,以提高数据传输速率和系统稳定性。

5. 增加硬件冗余:在硬件设计中,增加硬件冗余,以提高系统的稳定性和可靠性。

总之,在将MCLK与SCLK接到一起时,需要充分考虑时钟同步、数据传输速率、信号干扰、硬件设计复杂度和系统稳定性等因素,以确保系统的正常运行。

在系统设计中选择TAS6424E+TAS6422E的AMP方案,将MCLK与SCLK接到一起可能会带来一些限制和问题。以下是一些可能的限制和问题:

1. 时钟同步问题:将MCLK(主时钟)与SCLK(采样时钟)接到一起可能会导致时钟同步问题。在TDM(时分复用)接口中,时钟同步对于数据传输的稳定性和可靠性至关重要。如果MCLK和SCLK的频率不匹配,可能会导致数据传输错误。

2. 数据传输速率限制:将MCLK与SCLK接到一起可能会限制数据传输速率。在TDM接口中,数据传输速率通常受到时钟频率的限制。如果MCLK和SCLK的频率不匹配,可能会导致数据传输速率降低。

3. 信号干扰:将MCLK与SCLK接到一起可能会导致信号干扰。在电路设计中,信号线之间的距离和布局对信号干扰有很大影响。如果MCLK和SCLK的信号线距离过近,可能会导致信号干扰,从而影响数据传输的稳定性和可靠性。

4. 硬件设计复杂度:将MCLK与SCLK接到一起可能会增加硬件设计的复杂度。在电路设计中,需要考虑信号线的布局、电源分配、地线布局等因素。将MCLK与SCLK接到一起可能会增加这些因素的复杂度,从而导致硬件设计难度增加。

5. 系统稳定性:将MCLK与SCLK接到一起可能会影响系统的稳定性。在TDM接口中,时钟信号的稳定性对于数据传输的稳定性和可靠性至关重要。如果MCLK和SCLK的信号不稳定,可能会导致系统稳定性降低。

为了解决这些问题,可以考虑以下方案:

1. 使用独立的时钟源:为MCLK和SCLK分别使用独立的时钟源,以确保时钟同步和数据传输的稳定性。

2. 使用时钟分配器:使用时钟分配器将MCLK和SCLK分配到不同的信号线上,以减少信号干扰。

3. 优化信号线布局:在电路设计中,优化信号线的布局,以减少信号干扰和提高系统稳定性。

4. 使用高速接口:如果可能,可以考虑使用高速接口(如SPI、I2C等)来替代TDM接口,以提高数据传输速率和系统稳定性。

5. 增加硬件冗余:在硬件设计中,增加硬件冗余,以提高系统的稳定性和可靠性。

总之,在将MCLK与SCLK接到一起时,需要充分考虑时钟同步、数据传输速率、信号干扰、硬件设计复杂度和系统稳定性等因素,以确保系统的正常运行。

举报

举报

举报

举报

举报

举报