在解决TLV320AIC3104板卡信号测试中DOUT线上的异常电平问题时,我们可以按照以下步骤进行排查和解决:

1. 确认信号源:首先,我们需要确认信号源是否正常。检查外部提供的MCLK 12MHz信号是否稳定,以及BCLK 256KHz和WCLK 8KHz是否从MCLK正确分频生成。

2. 检查电源和地线:检查电源和地线是否连接正确,是否存在短路或接触不良的情况。电源不稳定或地线接触不良可能导致信号异常。

3. 检查PCB布局:虽然您提到在layout上检查了WCLK与BCLK的间距,但仍然需要仔细检查PCB布局,确保没有其他可能导致信号干扰的因素。例如,检查是否有过长的走线、不合理的布线或过小的间距等。

4. 检查器件安装:检查TLV320AIC3104芯片和其他相关器件是否正确安装在PCB上,是否存在焊接不良或接触不良的情况。

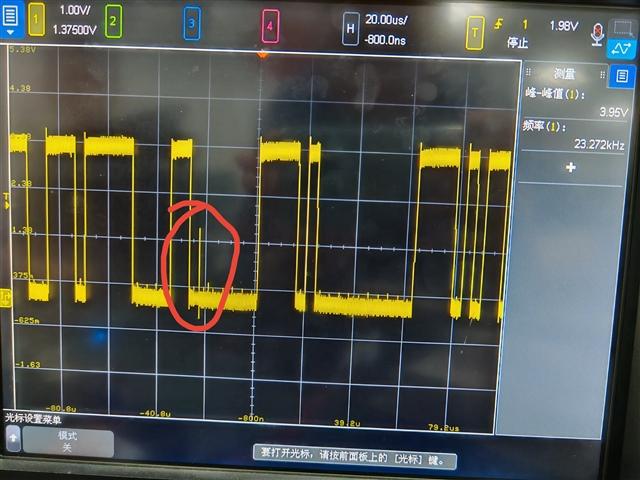

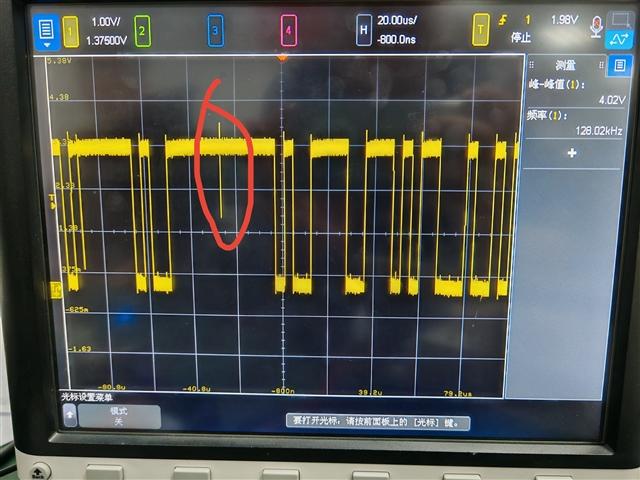

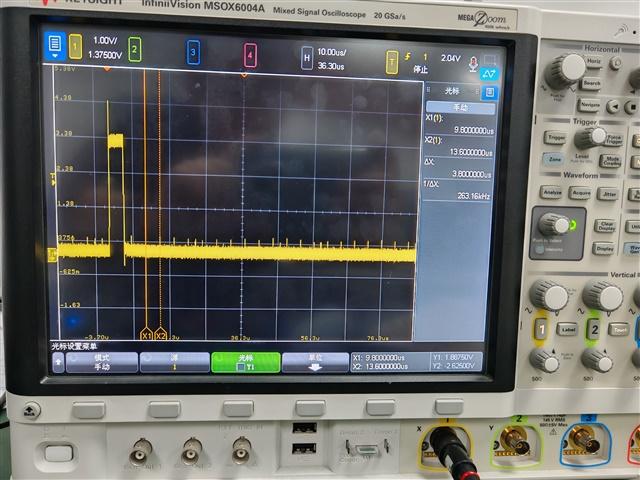

5. 检查信号完整性:使用示波器或逻辑分析仪检查DOUT线上的信号完整性,以确定异常电平是否是由于信号完整性问题导致的。

6. 考虑串扰问题:您提到在WCLK线上可以发现明显的串扰,这可能是导致DOUT线上异常电平的原因之一。尝试优化PCB布局,增加WCLK与BCLK之间的间距,或者在它们之间添加地线隔离,以减少串扰。

7. 参考TI评估套件:您提到在TI的评估套件TLV320AIC314EVM-K中也有类似现象,可以尝试参考评估套件的PCB布局和信号处理方式,看看是否有可以借鉴的地方。

8. 与TI技术支持联系:如果以上步骤都无法解决问题,可以考虑联系TI的技术支持,询问他们是否有关于这个问题的已知解决方案或建议。

通过以上步骤,我们可以尽量排查和解决DOUT线上的异常电平问题。至于这种现象是否正常,需要根据具体情况判断。如果异常电平对信号质量影响较大,可能需要进一步优化设计。

在解决TLV320AIC3104板卡信号测试中DOUT线上的异常电平问题时,我们可以按照以下步骤进行排查和解决:

1. 确认信号源:首先,我们需要确认信号源是否正常。检查外部提供的MCLK 12MHz信号是否稳定,以及BCLK 256KHz和WCLK 8KHz是否从MCLK正确分频生成。

2. 检查电源和地线:检查电源和地线是否连接正确,是否存在短路或接触不良的情况。电源不稳定或地线接触不良可能导致信号异常。

3. 检查PCB布局:虽然您提到在layout上检查了WCLK与BCLK的间距,但仍然需要仔细检查PCB布局,确保没有其他可能导致信号干扰的因素。例如,检查是否有过长的走线、不合理的布线或过小的间距等。

4. 检查器件安装:检查TLV320AIC3104芯片和其他相关器件是否正确安装在PCB上,是否存在焊接不良或接触不良的情况。

5. 检查信号完整性:使用示波器或逻辑分析仪检查DOUT线上的信号完整性,以确定异常电平是否是由于信号完整性问题导致的。

6. 考虑串扰问题:您提到在WCLK线上可以发现明显的串扰,这可能是导致DOUT线上异常电平的原因之一。尝试优化PCB布局,增加WCLK与BCLK之间的间距,或者在它们之间添加地线隔离,以减少串扰。

7. 参考TI评估套件:您提到在TI的评估套件TLV320AIC314EVM-K中也有类似现象,可以尝试参考评估套件的PCB布局和信号处理方式,看看是否有可以借鉴的地方。

8. 与TI技术支持联系:如果以上步骤都无法解决问题,可以考虑联系TI的技术支持,询问他们是否有关于这个问题的已知解决方案或建议。

通过以上步骤,我们可以尽量排查和解决DOUT线上的异常电平问题。至于这种现象是否正常,需要根据具体情况判断。如果异常电平对信号质量影响较大,可能需要进一步优化设计。

举报

举报

举报

举报