在将E203内核下载进

FPGA开发板后,使用Nuclei Studio烧录Hello World时OpenOCD报错

已经尝试过的方案

1.检查JTAG连接与约束,无误

2.将顶层中TDO从inout改成output,无效

3.重新安装驱动,无效

4.更换USB口,无效

硬件连接状况照片

硬件配置及软件版本

硬件配置及软件版本

开发板:黑金AX7020(xc7z020clg400-2)

下载器:蜂鸟Debugger Kit V2

IDE版本:NucleiStudio 2022.04

Nuclei项目配置

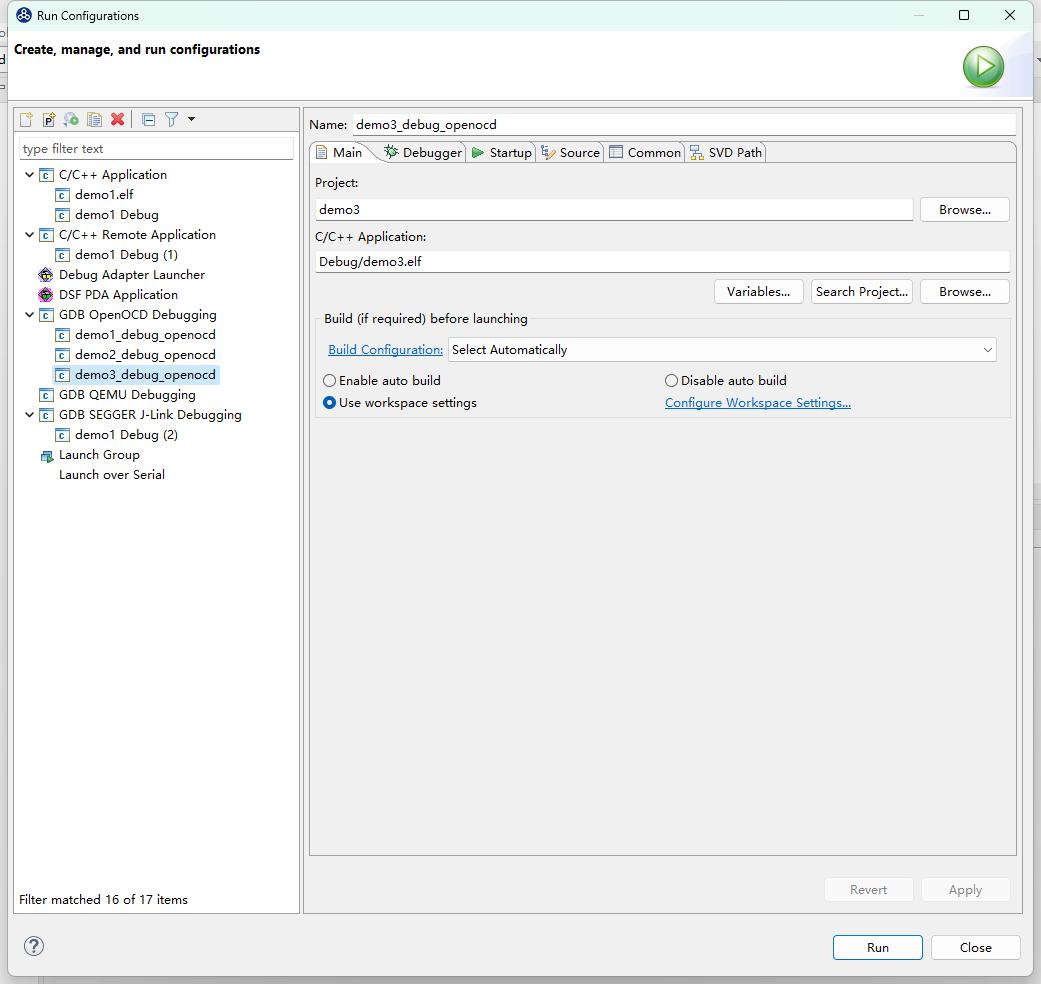

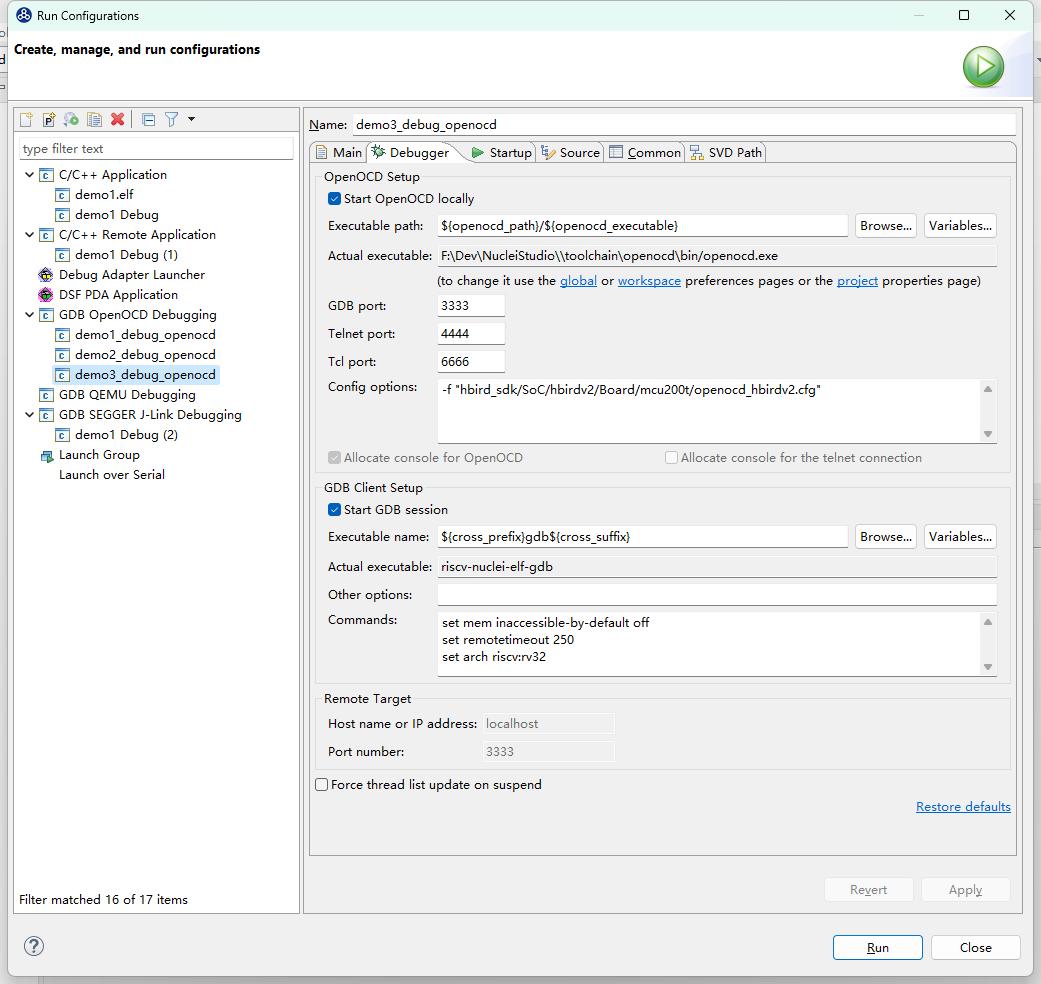

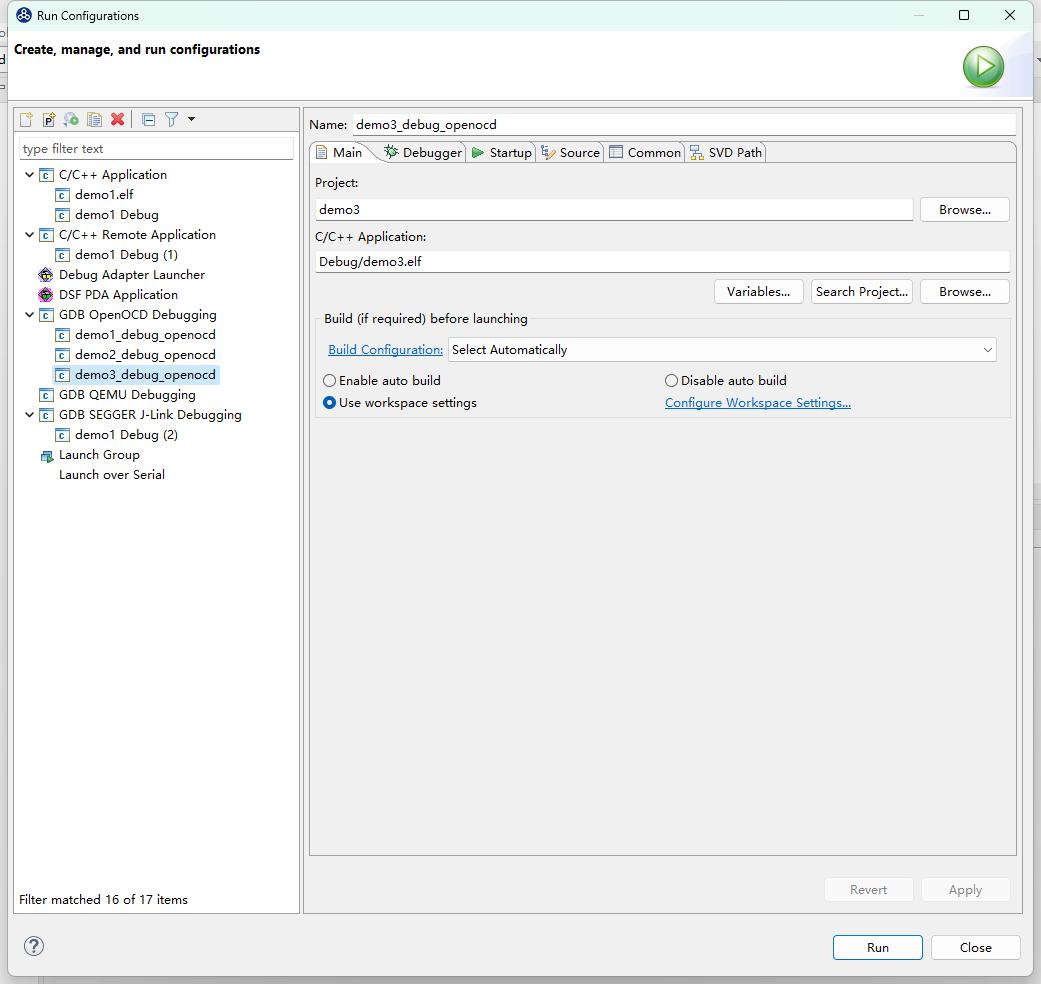

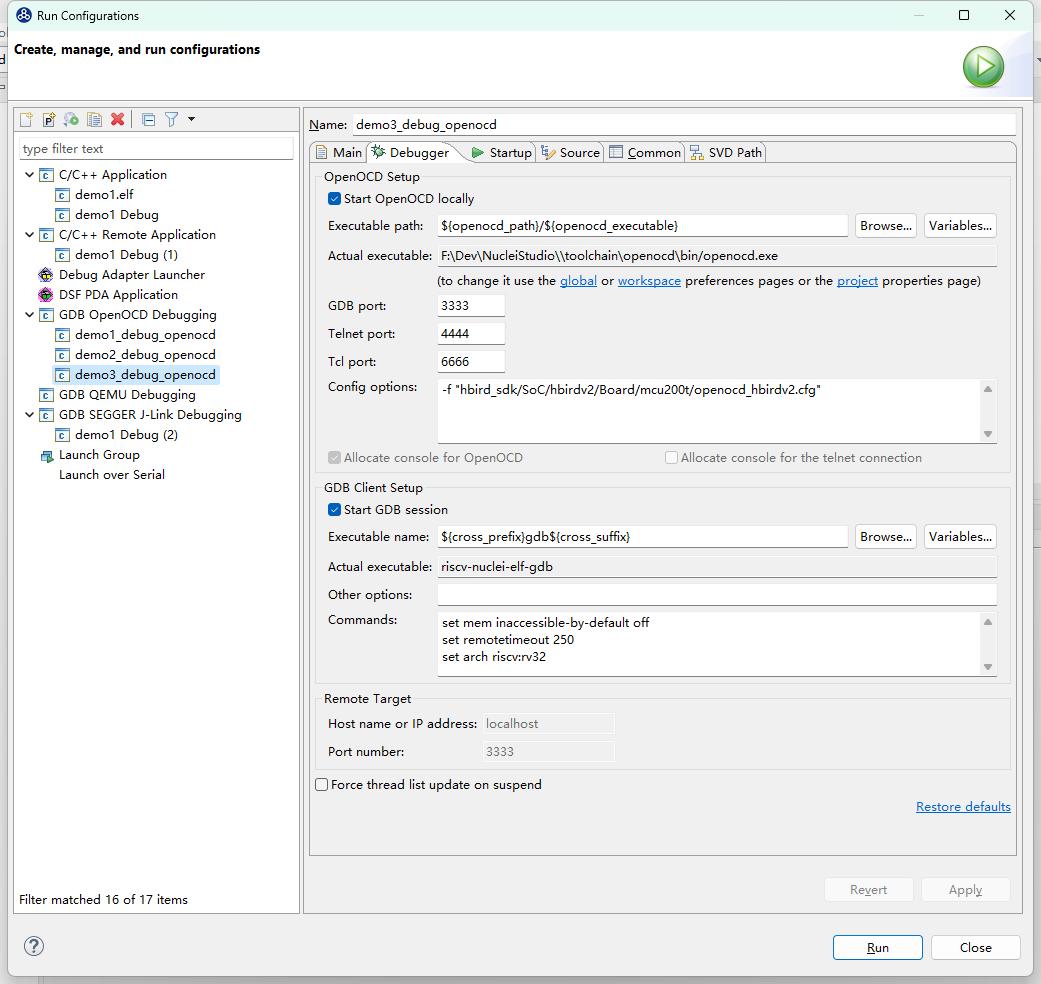

Run Configuration

openocd_hbirdv2.cfg

openocd_hbirdv2.cfg

cfg文件内注释掉了flash相关的三行代码

adapter_khz 1000interface ftdiftdi_vid_pid 0x0403 0x6010ftdi_oscan1_mode offtransport select jtagftdi_layout_init 0x0008 0x001bftdi_layout_signal nSRST -oe 0x0020 -data 0x0020ftdi_layout_signal TCK -data 0x0001ftdi_layout_signal TDI -data 0x0002ftdi_layout_signal TDO -input 0x0004ftdi_layout_signal TMS -data 0x0008ftdi_layout_signal JTAG_SEL -data 0x0100 -oe 0x0100set _CHIPNAME riscvjtag newtap $_CHIPNAME cpu -irlen 5set _TARGETNAME $_CHIPNAME.cputarget create $_TARGETNAME riscv -chain-position $_TARGETNAME$_TARGETNAME configure -work-area-phys 0x80000000 -work-area-size 10000 -work-area-backup 1# set _FLASHNAME $_CHIPNAME.flash# flash bank $_FLASHNAME fespi 0x20000000 0 0 0 $_TARGETNAME# Set the ILM space also as flash, to make sure it can be add breakpoint with hardware trigger#flash bank onboard_ilm fespi 0x80000000 0 0 0 $_TARGETNAME# Expose Nuclei self-defined CSRS range 770-800,835-850,1984-2032,2064-2070# See

https://github.com/riscv/riscv-gnu-toolchain/issues/319#issuecomment-358397306# Then user can view the csr register value in gdb using: info reg csr775 for CSR MTVT(0x307)riscv expose_csrs 770-800,835-850,1984-2032,2064-2070init#resetif {[ info exists pulse_srst]} { ftdi_set_signal nSRST 0 ftdi_set_signal nSRST z}halt# We must turn on this because otherwise the IDE version debug cannot download the program into flash# flash protect 0 0 last off

OpenOCD输出

Open On-Chip Debugger 0.11.0+dev-01897-gc8fc2a168 (2022-04-01-04:46)Licensed under GNU GPL v2For bug reports, read

http://openocd.org/doc/doxygen/bugs.htmlDEPRECATED! use 'adapter speed' not 'adapter_khz'DEPRECATED! use 'adapter driver' not 'interface'Info : Using libusb driverInfo : clock speed 1000 kHzError: JTAG scan chain interrogation failed: all onesError: Check JTAG interface, timings, target power, etc.Error: Trying to use configured scan chain anyway...Error: riscv.cpu: IR capture error; saw 0x1f not 0x01Warn : Bypassing JTAG setup events due to errorsError: Unsupported DTM version: 15Warn : target riscv.cpu examination failedInfo : starting gdb server for riscv.cpu on 3333Info : Listening on port 3333 for gdb connectionsError: Target not examined yetError: Unsupported DTM version: 15

驱动安装情况

按照

https://www.rvmcu.com/community-topic-id-464.html 安装了驱动

约束文件

约束文件

顶层文件中将TDO从inout改成了output

#=========================== Sys Clock & rstn ================================## Clock Signal 50Mset_property -dict { PACKAGE_PIN U18 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #U18create_clock -add -name sys_clk_pin -period 20.00 -waveform {0 10} [get_ports clk]## mcu Rst_nset_property -dict { PACKAGE_PIN N15 IOSTANDARD LVCMOS33 } [get_ports { mcu_rst }]; #PL_KEY1 N15set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports {rst_led }]; #PL LED1#----------------------------------------------------------------------------#=========================== Debug JTAG ======================================set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets IOBUF_jtag_TCK/O]set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets dut_io_

pads_jtag_TCK_i_ival]# mcu_TCK# mcu_TDO# mcu_TMS# rst# mcu_TDI# JTAG Debug Portset_property -dict { PACKAGE_PIN W15 IOSTANDARD LVCMOS33 } [get_ports { mcu_TCK }]; #J10-9set_property -dict { PACKAGE_PIN V15 IOSTANDARD LVCMOS33 } [get_ports { mcu_TDO }]; #J10-10set_property -dict { PACKAGE_PIN Y14 IOSTANDARD LVCMOS33 } [get_ports { mcu_TMS }]; #J10-11set_property -dict { PACKAGE_PIN W14 IOSTANDARD LVCMOS33 } [get_ports { mcu_TDI }]; #J10-12#------------------------ End of Debug JTAG ----------------------------------#=============================== UART 0 ======================================set_property -dict { PACKAGE_PIN P18 IOSTANDARD LVCMOS33 } [get_ports { uart0_tx }]; #J10-13set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports { uart0_rx }]; #J10-14#---------------------------- End of UART 0 --------------------------------#LED1 #LED2 #LED3 #LED4 #PL_KEY1 #PL_KEY2 ## GPIOA#LEDs# set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports { gpioA_0 }]; # M14set_property -dict { PACKAGE_PIN M15 IOSTANDARD LVCMOS33 } [get_ports { gpioA_1 }]; # M15set_property -dict { PACKAGE_PIN K16 IOSTANDARD LVCMOS33 } [get_ports { gpioA_2 }]; # K16set_property -dict { PACKAGE_PIN J16 IOSTANDARD LVCMOS33 } [get_ports { gpioA_3 }]; # J16#KEYset_property -dict { PACKAGE_PIN N16 IOSTANDARD LVCMOS33 } [get_ports { gpioA_4 }]; # N16 PL_KEY2# USERIOset_property -dict { PACKAGE_PIN F17 IOSTANDARD LVCMOS33 } [get_ports { gpioA_5 }]; # J11-3set_property -dict { PACKAGE_PIN F16 IOSTANDARD LVCMOS33 } [get_ports { gpioA_6 }]; # J11-4set_property -dict { PACKAGE_PIN F20 IOSTANDARD LVCMOS33 } [get_ports { gpioA_7 }]; # J11-5set_property KEEPER true [get_ports mcu_TMS]