本帖最后由 Tronlong创龙科技 于 2024-7-19 17:09 编辑

1 cameralink_display案例 4

1.1 案例功能 4

1.2 操作说明 4

1.3 关键代码(MicroBlaze) 11

1.4 Vivado工程说明 16

1.5 模块/IP核配置 20

前 言 本文主要介绍

FPGA视频开发案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。

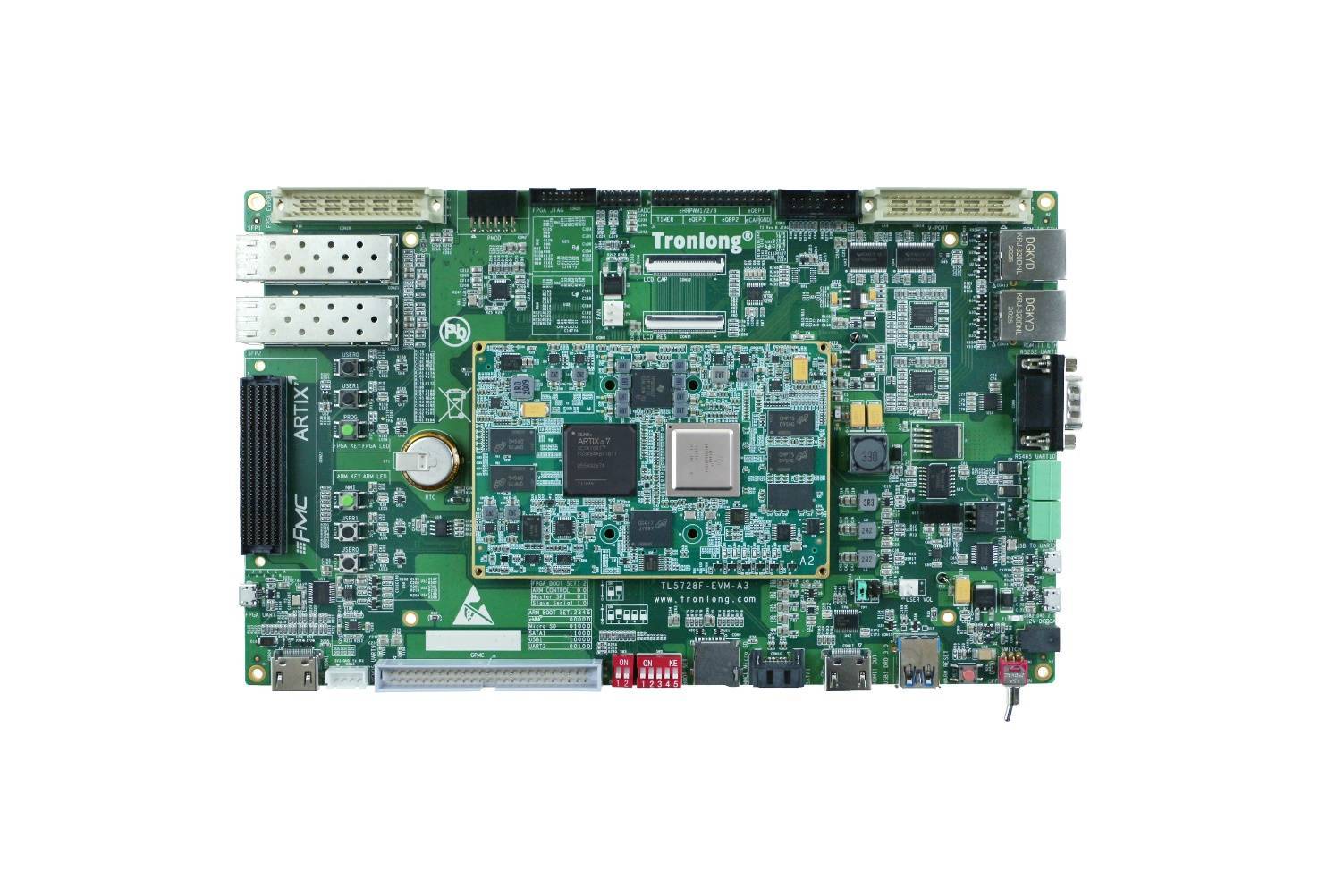

评估板简介 创龙科技TL5728F-EVM是一款基于

ti Sitara系列AM5728(双核ARM Cortex-A15 +浮点双核DSP C66x) + Xilinx Artix-7 FPGA处理器设计的高端异构多核评估板,由核心板与评估底板组成。AM5728与Artix-7在核心板内部通过GPMC、I2C

通信总线连接,在评估底板通过PCIe通信总线连接。核心板经过专业的

PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。评估板接口资源丰富,引出双路千兆网口、双路SFP光口、USB 3.0、CAN、RS485、SATA、HDMI、GPMC、FMC等接口,方便用户快速进行产品方案评估与技术预研。

编辑

在进行本文如下操作前,请先按照调试工具安装文档安装Xilinx Vivado开发工具包。本文默认使用创龙科技的TL-DLC10下载器进行操作演示。

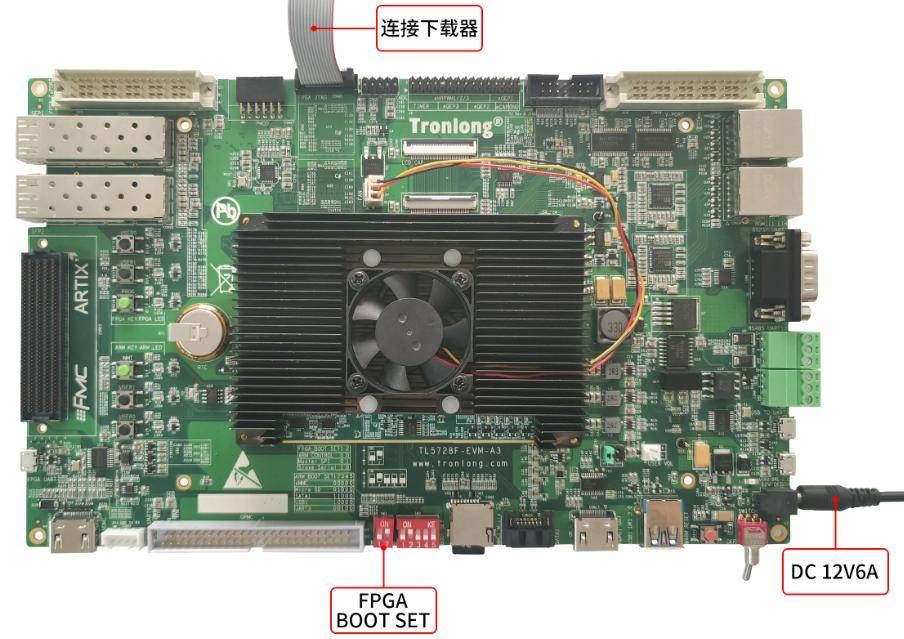

根据评估底板丝印将Artix-7的BOOT SET拨码开关(SW3)拨至01(1~2),此档位为SPI FLASH启动模式(此模式可进行程序在线加载、固化并离线启动),并将评估板通过下载器正常连接至PC机。

编辑

图 1

cameralink_display案例 cameralink_display案例分为FPGA程序与MicroBlaze裸机程序两部分。FPGA程序位于产品资料“4-软件资料DemoFPGA_DemoAll-Programmable-FPGA-demoscameralink_displayhw”目录下,包含project和bin两个目录。基于MicroBlaze软核的裸机程序位于产品资料“4-软件资料DemoAll-Programmable-FPGA-demoscameralink_displayswbaremetal_demo”目录下,包含project和bin两个目录。

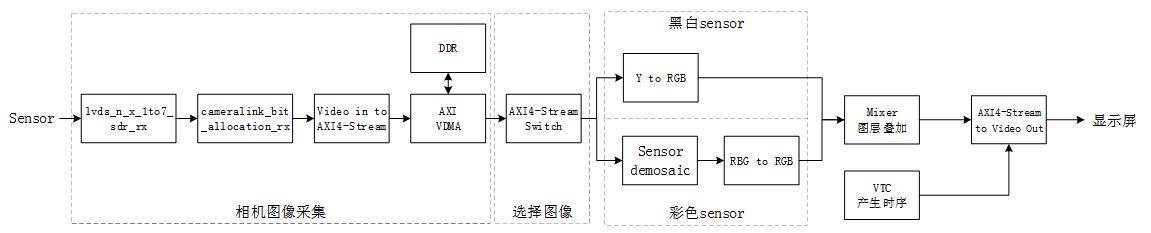

案例功能 案例功能:评估板通过FMC视频模块TLCameraLinkF的CameraLink接口采集分辨率为1280 x 1024的视频,并通过TLCameraLinkF模块的HDMI OUT接口输出采集到的视频。

编辑

图 2 程序功能框图

本案例FPGA程序支持CameraLink Full模式(工程为cameralink_display_full_xx)与CameraLink Base模式(工程为cameralink_display_base_xx)。

Full模式工程编译后生成的可执行文件为cameralink_display_full_xx.bit,Base模式工程编译后生成的可执行文件为cameralink_display_base_xx.bit。

操作说明 本案例支持三款CameraLink相机,具体说明如下。

厂家

相机型号

支持模式

相机性能

Microview

(北京微视)

RS-A5241-CM107-S00

(黑白CameraLink相机)

Full

全幅面2560*2048下,帧率可达107fps

Base

RS-A5241-CC107-S00

(彩色CameraLink相机)

Full

全幅面2560*2048下,帧率可达107fps

Base

MVC1381SAM-CL60-S00

(黑白CameraLink相机)

Base

全幅面1280*1024下,帧率可达60fps

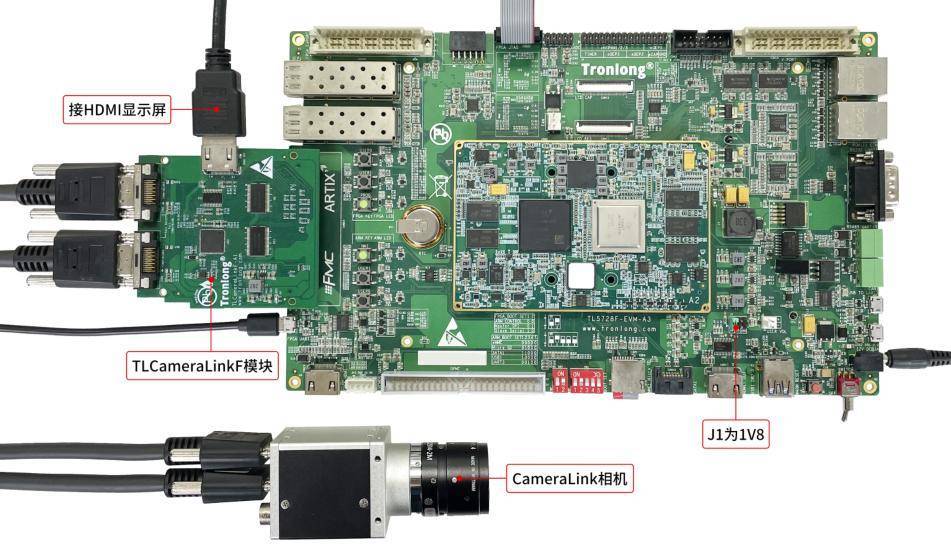

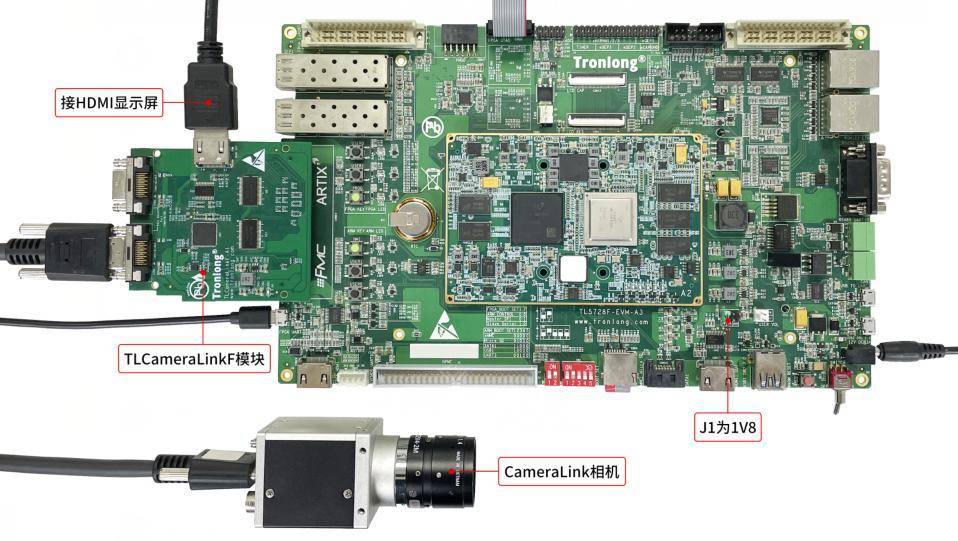

Full模式硬件连接方法

如采用Full模式,请将创龙科技的TLCameraLinkF模块连接至评估板FMC接口,评估板J1跳线帽选择1.8V档位,以配置FMC IO的BANK电压为1.8V。

请将CameraLink相机的CL0通过数据线连接至TLCameraLinkF模块的CameraLink1接口,将CameraLink相机的CL1通过数据线连接至TLCameraLinkF模块的CameraLink2接口,将HDMI显示屏通过数据线连接至TLCameraLinkF模块的HDMI OUT接口。

编辑

图 3

Base模式硬件连接方法

如采用Base模式,请将创龙科技的TLCameraLinkF模块连接至评估板FMC接口,评估板J1跳线帽选择1.8V档位,以配置FMC IO的BANK电压为1.8V。

请将CameraLink相机的CL0通过数据线连接至TLCameraLinkF模块的CameraLink1接口,将HDMI显示屏通过数据线连接至TLCameraLinkF模块的HDMI OUT接口。

编辑

图 4

下面对三款不同型号的CameraLink相机在Full/Base模式下的操作步骤进行说明。

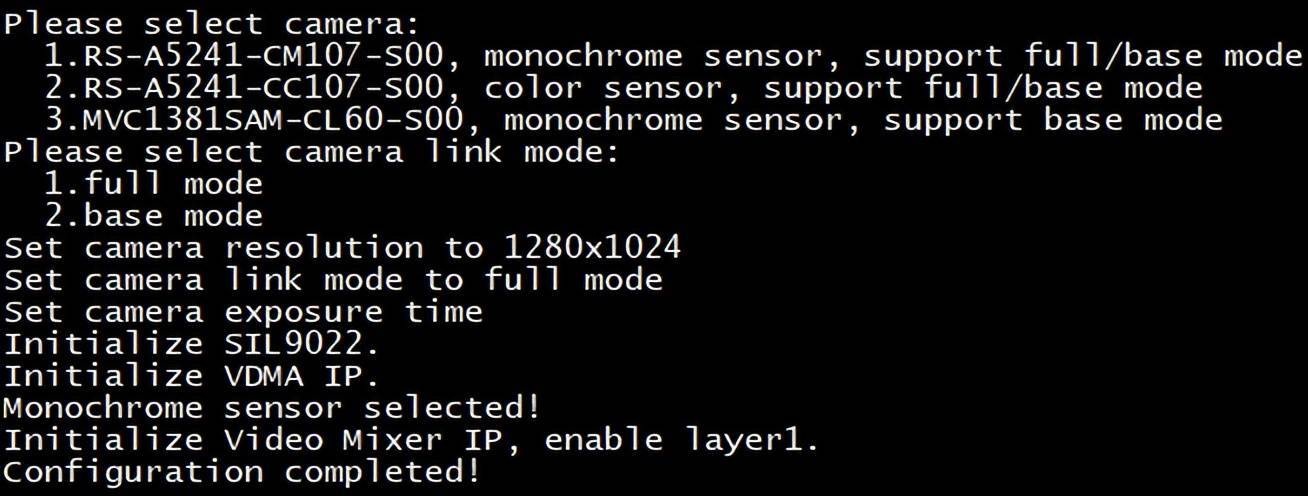

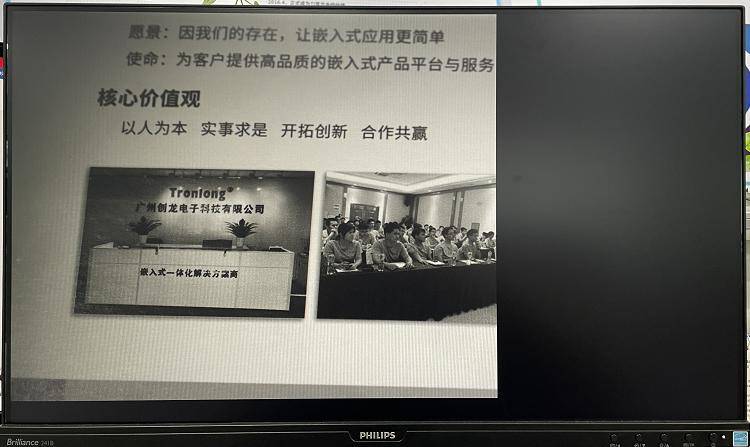

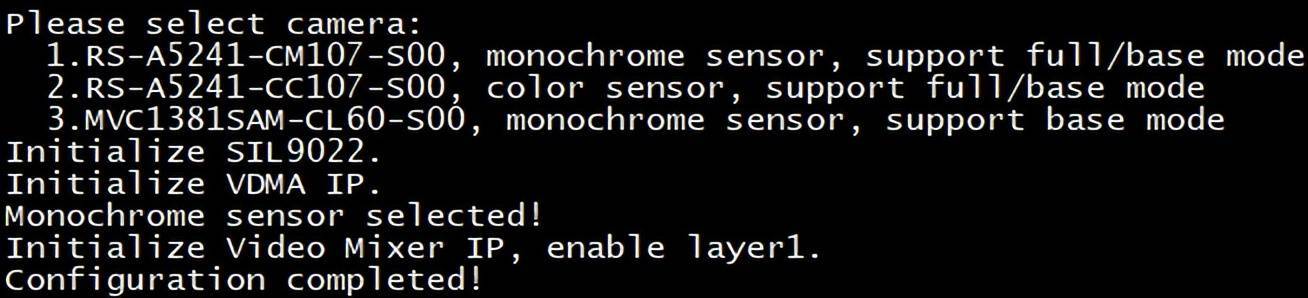

- 黑白CameraLink相机RS-A5241-CM107-S00,Full模式

请运行Full模式程序,即可看到串口调试终端打印如下信息。请先输入"1"选择相机型号为RS-A5241-CM107-S00,再输入"1"选择为Full模式。配置完成后,即可看到HDMI显示屏输出黑白图像。

编辑

图 5

编辑

图 6

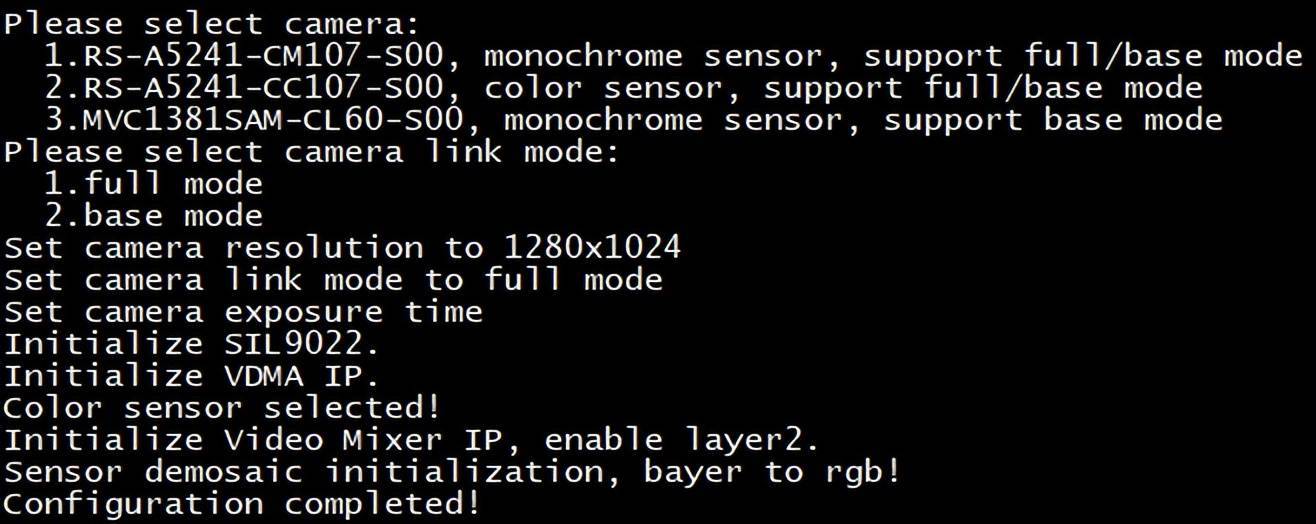

- 彩色CameraLink相机RS-A5241-CC107-S00,Full模式

请运行Full模式程序,即可看到串口调试终端打印如下信息。请先输入"2"选择相机型号为RS-A5241-CC107-S00,再输入"1"选择为Full模式。配置完成后,即可看到HDMI显示屏输出彩色图像。

编辑

图 7

编辑

图 8

备注:由于彩色CameraLink相机RS-A5241-CC107-S00无白平衡功能,故图像颜色偏绿。

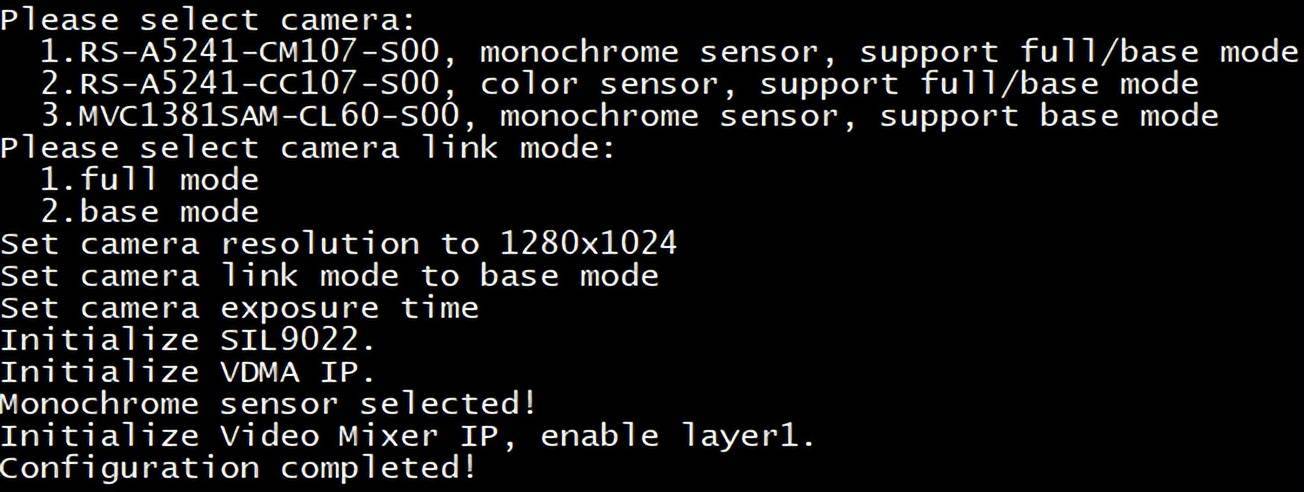

- 黑白CameraLink相机RS-A5241-CM107-S00,Base模式

请运行Base模式程序,即可看到串口调试终端打印如下信息。请先输入"1"选择相机型号为RS-A5241-CM107-S00,再输入"2"选择为Base模式。配置完成后,即可看到HDMI显示屏输出黑白图像。

编辑

图 9

编辑

图 10

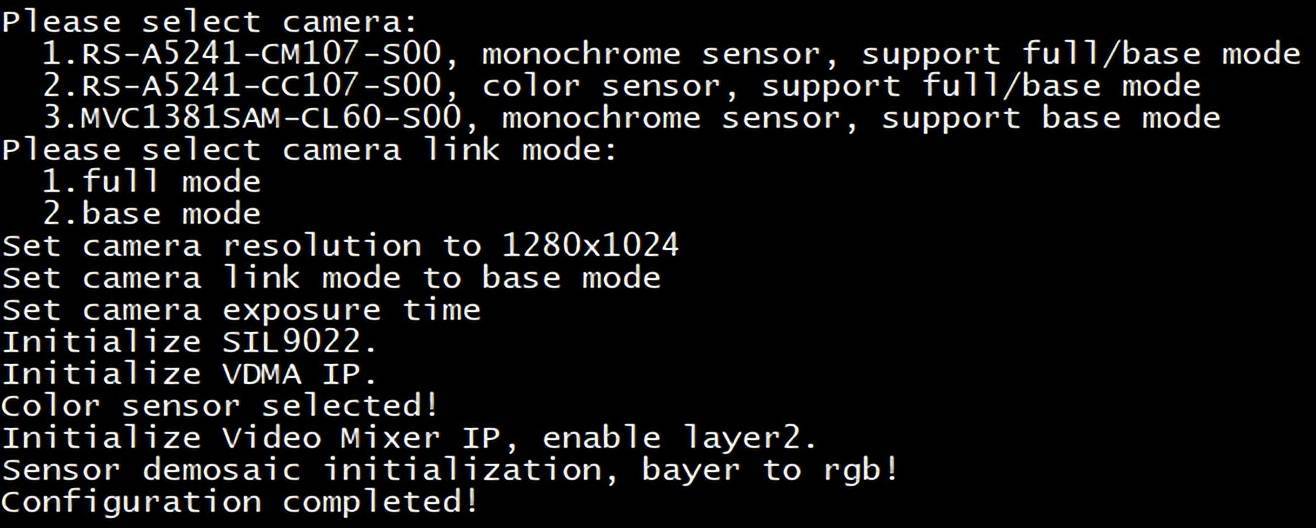

- CameraLink相机RS-A5241-CC107-S00,Base模式

请运行Base模式程序,即可看到串口调试终端打印如下信息。请先输入"2"选择相机型号为RS-A5241-CC107-S00,再输入"2"选择为Base模式。配置完成后,即可看到HDMI显示屏输出彩色图像。

编辑

图 11

编辑

图 12

备注:由于彩色CameraLink相机RS-A5241-CC107-S00无白平衡功能,故图像颜色偏绿。

- 黑白CameraLink相机MVC1381SAM-CL60-S00,Base模式

请运行Base模式程序,即可看到串口调试终端打印如下信息。请输入"3"选择相机型号为MVC1381SAM-CL60-S00。配置完成后,即可看到HDMI显示屏输出黑白图像。

编辑

图 13

编辑

图 14

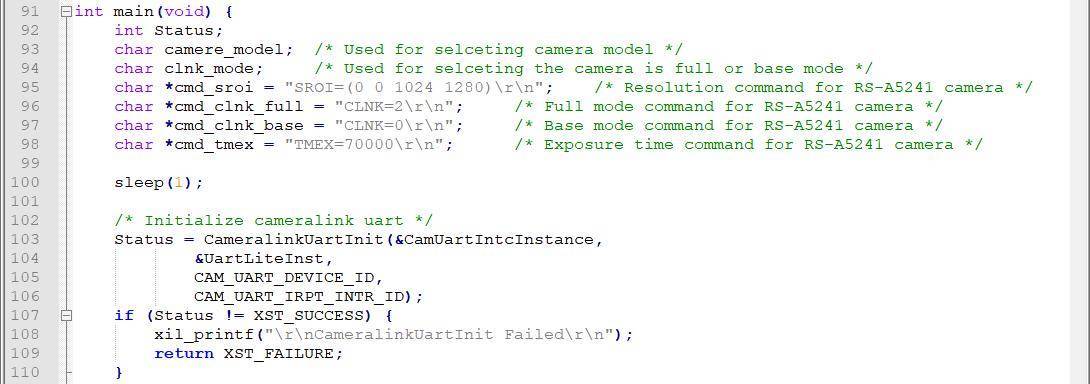

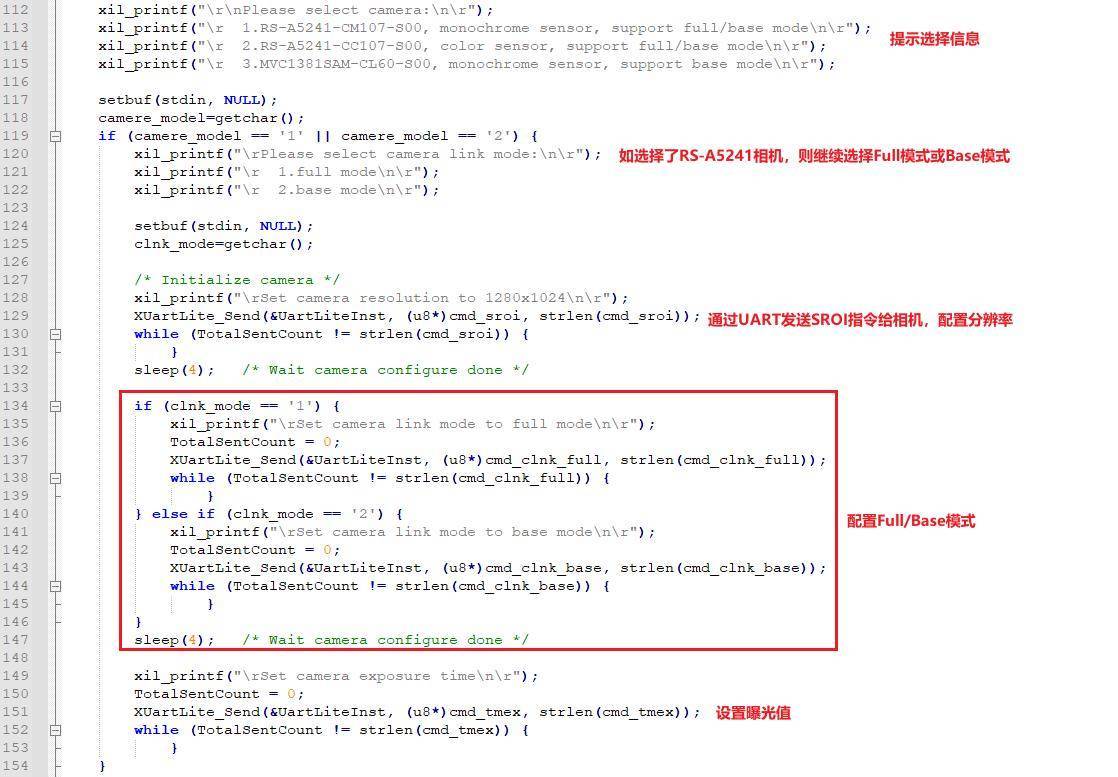

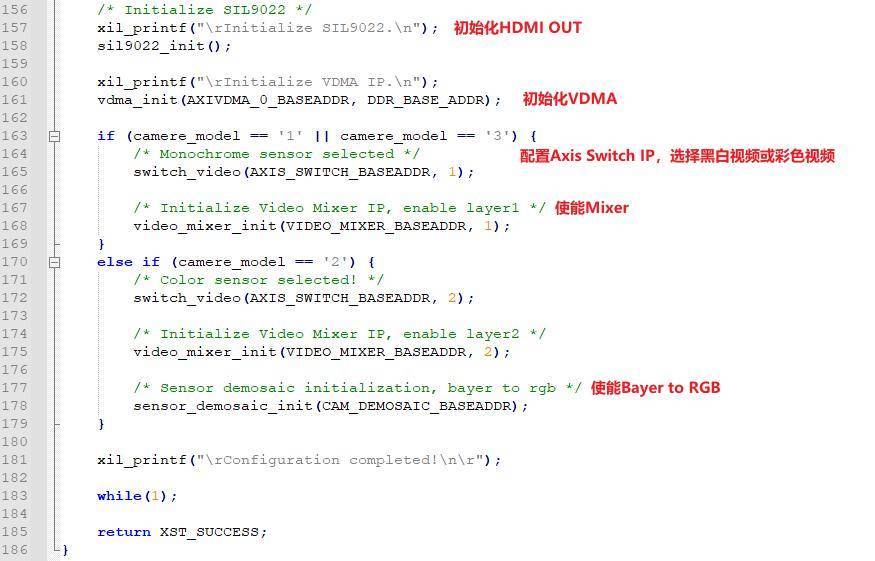

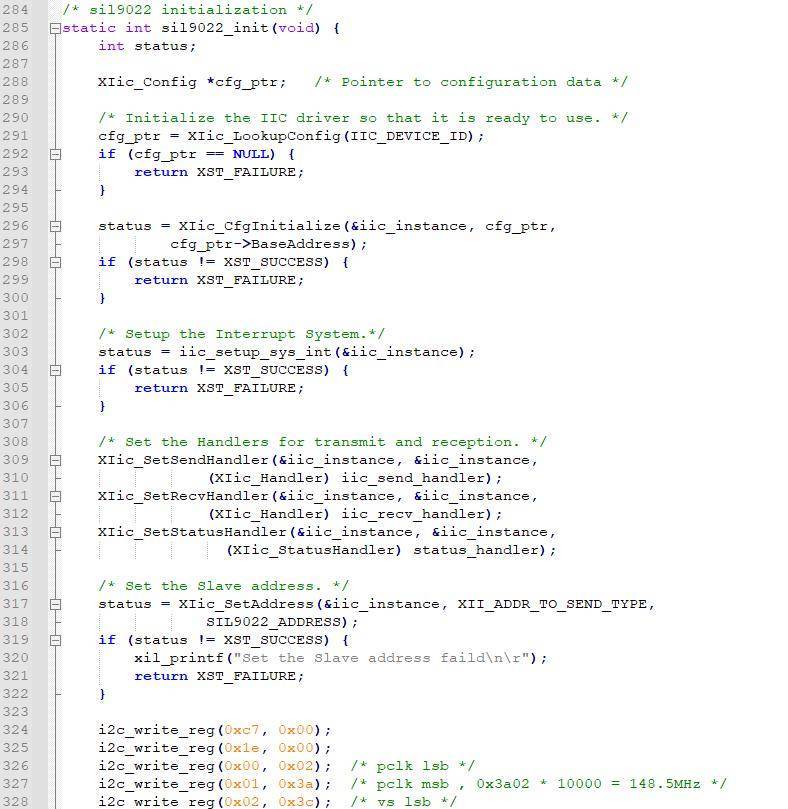

关键代码(MicroBlaze) MicroBlaze裸机源码为"swbaremetal_demoprojectcameralink_displaysrc",关键代码说明如下。

编辑

图 15

编辑

图 16

编辑

图 17

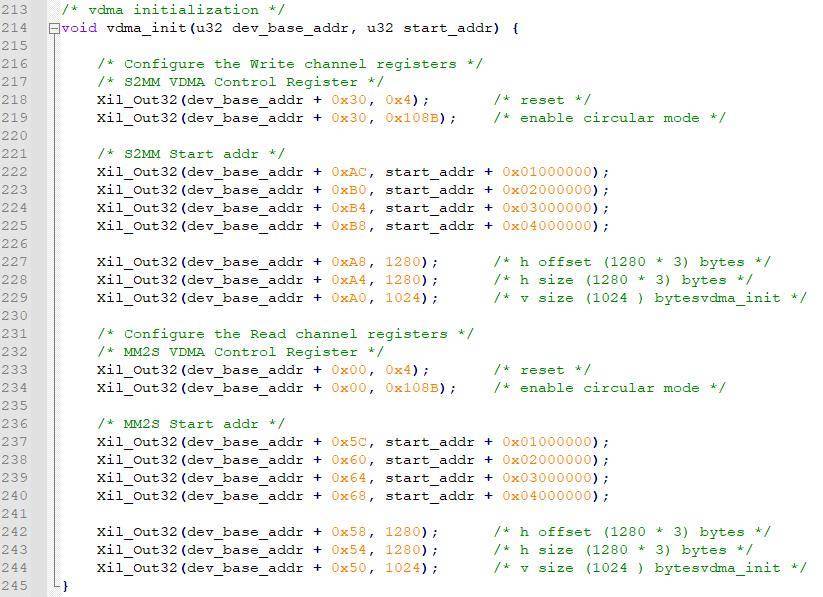

- 初始化VDMA,将采集到的视频数据缓存至DDR,再进行HDMI视频输出。

编辑

图 18

编辑

图 19

编辑

图 20

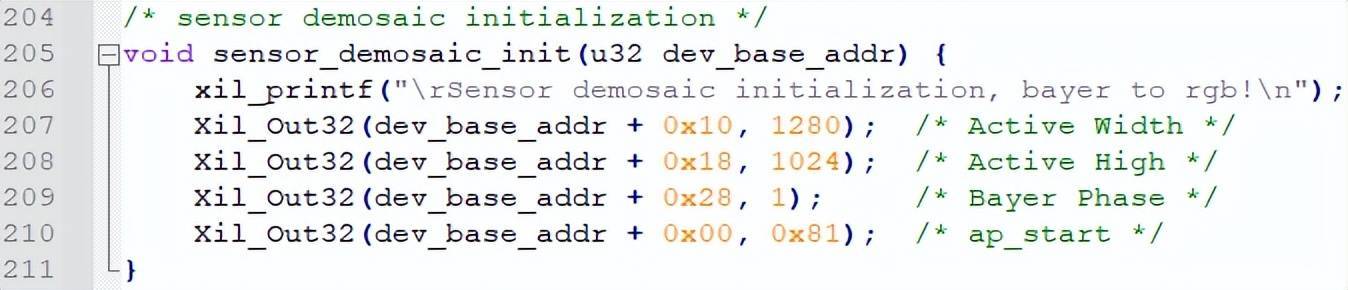

- 初始化Sensor Demosaic IP核,以将彩色CameraLink相机的Bayer格式视频数据转化为RGB格式。

编辑

图 21

编辑

图 22

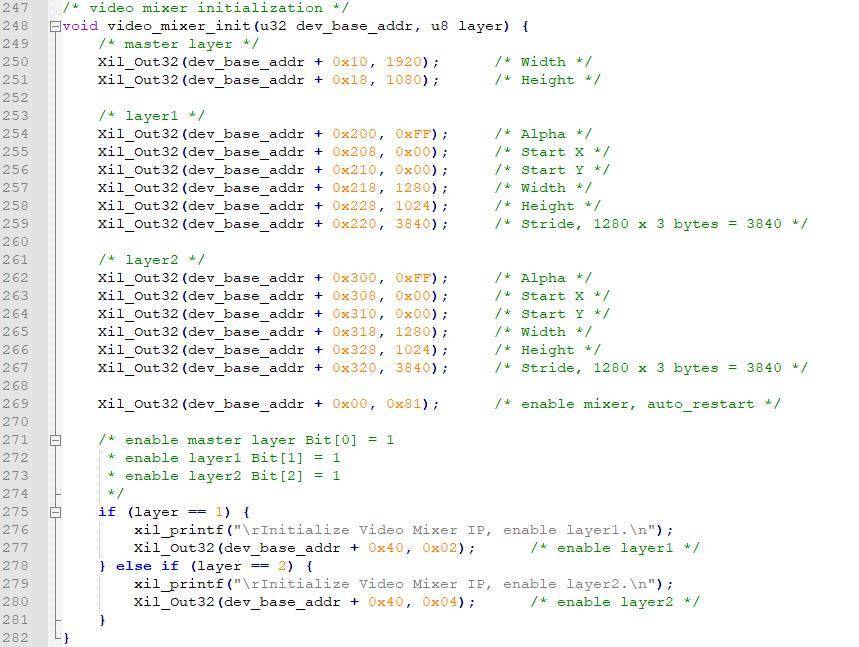

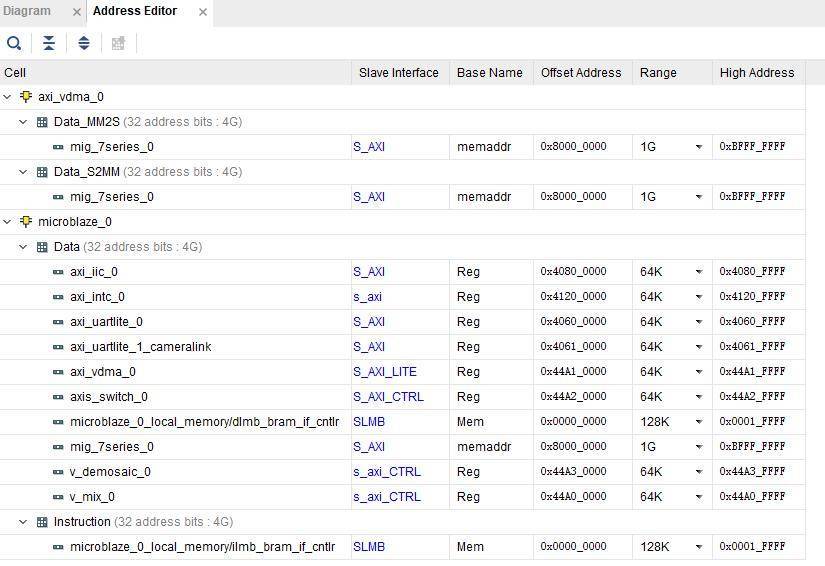

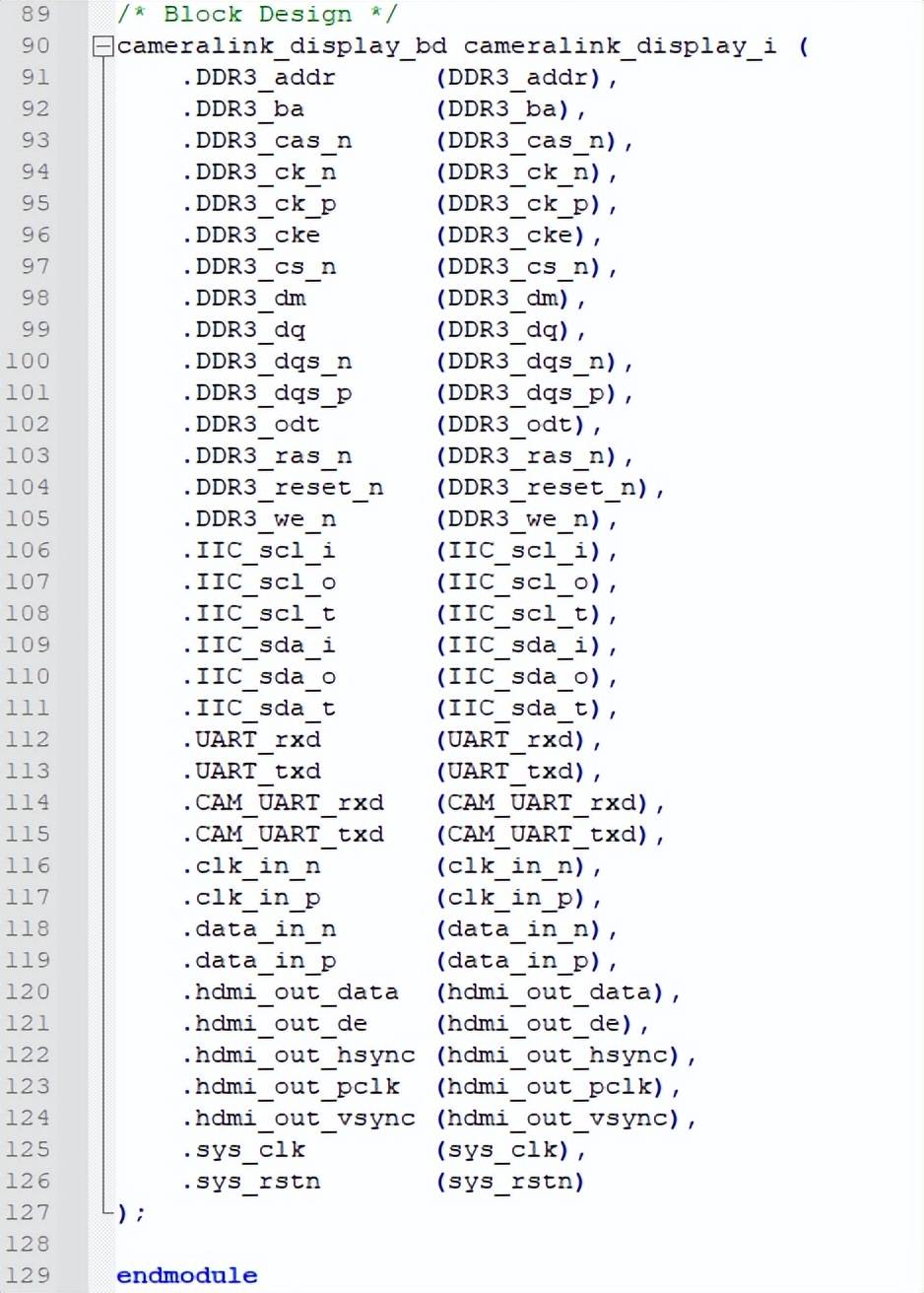

Vivado工程说明 点击BLOCK DESIGN开发界面下的"Address Editor"选项,可查看IP核分配的地址,MicroBlaze可通过对应地址对IP核进行控制。

编辑

图 23

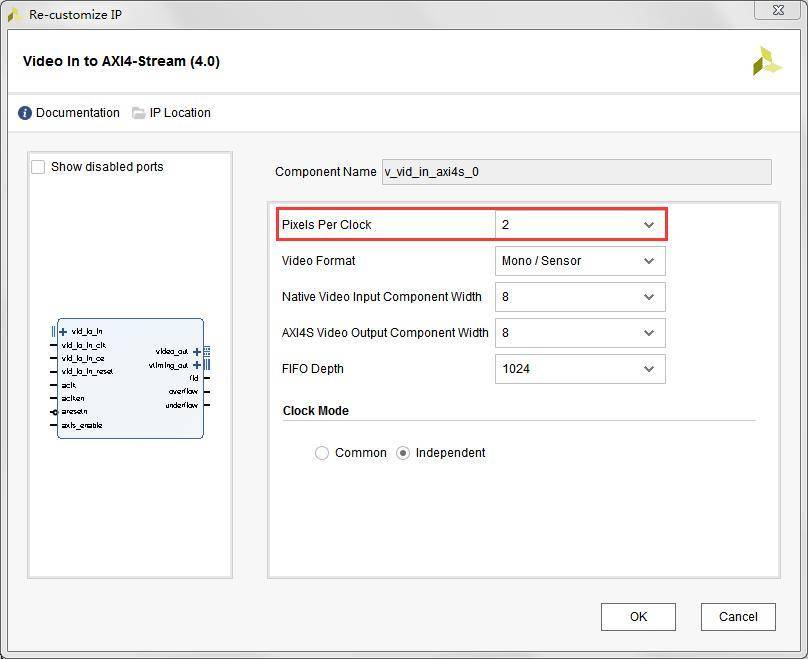

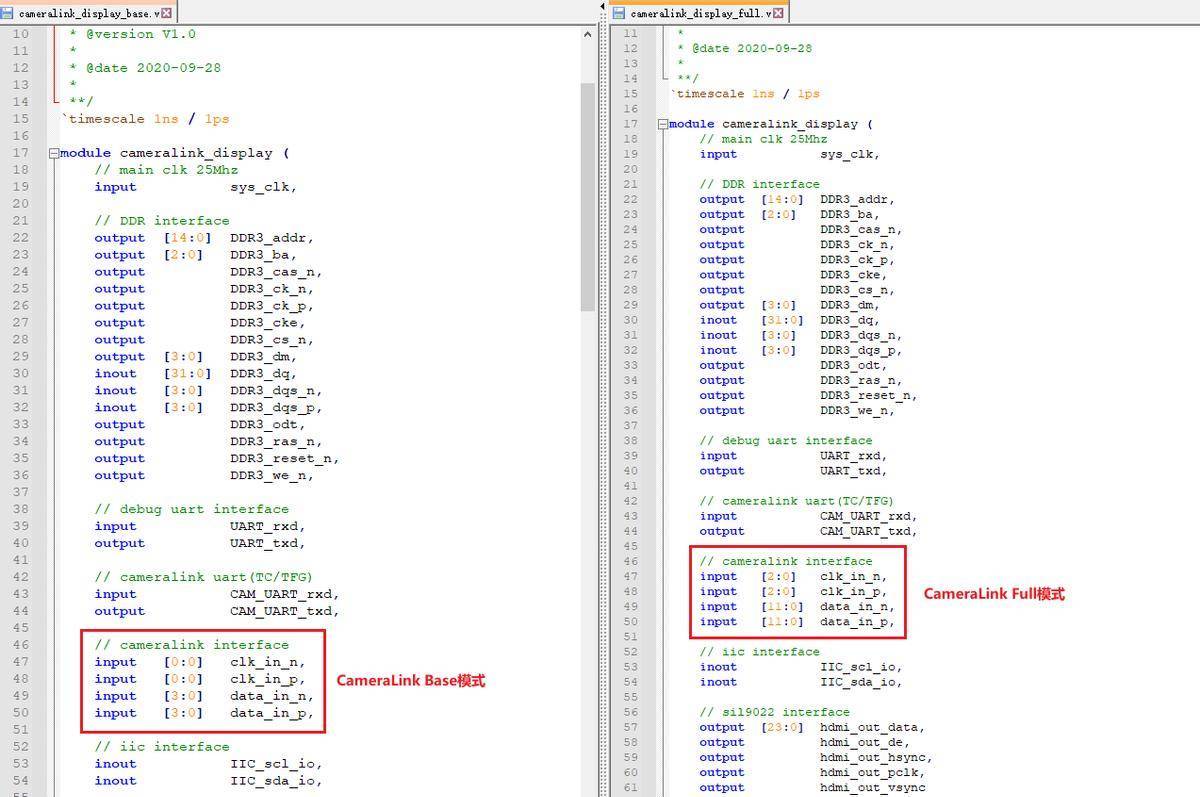

本案例分别支持CameraLink Full模式(工程为cameralink_display_full_xx)与CameraLink Base模式(工程为cameralink_display_base_xx)。两者区别如下:

- Full模式Vivado工程:Pixels Per Clock配置为8,即每个时钟8个像素。

- Base模式Vivado工程:Pixels Per Clock配置为2,即每个时钟2个像素。

编辑

图 24 Full模式

编辑

图 25 Base模式

CameraLink Full模式Vivado工程顶层文件为"hwprojectcameralink_display_full_xxcameralink_display.srcssources_1importshdlcameralink_display_full.v"。

CameraLink Base模式Vivado工程顶层文件为"hwprojectcameralink_display_base_xxcameralink_display.srcssources_1importshdlcameralink_display_base.v"。

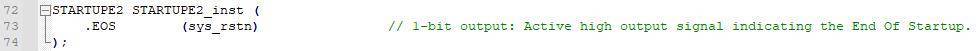

关键代码说明如下。

编辑

图 26

编辑

图 27

编辑

图 28

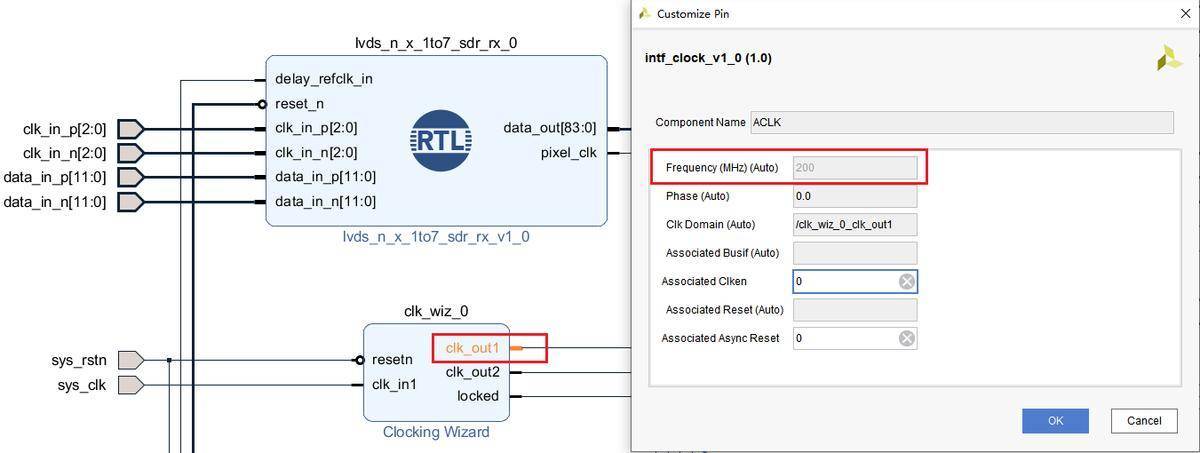

模块/IP核配置 lvds_n_x_1to7_sdr_rx模块 本案例使用lvds_n_x_1to7_sdr_rx模块将CameraLink相机输入的差分视频数据转化成并行视频数据。

lvds_n_x_1to7_sdr_rx模块开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《xapp585-lvds-source-synch-serdes-clock-multiplication.pdf》。lvds_n_x_1to7_sdr_rx模块源码文件为Vivado工程"cameralink_display.srcssources_1importshdllvds_n_x_1to7_sdr_rx.v",具体配置说明如下。

- delay_refclk_in接入由Clocking Wizard输出的200MHz参考时钟。

编辑

图 29

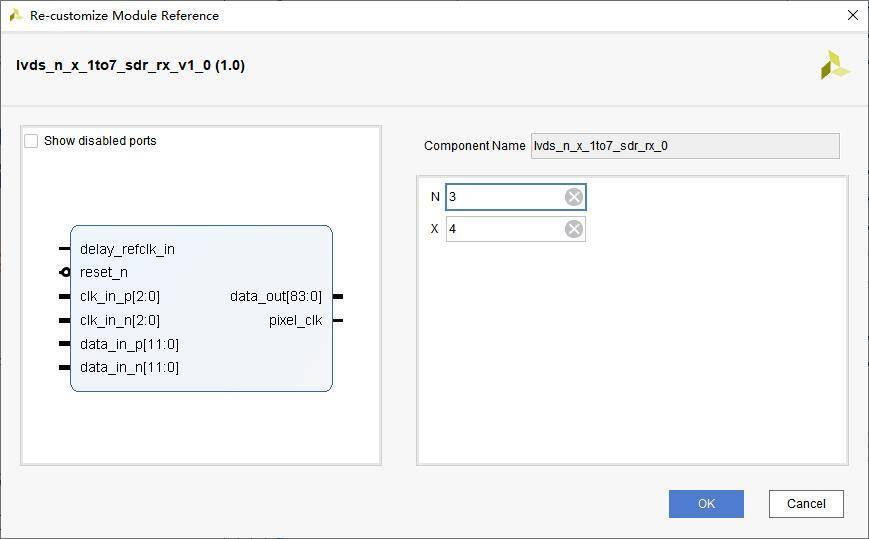

- 配置N(通道数量)为3对应Full模式,配置N为1则对应Base模式。配置X为4,表示“每个通道的数据差分对数量为4”。

- Base模式:单通道,每通道数据差分对为4组,需1个连接器。

- Medium模式:双通道,每通道数据差分对为4组,需2个连接器。

- Full模式:三通道,每通道数据差分对为4组,需2个连接器。

编辑

图 30

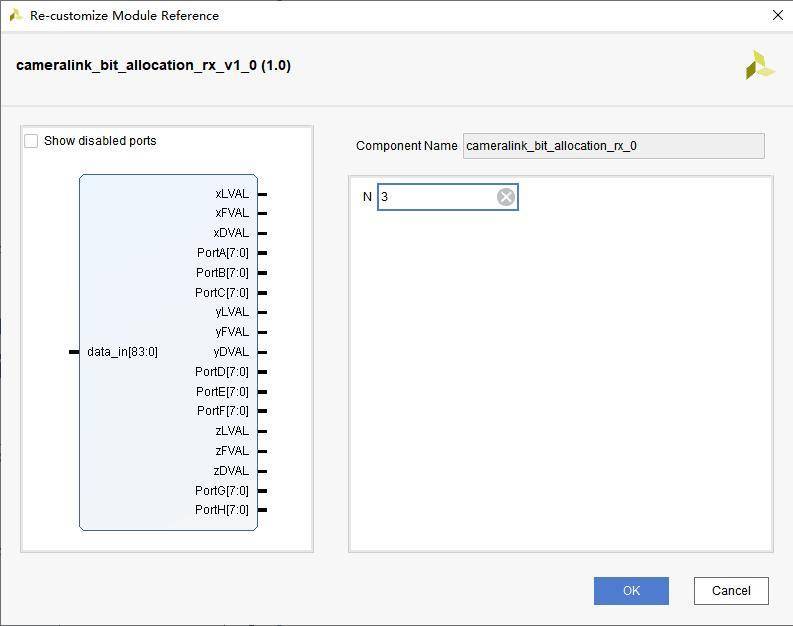

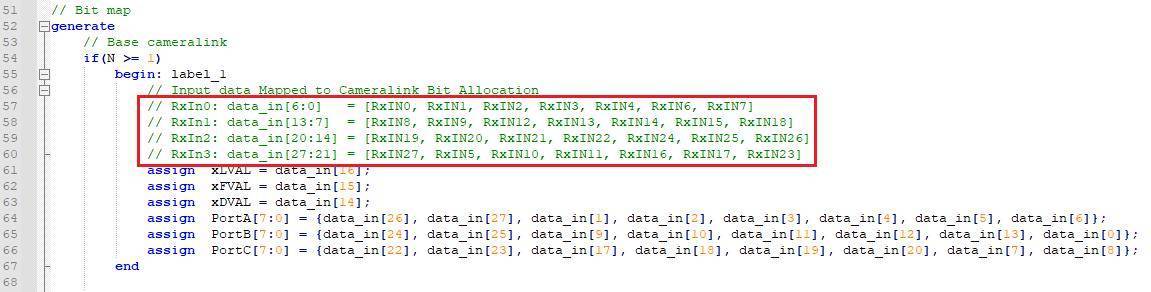

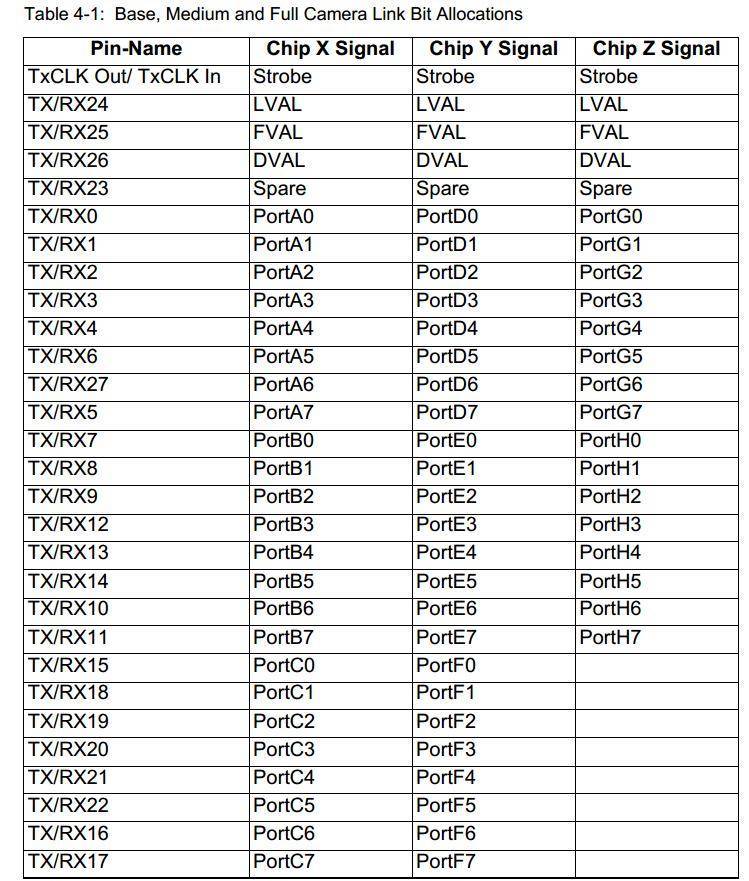

cameralink_bit_allocation_rx模块 本案例使用cameralink_bit_allocation_rx模块将转化后的并行视频数据进行重组,分离出行同步信号、场同步型号、数据有效信号和像素数据。

cameralink_bit_allocation_rx模块源码为Vivado工程"cameralink_display.srcssources_1importshdlcameralink_bit_allocation_rx.v",具体配置与关键代码说明如下。

- 配置N(通道数量)为3对应Full模式,配置N为1则对应Base模式。

- Base模式:单通道,输出端PortA、PortB、PortC有效。

- Medium模式:双通道,输出端PortA、PortB、PortC、PortD、PortE、PortF有效。

- Full模式:三通道,输出端PortA、PortB、PortC、PortD、PortE、PortF、PortG、PortH有效。

编辑

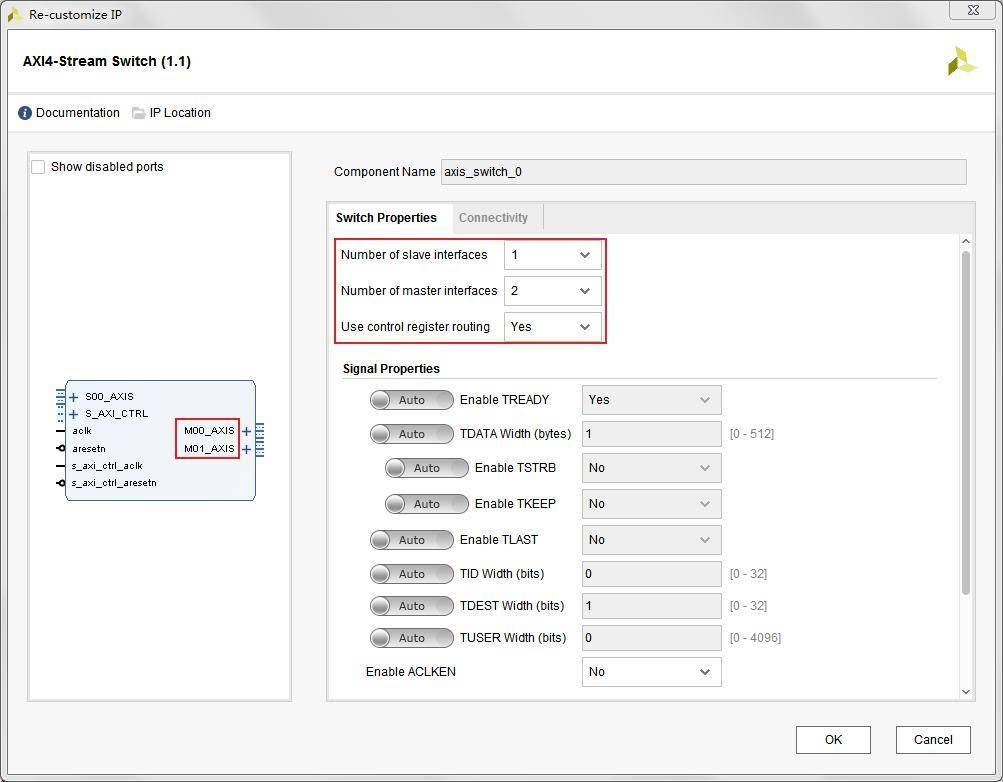

图 31

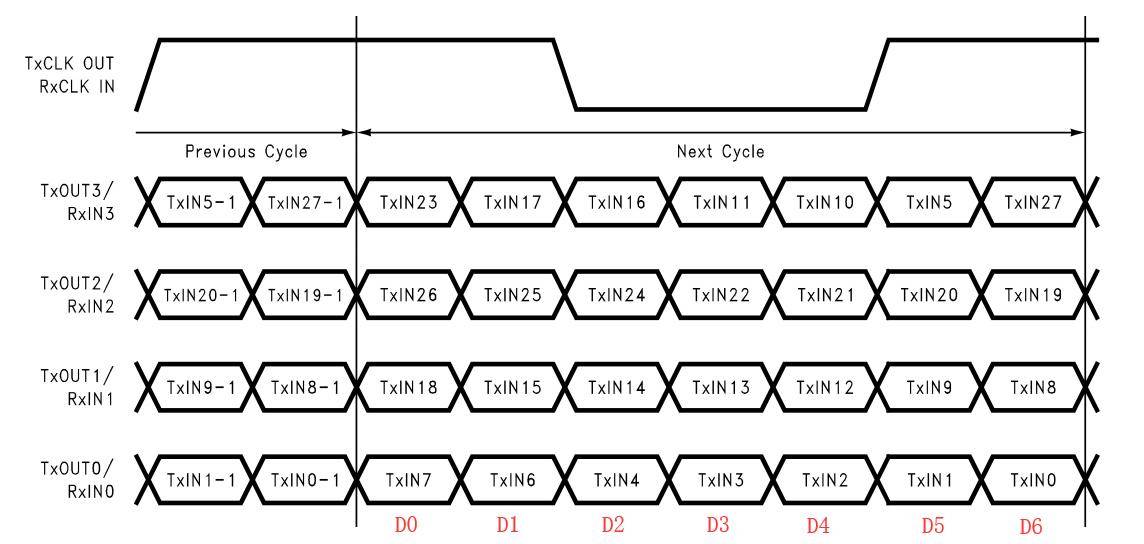

下图为Base模式单通道4组差分对图像数据排列,例如TxIN[7:6]对应D[0:1],TxIN[4:0]对应D[2:6]。

编辑

图 32

将Base模式单通道4组差分对图像数据保存在data_in数组的排列顺序如下。

编辑

图 33

- 分离行同步信号、场同步信号、数据有效信号和像素数据。

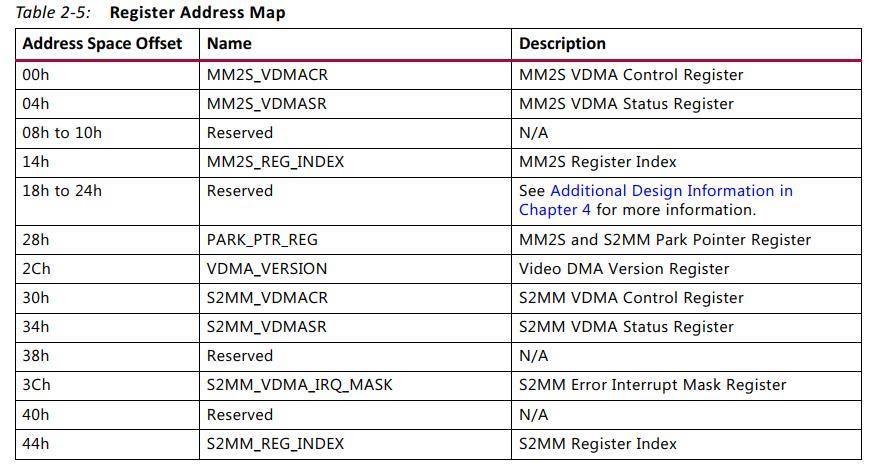

根据CameraLink V2.0协议,RX24对应行有效信号LVAL(行同步信号),RX25对应帧有效信号FVAL(场同步信号),RX26对应数据有效信号DVAL,具体对应关系如下。

编辑

图 34

根据上图说明,即可将行同步信号、场同步型号、数据有效信号和像素数据进行分离。

编辑

图 35

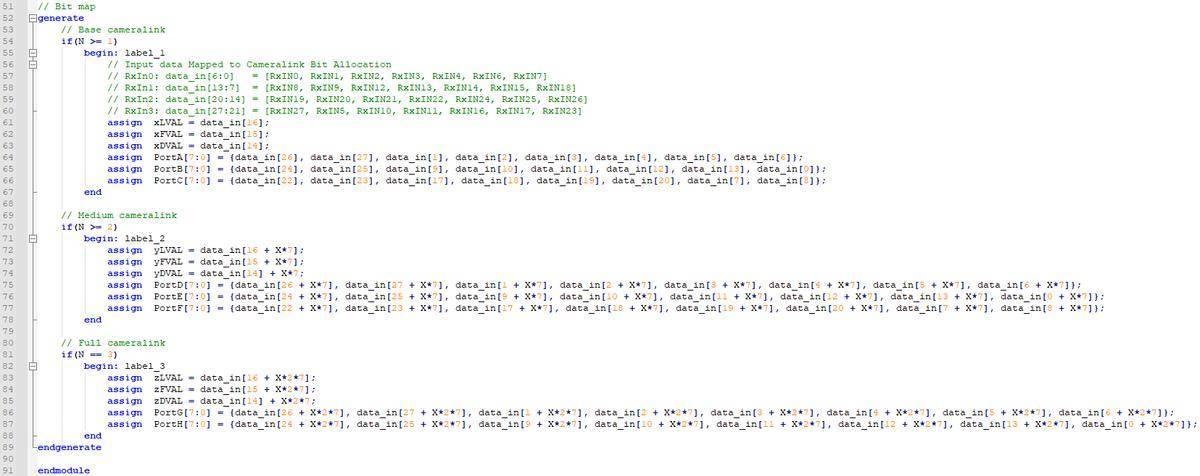

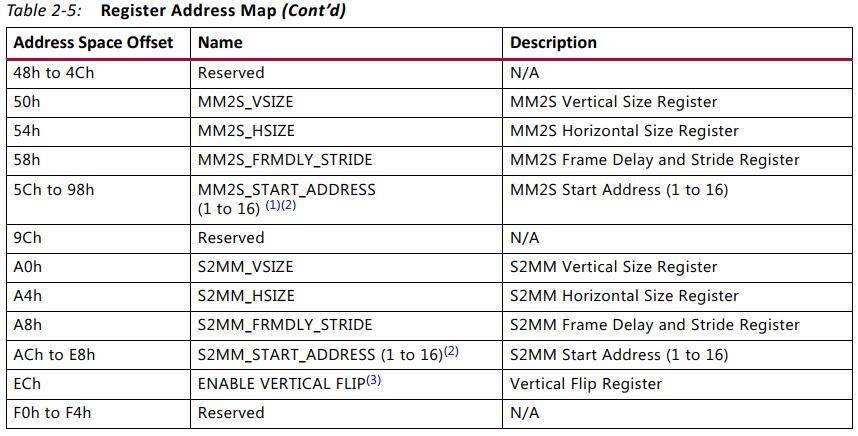

VDMA IP核 本案例使用VDMA IP核进行视频数据缓存。

VDMA(AXI Video Direct Memory Access) IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg020_axi_vdma.pdf》。

VDMA IP核寄存器列表如下,其中S2MM_xx将视频数据缓存至DDR,MM2S_xx将视频数据从DDR中取出。

编辑

图 36

编辑

图 37

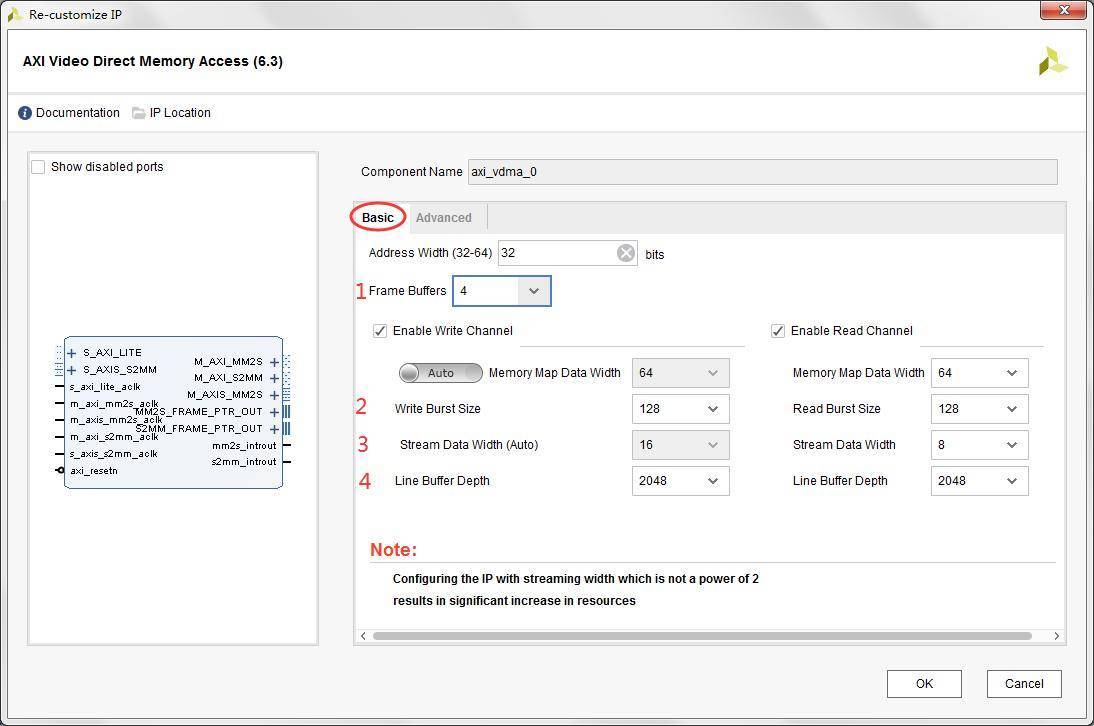

VDMA IP核具体配置说明如下。

- Frame Buffers配置为4个。

- Write Burst Size、Read Burst Size均配置为128。

- 读通道的Stream Date Width配置为8。

- 读/写通道的Line Buffer Depth均配置为2048。

编辑

图 38

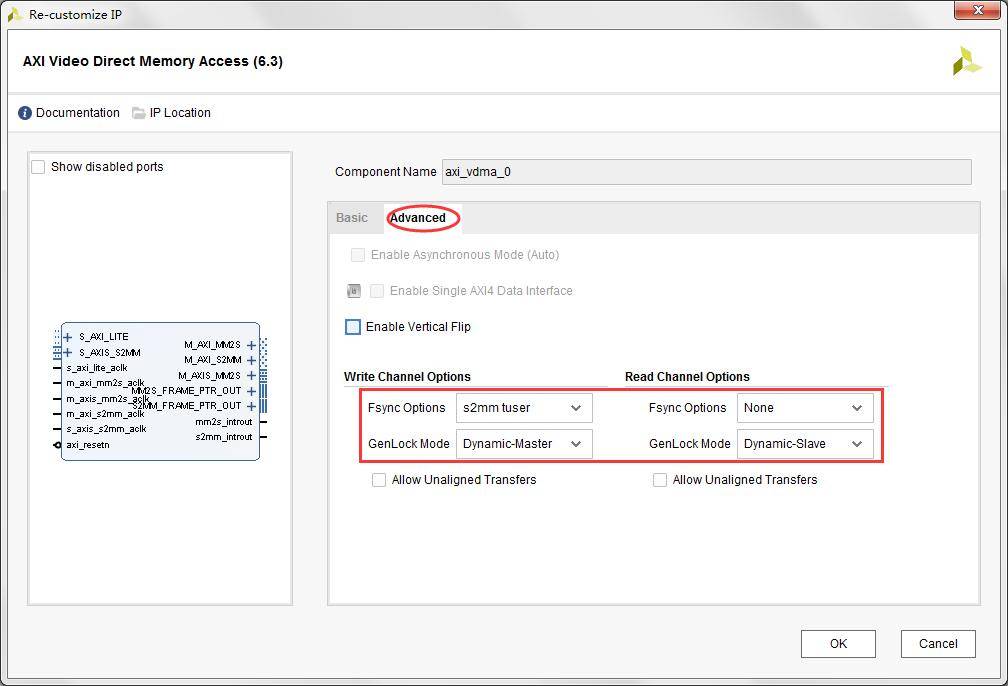

- 点击Advanced,保持默认配置,即可避免VDMA同时读写同一个Buffer,造成视频数据传输乱码。

编辑

图 39

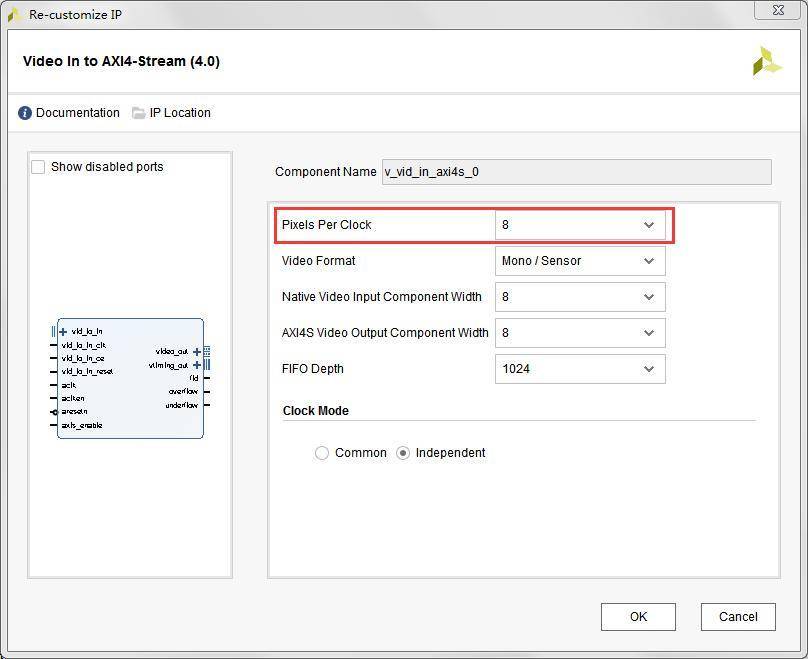

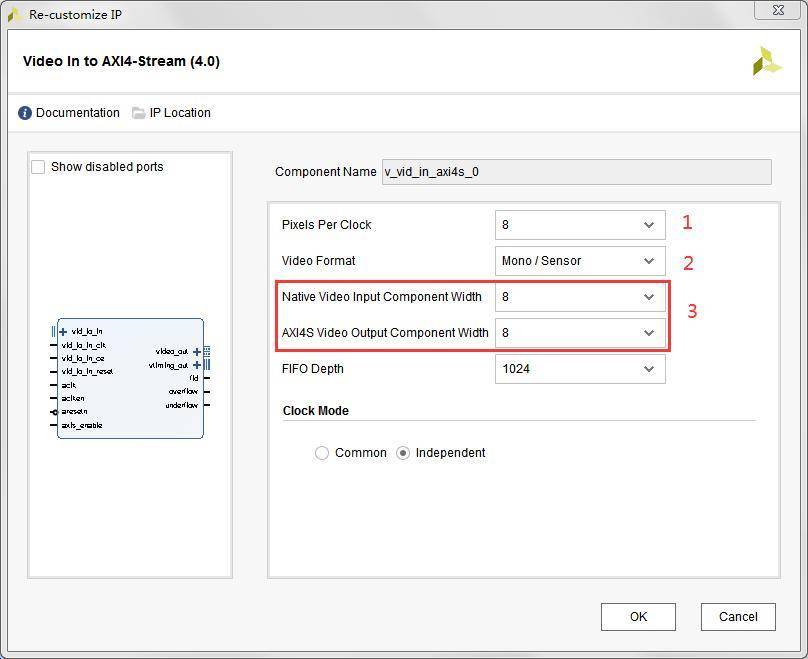

Video In to AXI4-Stream IP核 本案例使用Video In to AXI4-Stream IP核将并行视频信号转换为AXI4-Stream视频流。

Video In to AXI4-Stream IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg043_v_vid_in_axi4s.pdf》,具体配置说明如下。

- Full模式:Pixels Per Clock配置为8,即每个时钟8个像素。Base模式:Pixels Per Clock配置为2,即每个时钟2个像素。

- 视频格式配置为Mono/Sensor。

- 数据位宽配置为8bit。

编辑

图 40

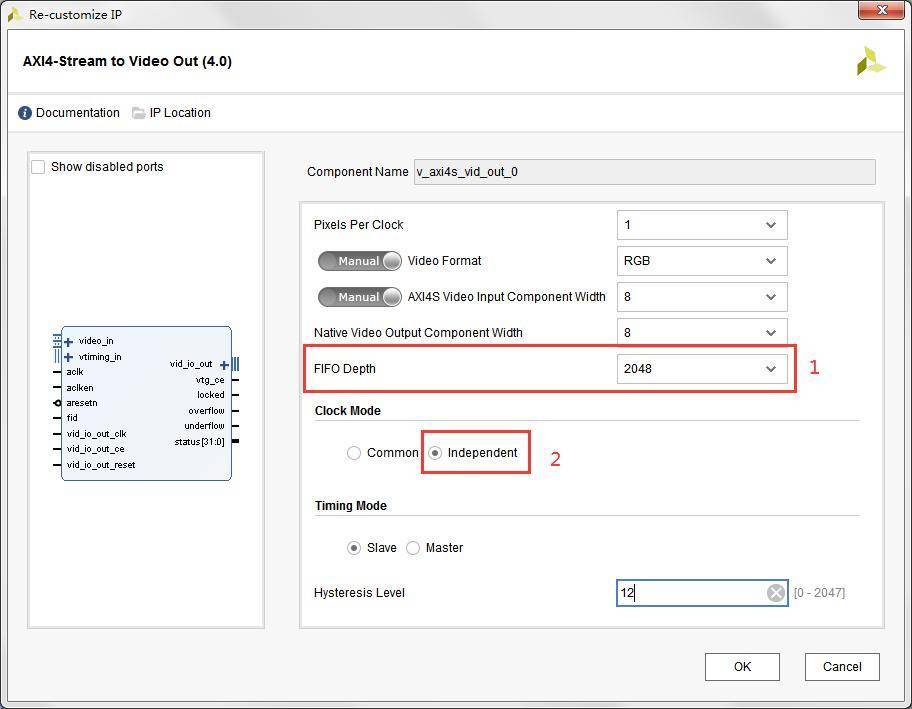

AXI4-Stream to Video Out IP核 本案例使用AXI4-Stream to Video Out IP核将AXI4-Stream视频流转化为并行视频信号。

AXI4-Stream to Video Out IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg044_v_axis_vid_out.pdf》,具体配置说明如下。

- FIFO Depth配置为2048。

- Clock Mode配置为Independent(独立时钟)。

编辑

图 41

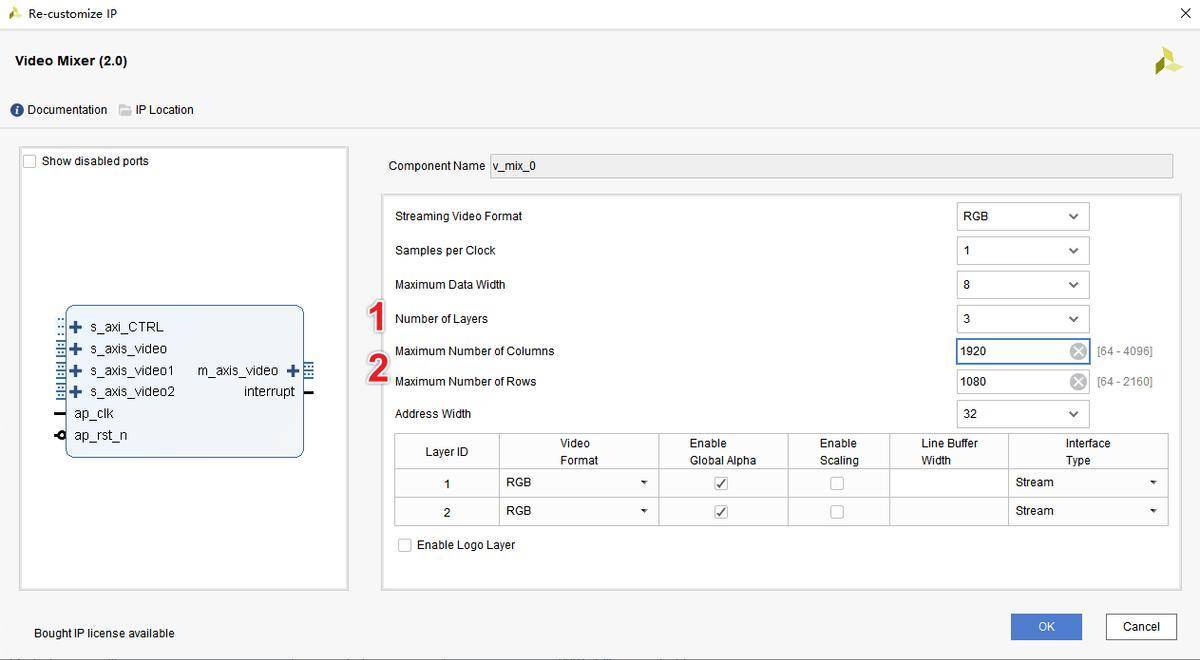

Video Mixer IP核 本案例使用Video Mixer IP核将视频数据叠加到1920 x 1080分辨率的视频中。

Video Mixer IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg243-v-mix-v2.0.pdf》,具体配置说明如下。

Mixer通过MicroBlaze配置寄存器进行使能。

编辑

图 42

- Number of Layers配置为3,其中Master Layer(s_axis_video)未使用,仅使用Layer1(s_axis_video1)与Layer2(s_axis_video2)。当采集黑白CameraLink相机的图像时,使用Layer1;当采集彩色CameraLink相机的图像时,使用Layer2。

- 配置可支持的最大分辨率为1920 x 1080。

编辑

图 43

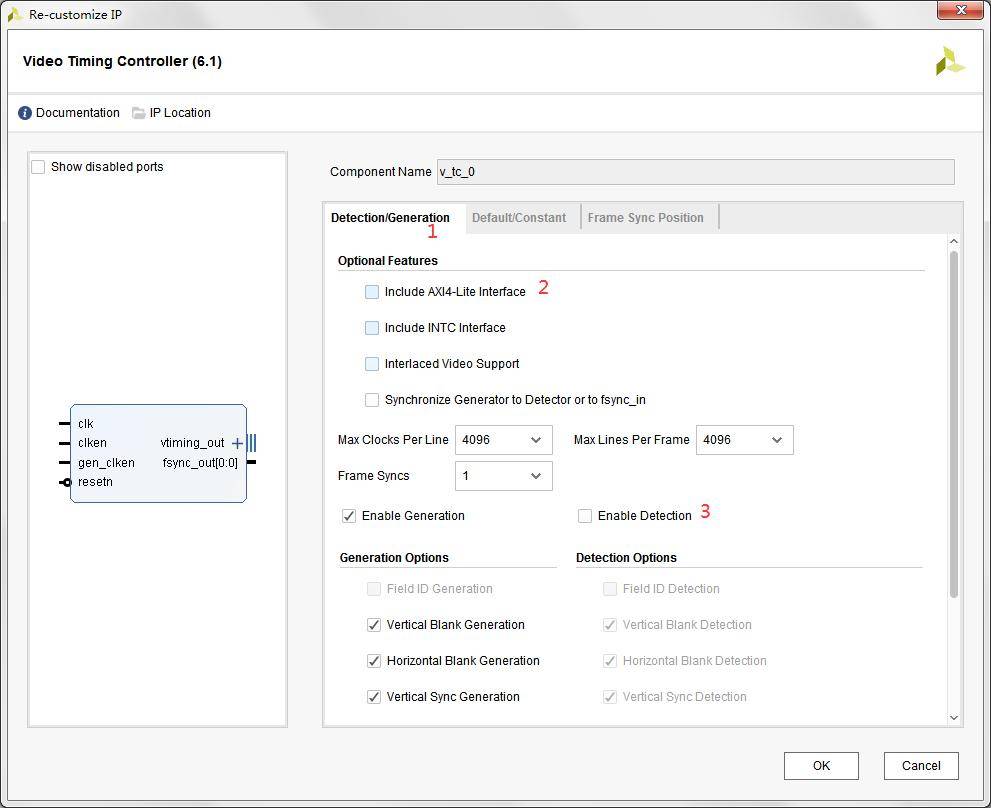

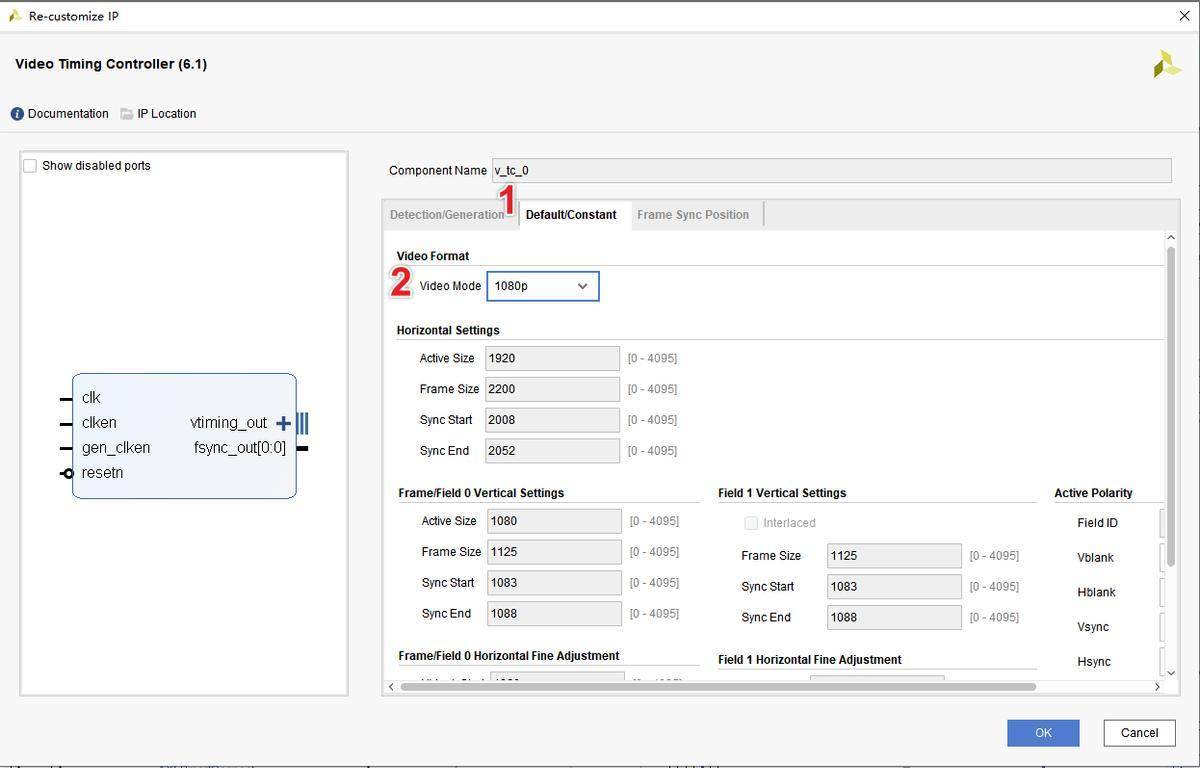

VTC IP核 本案例使用VTC IP核产生用于视频输出的时序。

VTC(Video Timing Controller) IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg016_v_tc.pdf》,具体配置说明如下。

- 点击Detection/Generation,确保不勾选"Include AXI4-Lite Interface"及"Enable Detection"。

编辑

图 44

- 点击Default/Constant,Video Mode配置为1080p,其余配置保持默认。

编辑

图 45

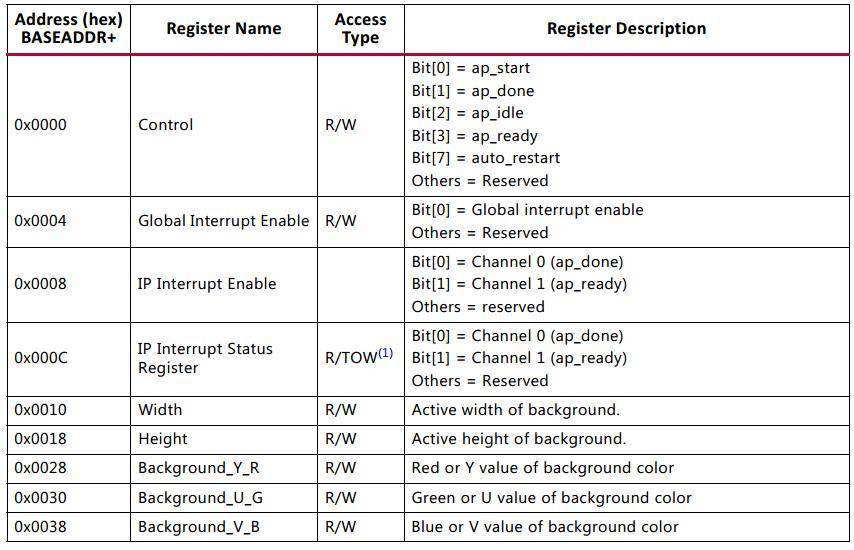

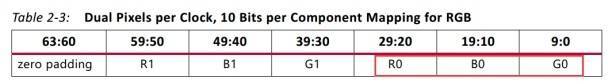

Sensor Demosaic IP核 本案例使用Sensor Demosaic IP核将彩色CameraLink相机的Bayer格式视频数据转化为RGB格式。

Sensor Demosaic IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg286-v-demosaic.pdf》,具体配置说明如下。图像宽高以及Bayer的格式,通过MicroBlaze配置寄存器进行设置。

编辑

图 46

由于Sensor Demosaic IP核视频数据输出格式为RBG,因此使用AXI4-Stream Subset Converter IP核将RBG转换成RGB,再进行视频输出。

编辑

图 47

编辑

图 48

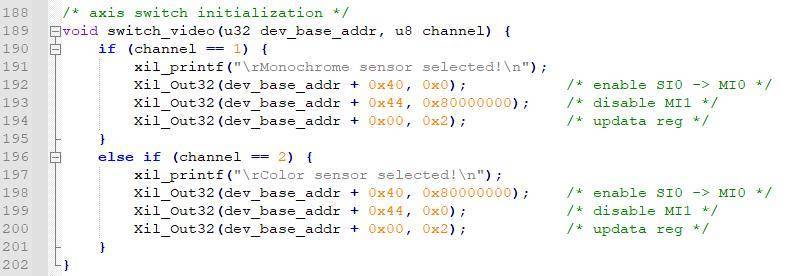

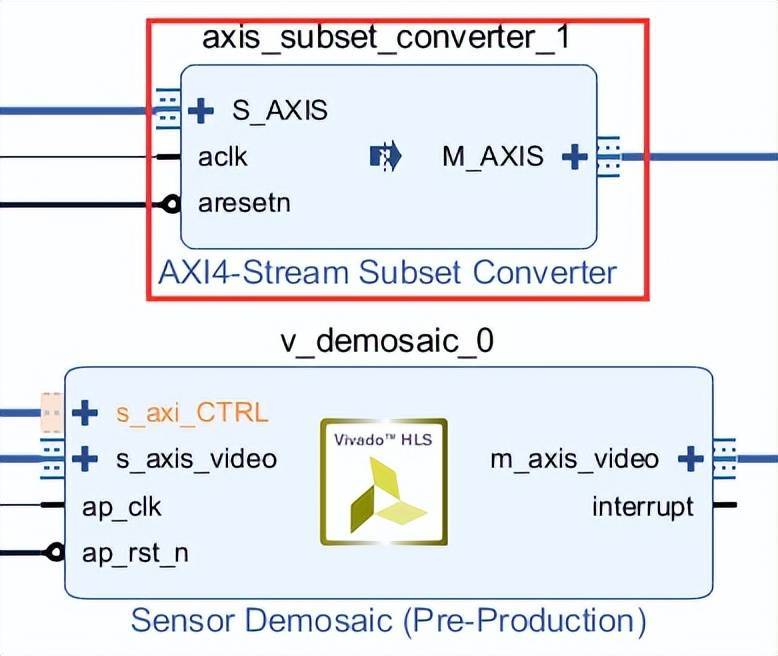

AXI4-Stream Switch IP核 本案例使用AXI4-Stream Switch IP核选择黑白或彩色CameraLink相机视频数据进行处理。

AXI4-Stream Switch IP核开发文档为产品资料“6-开发参考资料Xilinx官方参考文档”目录下的《pg085-axi4stream-infrastructure.pdf》,具体配置说明如下。本案例通过MicroBlaze配置寄存器,选择将S00_AXIS(视频数据输入通道)路由到M00_AXIS(黑白CameraLink相机视频数据处理通道)或M01_AXIS(彩色CameraLink相机视频数据处理通道)。

- Number of slave interfaces配置为1,即配置1个Slave接口。

- Number of master interfaces配置为2,即配置2个Master接口。

- Use control register routing配置为Yes,即使能AXI4-Lite接口。

编辑

图 49

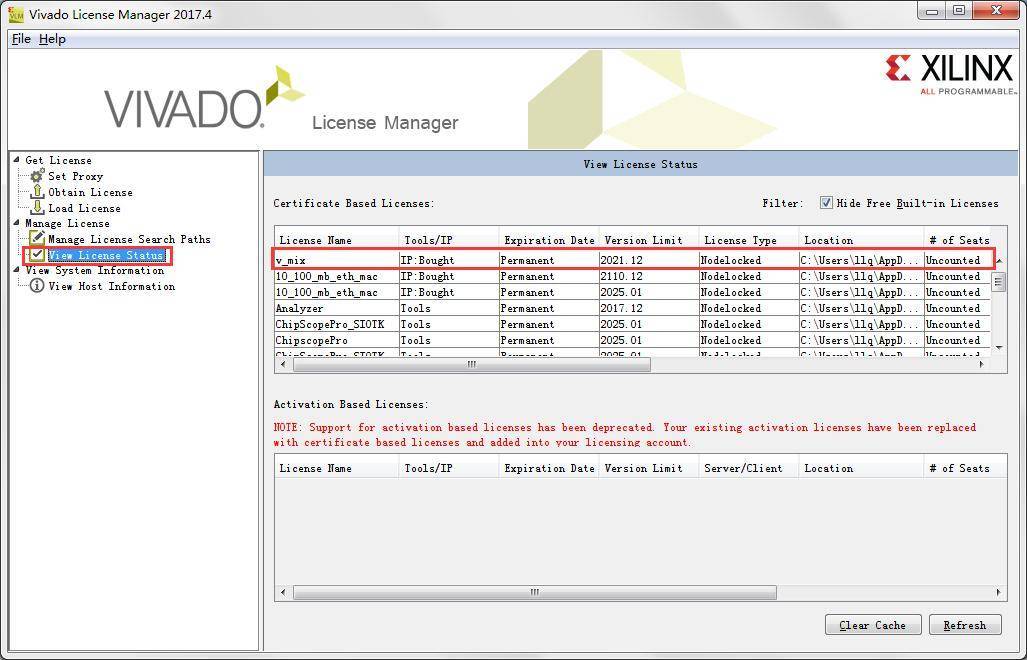

Vivado工程编译 申请IP核License 如需重新编译工程或打开Video Mixer IP核,需在Xilinx官网申请Video Mixer IP核的免费License,并将其正确导入。License申请与导入方法,请查阅调试工具安装文档相关章节,其它IP核无需License。

成功导入后,可在View License Status窗口发现新添加的License。

编辑

图 50

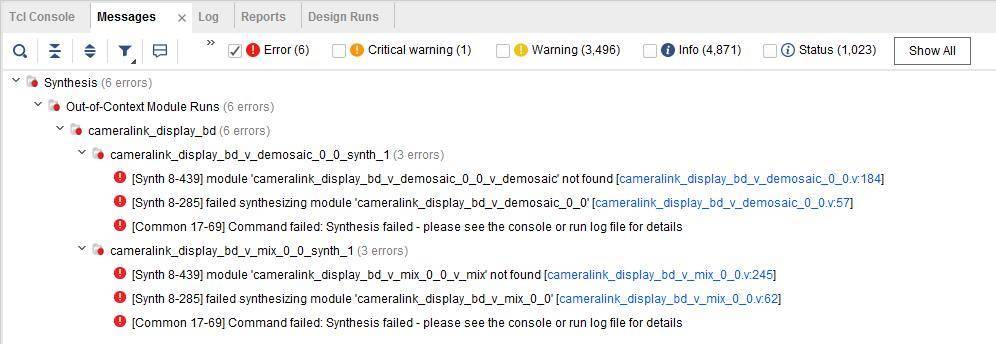

工程编译异常解决 本案例包含HLS IP核,由于Vivado工程文件路径过长,可能导致工程编译过程中出现如下错误。

编辑

图 51

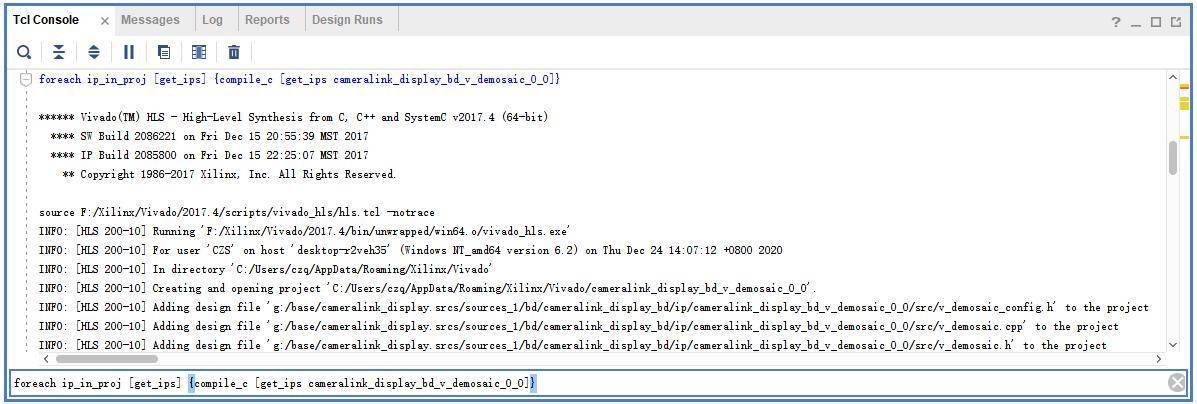

可在Tcl Console窗口执行如下命令,重新生成HLS IP核相关文件,即可正常编译工程。

Vivado# foreach ip_in_proj [get_ips] {compile_c [get_ips cameralink_display_bd_v_demosaic_0_0]}

编辑

图 52

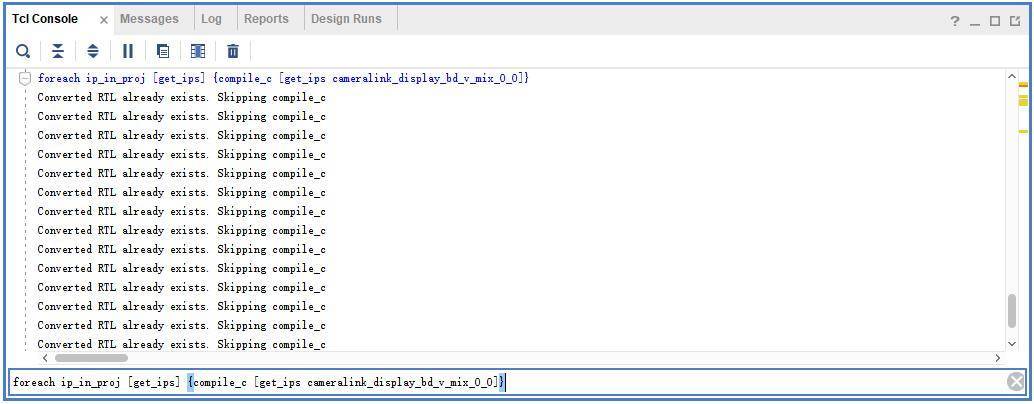

Vivado# foreach ip_in_proj [get_ips] {compile_c [get_ips cameralink_display_bd_v_mix_0_0]}

编辑

图 53