为了验证我的板子上的32.768K晶振是否有问题,我特地买了块ESP-WROVER-KIT

开发板来验证,因为只有这个开发板上配置有外部32.768K的晶振。

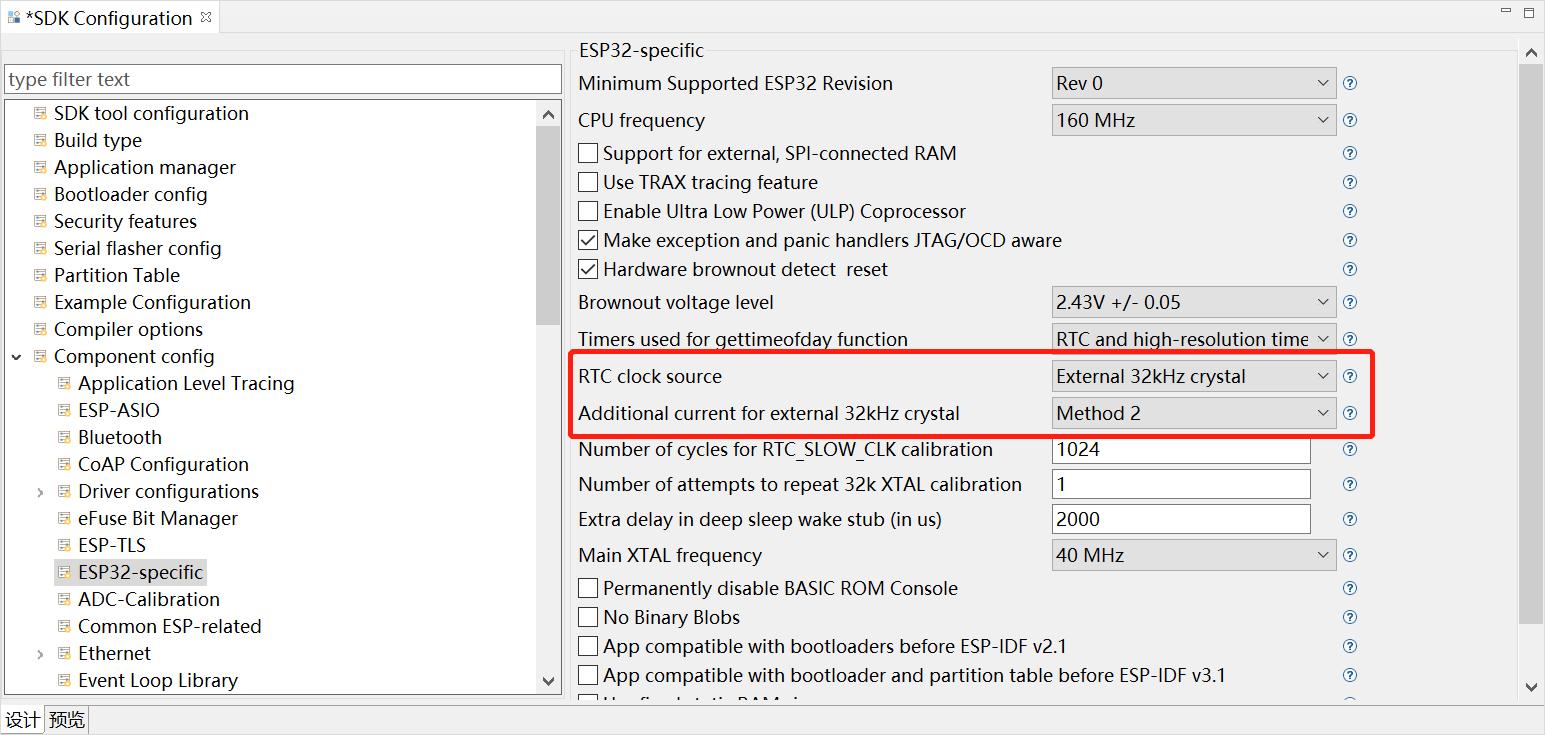

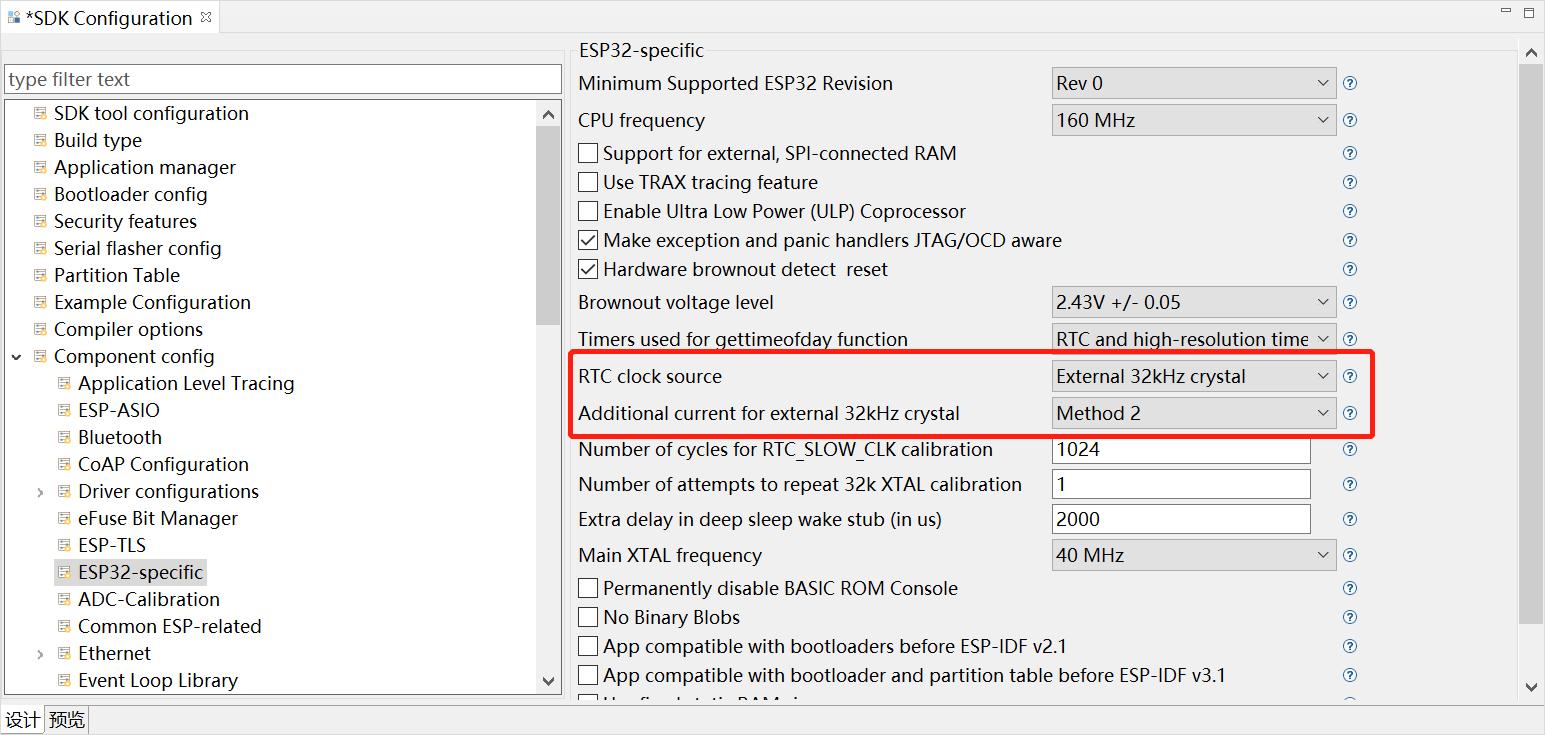

首先我使用了ESP-WROVER-KIT配套的例程:“examplesperipheralsspi_masterlcd”,然后sdkconfig->Component config->ESP32-specific->RTC clock source->External 32kHz crystal,然后Addi

tional current for external 32kHz crystal中三个选项都试过,如下图:

RTC.png (81.13 KiB) Viewed 10004 times

依然无法使32.768K起振,上电信息如下:Code: Select all

ets Jul 29 2019 12:21:46rst:0x1 (POWERON_RESET),boot:0x1e (SPI_FAST_FLASH_BOOT)configsip: 0, SPIWP:0xeeclk_drv:0x00,q_drv:0x00,d_drv:0x00,cs0_drv:0x00,hd_drv:0x00,wp_drv:0x00mode:DIO, clock div:2load:0x3fff0030,len:6708load:0x40078000,len:15340load:0x40080400,len:3808entry 0x40080694I (27) boot: ESP-IDF v4.4-beta1 2nd stage bootloaderI (27) boot: compile time 16:29:13I (28) boot: chip revision: 3I (30) boot_comm: chip revision: 3, min. bootloader chip revision: 0I (37) boot.esp32: SPI Speed : 40MHzI (42) boot.esp32: SPI Mode : DIOI (47) boot.esp32: SPI Flash Size : 2MBI (51) boot: Enabling RNG early entropy source...I (56) boot: Partition Table:I (60) boot: ## Label Usage Type ST Offset LengthI (67) boot: 0 nvs WiFi data 01 02 00009000 00006000I (75) boot: 1 phy_init RF data 01 01 0000f000 00001000I (82) boot: 2 factory factory app 00 00 00010000 00100000I (90) boot: End of partition tableI (94) boot_comm: chip revision: 3, min. application chip revision: 0I (101) esp_image: segment 0: paddr=00010020 vaddr=3f400020 size=19bbch (105404) mapI (148) esp_image: segment 1: paddr=00029be4 vaddr=3ffb0000 size=02784h ( 10116) loadI (152) esp_image: segment 2: paddr=0002c370 vaddr=40080000 size=03ca8h ( 15528) loadI (160) esp_image: segment 3: paddr=00030020 vaddr=400d0020 size=18f14h (102164) mapI (199) esp_image: segment 4: paddr=00048f3c vaddr=40083ca8 size=08fe4h ( 36836) loadI (214) esp_image: segment 5: paddr=00051f28 vaddr=50000000 size=00010h ( 16) loadI (221) boot: Loaded app from partition at offset 0x10000I (221) boot: Disabling RNG early entropy source...I (235) cpu_start: Pro cpu up.I (235) cpu_start: Starting app cpu, entry point is 0x400810f0I (0) cpu_start: App cpu up.W (397) clk: 32 kHz XTAL not found, switching to internal 150 kHz oscillatorI (405) cpu_start: Pro cpu start user codeI (405) cpu_start: cpu freq: 160000000I (405) cpu_start: Application information:I (409) cpu_start: Project name: spi_masterI (415) cpu_start: App version: 1I (419) cpu_start: Compile time: Dec 17 2021 16:29:05I (425) cpu_start: ELF file SHA256: 985b0254728d80f3...I (431) cpu_start: ESP-IDF: v4.4-beta1I (437) heap_init: Initializing. RAM available for dynamic allocation:I (444) heap_init: At 3FFAE6E0 len 00001920 (6 KiB): DRAMI (450) heap_init: At 3FFB35E8 len 0002CA18 (178 KiB): DRAMI (456) heap_init: At 3FFE0440 len 00003AE0 (14 KiB): D/IRAMI (462) heap_init: At 3FFE4350 len 0001BCB0 (111 KiB): D/IRAMI (469) heap_init: At 4008CC8C len 00013374 (76 KiB): IRAMI (476) spi_flash: detected chip: genericI (480) spi_flash: flash io: dioW (484) spi_flash: Detected size(4096k) larger than the size in the binary image header(2048k). Using the size in the binary image header.I (498) cpu_start: Starting scheduler on PRO CPU.I (0) cpu_start: Starting scheduler on APP CPU.LCD ID: 00000000ILI9341 detected.LCD ILI9341 initialization.

由开机信息

W (397) clk: 32 kHz XTAL not found, switching to internal 150 kHz oscillator

可以得知没能起振,然后通过示波器查看晶振两个管脚均没有波形产生,只有在上电的过程中有5个30.86K频率的方波。

[size=150%]

请问,要使用这外部32.768K的晶振,sdkconfig或者代码里还有哪些配置要设置的吗???

各位坛友,有用过的指导一下呗。

还有esp-idf中哪个examples是与这32.768K晶振或者RTC相关的?我都翻遍了,没找着。

RTC.png (81.13 KiB) Viewed 10004 times

RTC.png (81.13 KiB) Viewed 10004 times

举报

举报