#2024,为FPGA生态加油,为FPGA社区点赞#新手入门的简单小例子,主要给入门的新手建立时间或者说时序的概念,最近看了不少的资料基本上都是以点灯为例,估计是大家对嵌入式开发和FPGA的普遍共识,这两天逛B站发现了也不少比较好的视频教程,我就在这里二次提炼一下,做上几篇文章,为大家的学习垫上两块砖头。

实验之前:

(1)默认对应的FPGA外部输入时钟为50MHz,这样对应的时钟周期就为20ns(当然其他的频率也可以,这里以50MHz时钟来举例);

(2)不限制开发板类型、IDE类型;

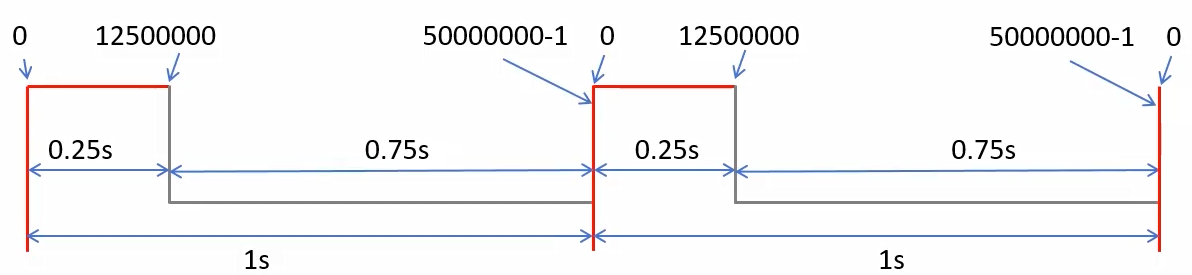

(3)实现目的按照图示完成对应的功能即为一秒之内0.25秒点亮0.75秒熄灭;

时序分析图:

module led_ctrl_1(

input wire clk,

input wire rst_n,

output reg led

);

parameter CNT_1S_MAX = 26'd50_000_000 - 1;

parameter CNT_025S_MAX = 26'd12_500_000 - 1;

//为什么要减1,大家可以思考一下从0到9是几个数,如果认为是9个的那么可以放弃学习FPGA了

//完成1秒的计数周期

reg [25:0] counter;

always @(posedge clk or negedge rst_n)

if( rst_n == 1'b0 )

counter <= 26'b0;

else if( counter == CNT_1S_MAX )

counter <= 26'b0;

else

counter <= counter + 1'b1;

//在这里建议能在对应的数值前加上位数的还是加上位数,我记得不加位数会被默认为32位,不知道是不是还是这样

//在1秒的周期内设定对应led翻转的时间节点并完成操作

always @(posedge clk or negedge rst_n)

if( rst_n == 1'b0 )

led <= 1'b1; //因起始位高电平

else if( counter == CNT_025S_MAX )

led <= ~led;

else if( counter == CNT_1S_MAX )

led <= ~led;

else

led <= led; //避免产生锁存器

endmodule

对应的测试模块:

`timescale 1ns/1ns

module tb_led_ctrl_1();

//****************** Parameter and Internal Signal *******************//

//wire define

wire led;

//reg define

reg clk;

reg rst_n;

//***************************** Main Code ****************************//

initial begin

clk = 1'b1;

rst_n <= 1'b0;

#201

rst_n <= 1'b1;

#2_000_000;

$stop;

end

//参数重定义缩短仿真时间(大家的时间很宝贵,尽量不要浪费)

defparam led_ctrl_1_inst.CNT_1S_MAX = 26'd5_000 - 1;

defparam led_ctrl_1_inst.CNT_025S_MAX = 26'd1_250 - 1;

// creator clk

always #10 clk <= ~clk;

//*************************** Instantiation **************************//

led_ctrl_1 led_ctrl_1_inst

(

.clk ( clk ),

.rst_n ( rst_n ),

.led ( led )

);

endmodule

仿真结果:

对应的时间放大1万倍即为实际设计值举例波形图中的高电平25us,乘以10000即为实际时间,即0.25s;

最后对应的图片使用了小梅哥视频中的图,特此表示感谢!

更多回帖