可能的原因有以下几个:

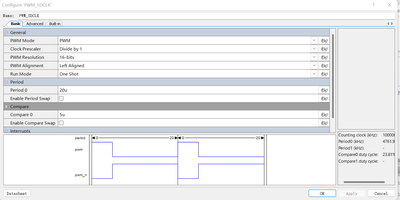

1. 初始化设置不正确:请确保你已经正确地配置了PWM输出的引脚和初始化寄存器。检查初始化代码以确保所有的参数都被正确地设置。

2. 时钟频率问题:有可能时钟频率设置不正确导致PWM输出不正常。请检查PWM的时钟源是否正确配置,并且时钟频率是否符合要求。

3. 周期参数设置不正确:请检查PWM的周期参数是否正确设置。如果初始化代码中的周期参数设置不正确,可能导致PWM输出一直为低电平。

4. 功能配置错误:请确定你已经正确地配置了PWM的功能模块和控制寄存器,以确保正确的功能被使能。

可能的原因有以下几个:

1. 初始化设置不正确:请确保你已经正确地配置了PWM输出的引脚和初始化寄存器。检查初始化代码以确保所有的参数都被正确地设置。

2. 时钟频率问题:有可能时钟频率设置不正确导致PWM输出不正常。请检查PWM的时钟源是否正确配置,并且时钟频率是否符合要求。

3. 周期参数设置不正确:请检查PWM的周期参数是否正确设置。如果初始化代码中的周期参数设置不正确,可能导致PWM输出一直为低电平。

4. 功能配置错误:请确定你已经正确地配置了PWM的功能模块和控制寄存器,以确保正确的功能被使能。

举报

举报

举报

举报