DDR是运行内存芯片,其运行频率主要有100MHz、133MHz、166MHz三种,由于DDR内存具有双倍速率传输数据的特性,因此在DDR内存的标识上采用了工作频率×2的方法。

DDR芯片内存的工作原理可以分为两部分, 一部分是时序,一部分是数据传输 。

控制DDR内存的时序,是由内存控制器控制的,它负责管理内存的读写操作。内存控制器会向DDR内存发送时钟信号,这个时钟信号被称为 系统时钟 。

DDR内存的数据传输,是通过前沿和下降沿来实现的。在每个时钟周期的前沿和下降沿,DDR内存会传输一个数据,这意味着DDR内存的传输速度是普通SDRAM的 两倍 。

DDR内存条的引脚数,取决于内存条的类型和规格。以下是一些常见的 DDR内存条类型和它们的引脚数 :

DDR1内存条,184引脚(92针对每侧)

DDR2内存条,240引脚(120针对每侧)

DDR3内存条,240引脚(120针对每侧)

DDR4内存条,288引脚(144针对每侧)

DDR5内存条,288引脚(144针对每侧)

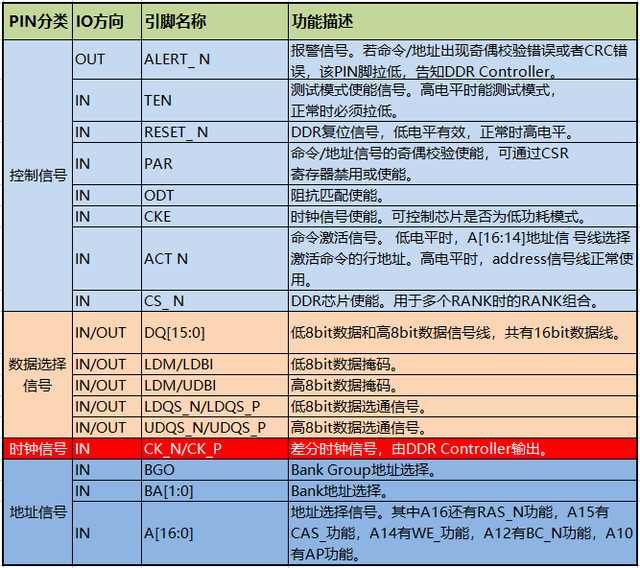

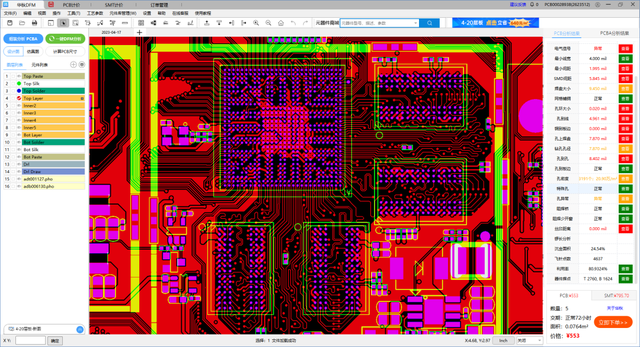

DDR芯片引脚功能如下图所示:

DDR数据线的分组:

DQ0到DQ7差分,是DQS0_N和DQS0_P加上DQM0为底8位。

DQ8到DQ15差分,是DQS1_N和DQS1_P加上DQM1为高8位。

时钟命令线,是CLK_N和CLK_P,其他的为地址线。

DDR信号分组,可分为数据信号、时钟信号、地址/命令信号、控制信号等四个信号组。

一、时钟组

1、DDR时钟回路的走线需完整的地平面,给回路电流提供一个低阻抗的路径。

2、DDR差分时钟信号都必须在关键平面上走线,尽量避免层到层的转换。

3、信号线的单线阻抗应控制在50~60Ω。

4、差分阻抗控制在100~120Ω。

5、时钟信号到其他信号应保持在20mil以上,防止对其他信号的干扰。

6、蛇形走线的间距不应小于20mil。

二、数据组

1、数据组包括DQ、DQS、DM。

2、以低8位数据为例,该数据组包括:DQ[7..0]、DQS[0]、DM[0]数据组。

3、以地平面为参考,给信号回路提供完整的地平面。

4、特征阻抗控制在50~60Ω。

5、与其他非DDR信号间距至少隔离20mil。

三、地址、命令组

1、地址组包括ADD、BANK、RAS、CAS、WE。

2、布线要求需保持完整的地和电源平面。

3、特征阻抗控制在50~60Ω。

4、信号组与其他非DDR信号间距,至少保持在 20mil以上。

四、控制组

1、控制组包括CS、CKE。

2、布线要求需保持完整的地和电源平面。

3、为了防止串扰,本组内信号不能和数据信号在同一个电阻排内。

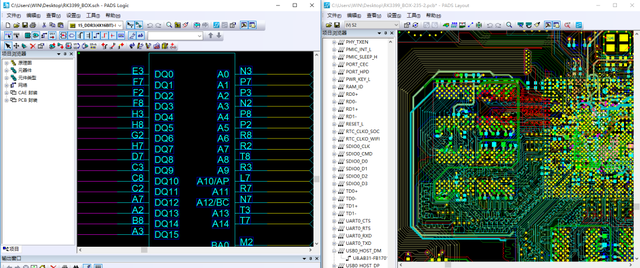

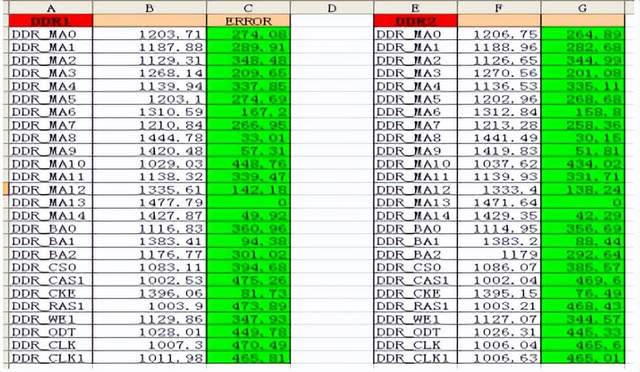

DDR信号等长约束,由于DDR工作频率高,对信号等长有更严格的要求,实际的PCB设计中,对所有信号都进行等长控制是不太现实的,也没有这个必要,DDR的等长约束只需要四个参数:

1、差分时钟之间(CLK_P与CLK_N)等长不大于 5mil。

2、地址、控制组中每个信号都以时钟(CLK_N)为基准,等长差范围设置为±150mil。

3、数据组内以DQ[0]为基准,等长控制在25mil以内。

4、各数据组之间,以时钟线为基准,等长差范围设置为0-500mil。

1、阻抗

在制造过程中阻抗线的公差是+/-10%,普通走线一般是+/-20%,阻抗线要求更加精确,因此阻抗线设计最好大于普通线最小的制成能力。

2、线宽线距

线宽线距设计的越小,生产难度越大,成本越高,因此在生产前使用可制造性软件检测线宽线距,评估生产能力及制造成本。

3、焊盘大小

焊盘的大小关乎SMT组装焊接的可靠性,BGA焊盘直径需大于焊球直径的20%~25%,才能有可靠的附着力,因此做板前使用装配分析软件,匹配实物的元件库评估DDR芯片的可焊性。

这里推荐一款一款可制造性检查的工艺软件: 华秋DFM ,对于DDR芯片安装的PCB设计,可以检查其 线宽、线距是否符合生产的工艺能力 ,以及 焊盘大小是否满足组装要求 ,同时也可以 模拟计算DDR的阻抗 ,提前判断要设计的线宽线距、叠层规划等。

更多回帖