在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。

建议层叠为TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基铜厚度建议全部采用1oZ,厚度为1.6mm。

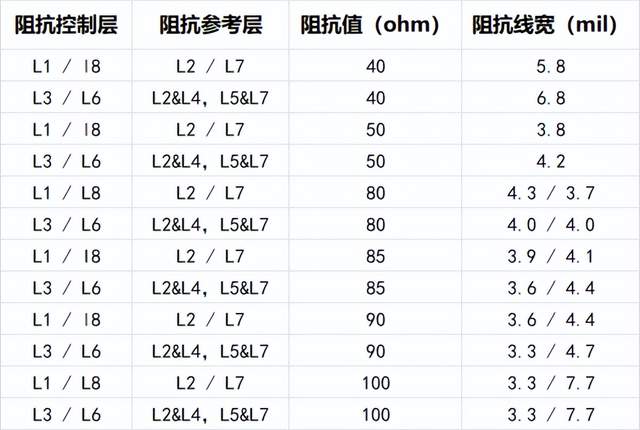

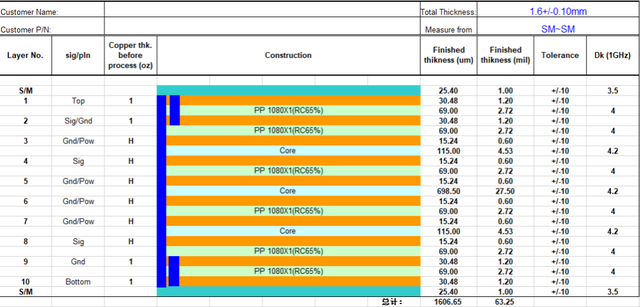

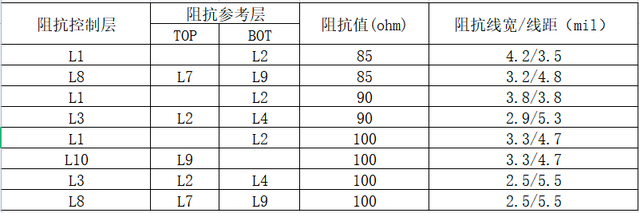

板厚推荐叠层如下图(上)所示(8层通孔1.6mm厚度推荐叠层),阻抗线宽线距如下图(下)所示(8层通孔1.6mm厚度各阻抗线宽线距)。

在10层1阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。

建议层叠为TOP-Signal/Gnd-Gnd/Power-Signal-Gnd/Power-Gnd/Power-Gnd/Power-Signal-Gnd-Bottom,其中L1,L2,L9,L10,建议采用1oZ,其它内层采用HoZ。

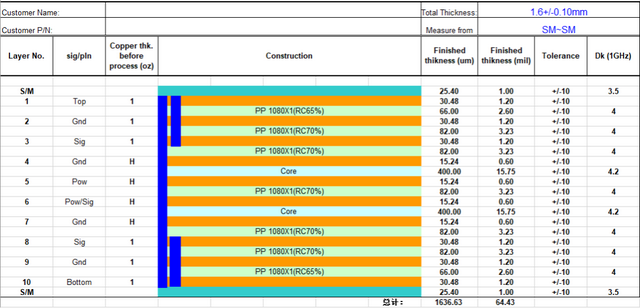

板厚推荐叠层如下图(上)所示(10层1阶HDI板叠层设计),阻抗线宽线距如下图(下)所示(10层1阶HDI板阻抗设计)。

在10层2阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。

建议层叠为TOP-Gnd-Signal-Gnd-Power-Signal/Pow -Gnd-Signal-Gnd-Bottom,其中L1,L2,L3,L8,L9,L10,建议采用1oZ,其它内层采用HoZ。

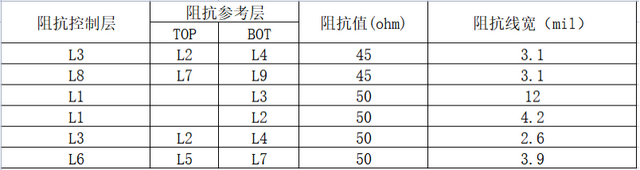

板厚推荐叠层如下图(上)所示(10层2阶HDI板叠层设计),阻抗线宽线距如下图(中、下)所示(10层2阶HDI板单端、差分阻抗设计图)。

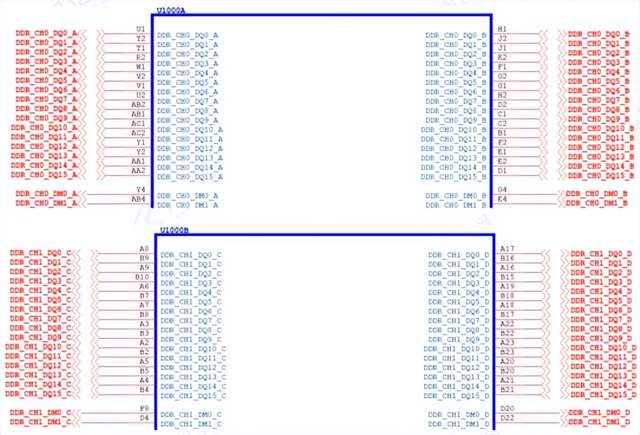

所有通道数据DQ、DM单端信号阻抗40欧姆,如果叠层无法满足40欧目标阻抗,至少保证阻抗满足45ohm±10%,40欧目标阻抗信号余量会更大,45欧目标阻抗信号余量会更小,如下图是CH0与CH1通道数据DQ、DM阻抗线。

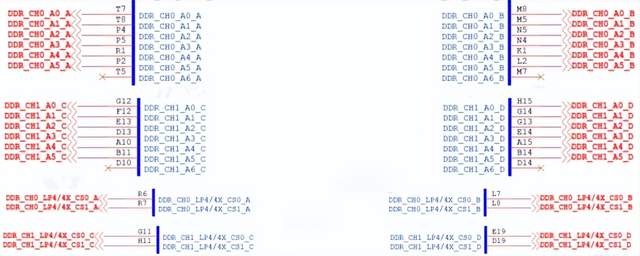

所有通道地址、控制单端信号阻抗40欧姆,如下图是CH0与CH1通道地址、控制阻抗线。

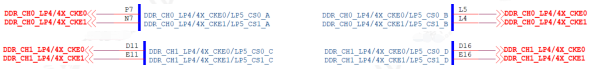

CKE单端信号阻抗50欧姆,如下图是CH0与CH1通道CKE阻抗线。

所有通道数据锁存信号DQS与时钟差分信号阻抗80欧姆,如果叠层无法满足80欧目标阻抗,至少保证阻抗满足90ohm±10%,如下图是CH0与CH1通道DQS与CLK差分阻抗线。

阻抗的知识点非常多,相信大家也竟然为此困扰,这里推荐一款可以一键智能计算阻抗自动叠层的工具: 华秋DFM软件 ,使用其阻抗计算功能,可以高效轻松反算和计算所需阻抗和线宽线距等。

更多回帖