本此实验操作视频是基于创龙教仪DSP教学实验箱TL6748-PlusTEB录制完成的。

本节视频的目的是学习OV2640 摄像头和VPIF总线的工作原理,并实现VPIF 总线控制摄像头采集图像显示在 LCD 上。

OV2640 是世界上第一个 1/4 英寸 2 百万像素视频传感器,同时是 OmniVision 最新的

2.2 微米 OmniPixel2™架构的视频传感器,可支持 200 万像素,分辨率可高达 1600x1200,

帧率可达 30 帧/秒,最高帧率可达 60 帧/秒。

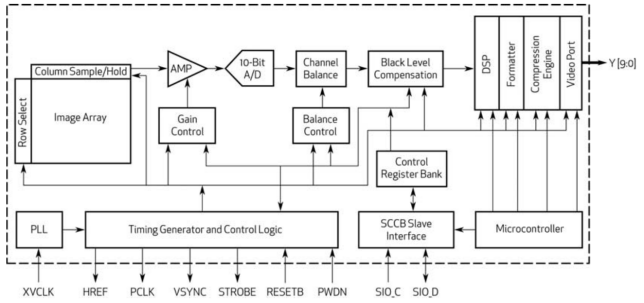

OV2640摄像头采集图像时,会先经过感光元件,采样的信号经过运放,再进行AD转换,AD量化之后得到数字化的视频信号会进行控制调整,最终通过视频输出接口输出。

除此之外还有其他的一些信号接口,比如时钟输入,像素时钟,行同步信号,帧同步信号,时序产生和逻辑控制单元等等。

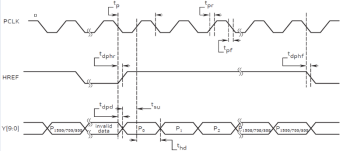

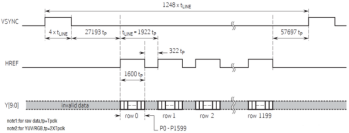

图像数据在HREF为高的时候输出,当HREF变高后,每一个PCLK时钟,输出一个字节数据。比如我们采用UXGA时序,RGB565格式输出,每2个字节组成一个像素的颜色(低字节在前,高字节在后),这样每行输出总共有16002个PCLK周期,输出16002个字节。

当HREF输出高电平时开始读取一行像素点,当低电平时不操作,重复操作即可读取一帧图像。OV2640支持:RGB565或JPEG输出。RGB565输出时,时序如图所示。JPEG输出时,PCLK大大减少,且HREF不连续,数据流以0XFF,0XD8开头,以0XFF,0XD9结束。

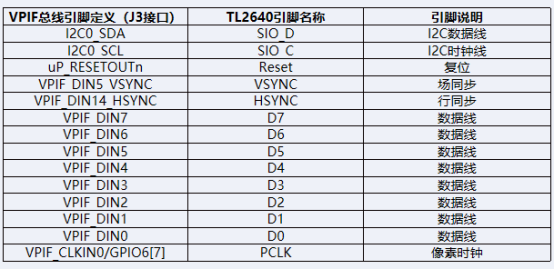

TL2640摄像头模块和实验板的连接引脚对应表如表所示。DSP通过I2C总线配置摄像头的相关寄存器,摄像头采集的数据通过VPIF总线传输回DSP进行处理。

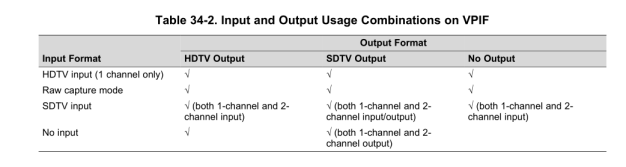

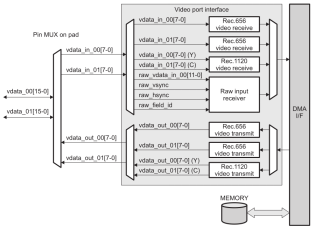

Video Port Interface (VPIF), 是一种视频接口。VPIF的通道0和通道1只能用于接收数据,通道2和通道3只能用于发送数据

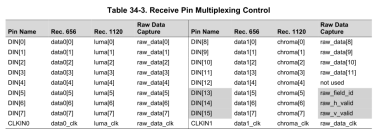

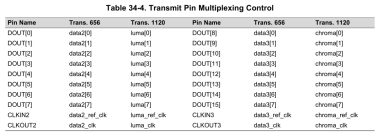

VPIF 接口主要支持三种协议的传输:

BT-656

BT-1120

Raw Capture mode

其中,VPIF 端口接收通道支持BT-656、BT-1120和Raw Capture mode三种协议,

VPIF 端口发送通道只支持BT-656和BT-1120两种协议。

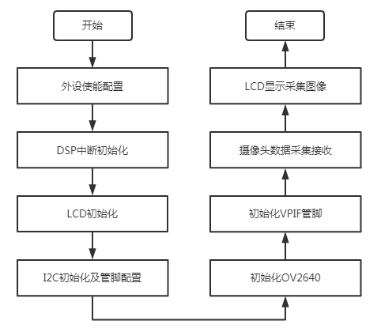

程序流程

接下来我们先看下程序的流程设计。

程序流程设计中首先要进行外设使能配置,接着进行DSP中断初始化和LCD的初始化,然后初始化配置I2C和OV2640摄像头,初始化VPIF总线。最后摄像头采集接收数据并将数据显示在LCD上。

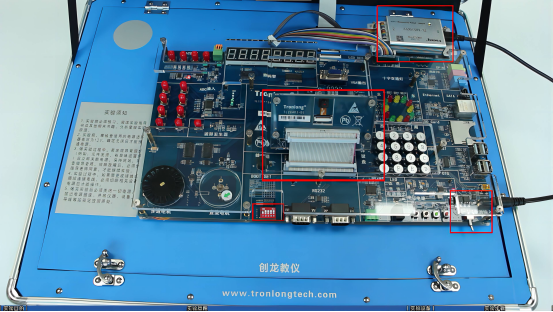

本实验使用的硬件接口为LCD和VPIF 接口,所需硬件为实验板、仿真器、TL2640I 摄像头模块、LCD和电源。

(1)将 TL2640I 摄像头模块连接到实验板的 VPIF 接口。

(2)连接仿真器和电脑的USB接口,

(3)将拨码开关拨到DEBUG模式01111,连接实验箱电源,拨动电源开关上电。

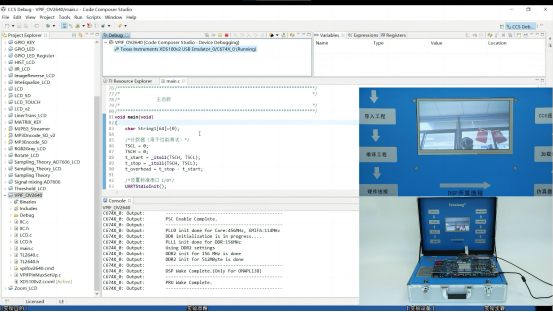

导入工程,选择Demo文件夹下的对应工程

编译工程

将CCS连接实验箱并加载程序

点击运行程序

在LCD屏幕上会显示摄像头采集的图像,并显示帧率。

更多回帖