在本文中,我们将探讨如何估算桥式电路中理想的死区时间。

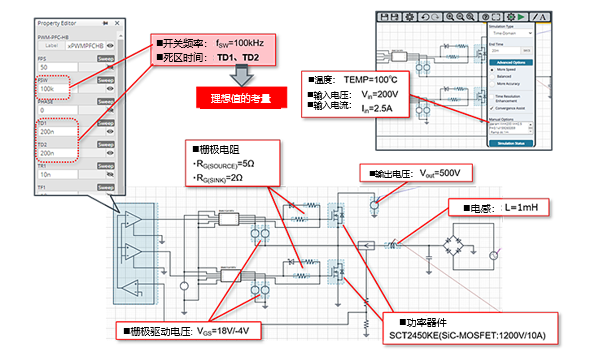

电路以Power Device Solution Circuit/AC-DC PFC的一览表中的仿真电路“A-6. PFC CCM Synchro V in =200V I in =2.5A”为例(参考图16)。关于更详细的电路图,还可以通过这里查看。

由于该电路是进行同步整流工作的电路,所以我们通过仿真来探讨高边(HS)和低边(LS)SiC MOSFET SCT2450KE的死区时间理想值,即不直通的最短时间。死区时间可以通过仿真工具的PWM控制器参数TD1(HS)和TD2(LS)来分别设置。

图16:PFC仿真电路“A-6. PFC CCM Synchro V in =200V I in =2.5A”

图17表示死区时间内的电流流动情况。在桥式结构的电路中,要防止直通电流,就需要确保足够的死区时间长度,但如果将死区时间设置得过长,会导致损耗增加。这是因为在死区时间内,SiC MOSFET处于OFF状态,因此电流会流过体二极管。通常,体二极管的导通损耗比较大,其导通时间越长,损耗越大。

图17:死区时间内的电流流动情况

图18表示死区时间长度与电感电流IL之间的关系。如果死区时间过长,低电压区域可能会变为断续工作状态,电感电流波形可能会失真,功率因数可能会恶化。因此,从功率因数的角度来看,将死区时间设置得过长并非好事。

图18:死区时间长度与电感电流IL的关系

图19表示使死区时间变化时SiC MOSFET的损耗仿真结果。

图19:使死区时间变化时的SiC MOSFET损耗仿真结果

从图中可以看出,当死区时间在50ns以下时,损耗会因流过直通电流而急剧增加。反之,当延长死区时间时,HS SiC MOSFET的体二极管的导通时间会变长,因此在这种条件下损耗也会增加。SiC MOSFET的损耗最小时,正是死区时间最短(没有直通电流)时,在本例中为100ns时。但是,由于开关速度会随温度和批次差异等因素而波动,因此通常需要留100ns左右的余量。也就是说,在这种情况下,200ns是理想的死区时间。

更多回帖