这次幸运的申请到盘古50K开发板,收到板后就开始了紧张的测试,希望能使用这块开发板,实现200M的高速ADC示波器功能。

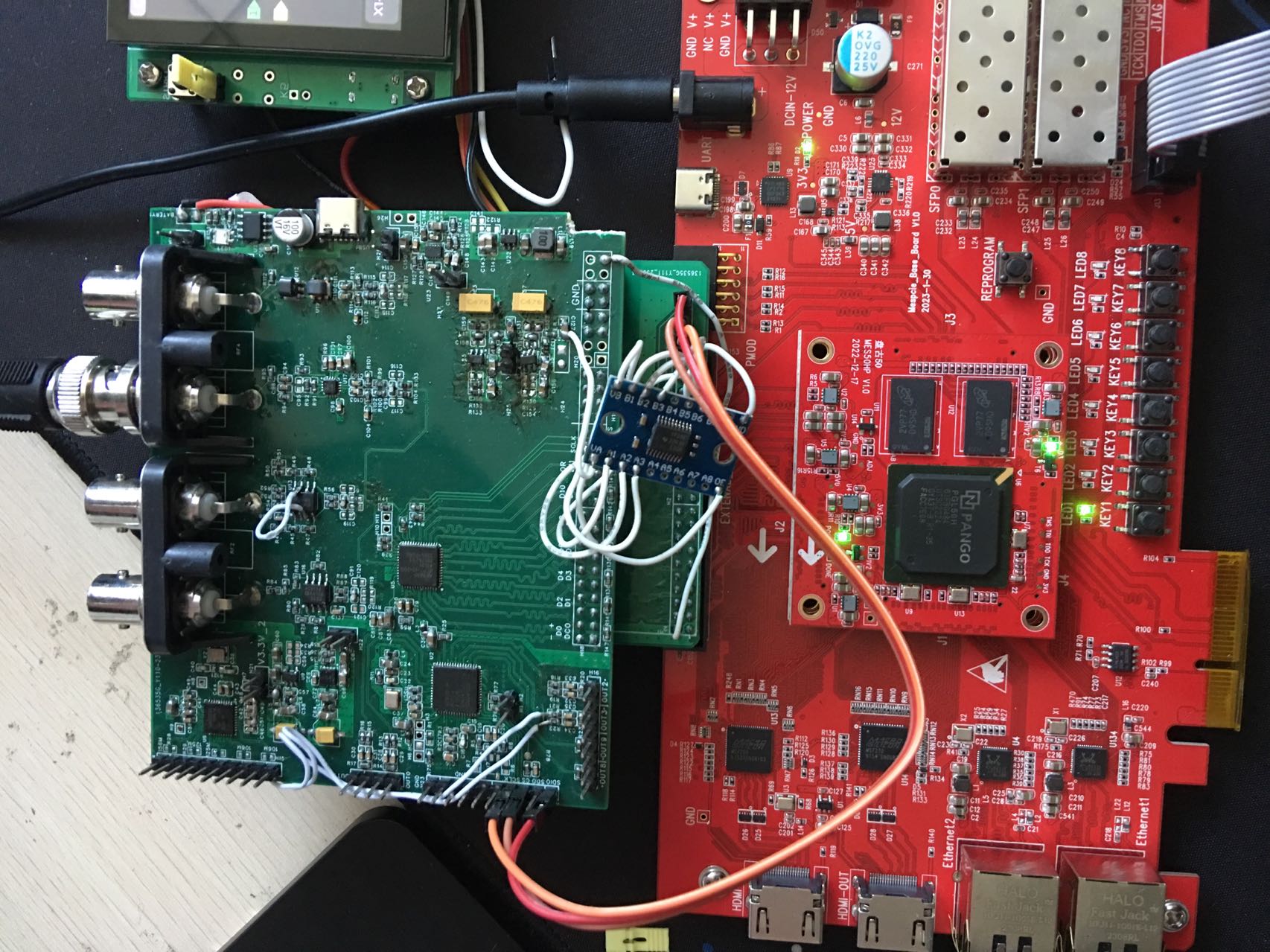

首先看我的ADC采集硬件结构

高速ADC采集板,是自己画的一个板子,以前是用来适配一款小眼睛FPGA推出过的ZYNQ7030的开发板,开发板引出的引脚是1.8V的HP高速I/O。这次为了适配盘古50K开发板,做了一些手工添加,主要是对ADC做SPI配置时,需要从3.3V转到1.8V,添加了电平转换芯片模块。

由于时间比较紧张,采集板就没有重新打样,使用原来的实验板,外观观赏性不太好,还请见谅。性能倒是没什么问题。

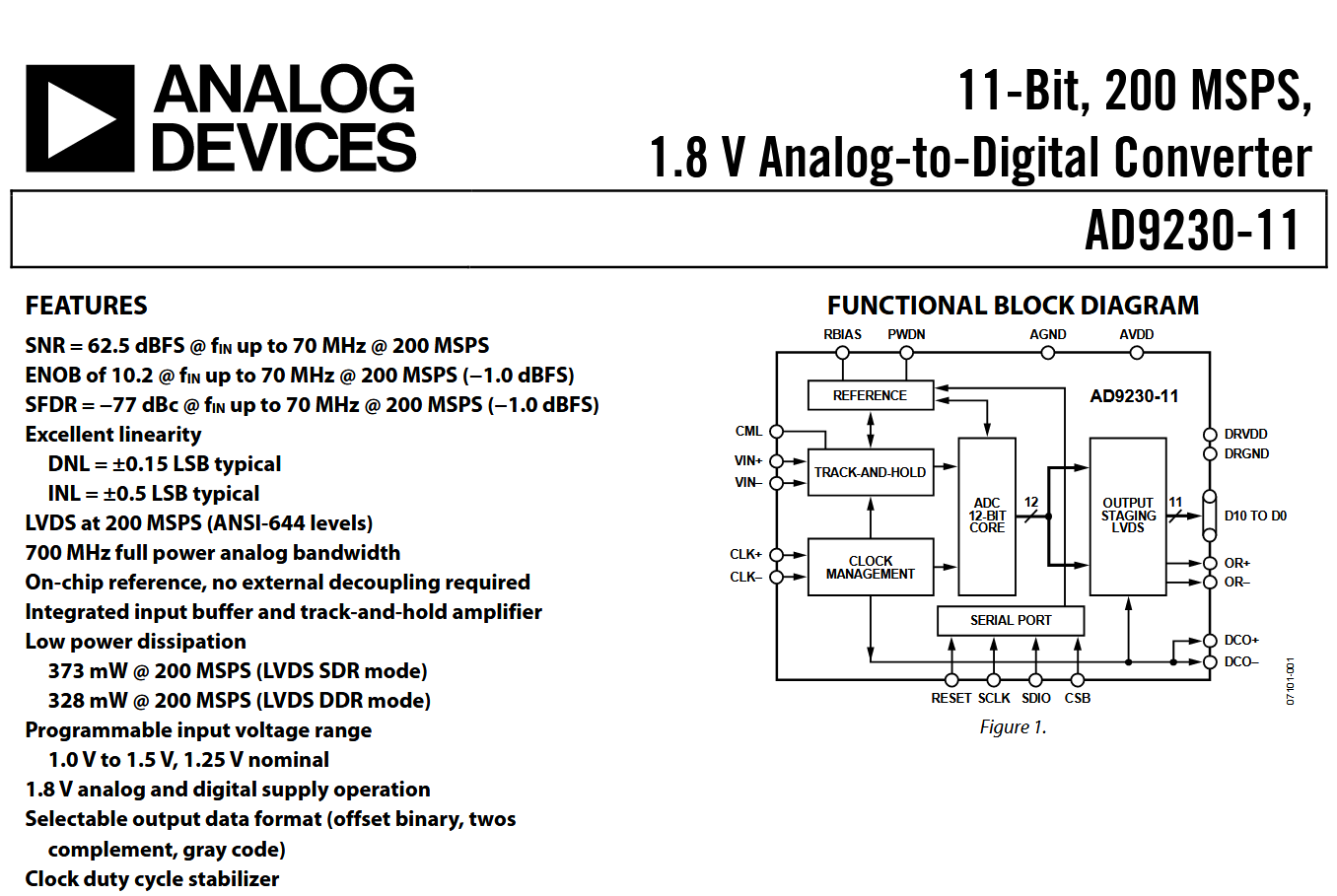

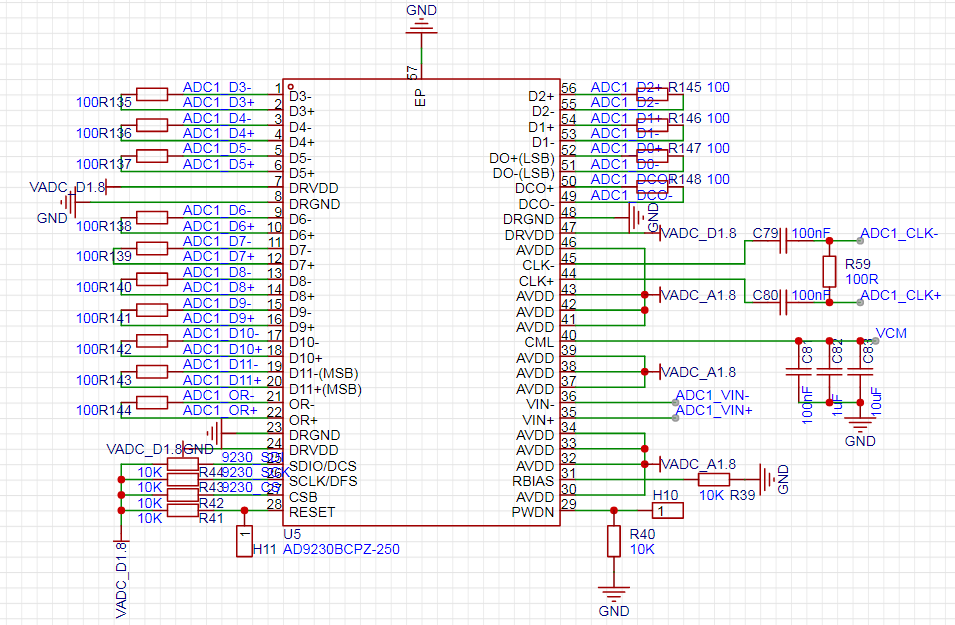

这次使用的是ADI公司的AD9230-11。AD9230-11是一款11位单芯片采样模数转换器(ADC),专门针对高性能、低功耗和易用性进行了优化。该产品的转换速率最高可达200 MSPS,具有出色的动态性能,适合宽带载波和宽带系统使用。芯片上集成了全部必需功能,包括采样保持(T/H)放大器与基准电压源,可提供完整的信号转换解决方案。

该ADC要求采用1.8 V模拟电源供电及差分时钟信号,以便充分发挥其工作性能。数字输出为LVDS (ANSI-644)兼容,支持二进制补码、偏移二进制或格雷码格式。该ADC还提供数据时钟输出,用于正确进行输出数据定时。

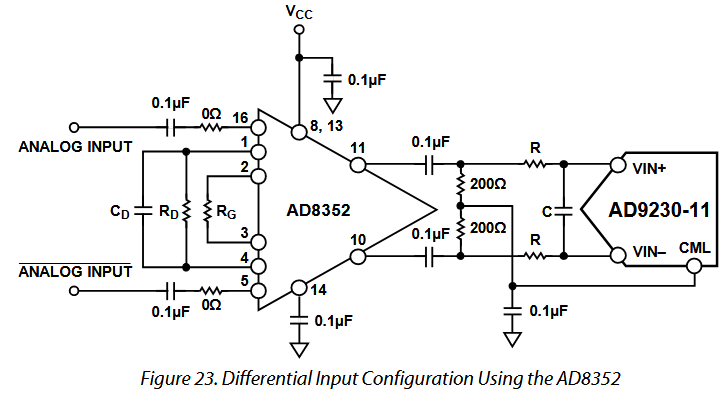

ADC的输入电路使用的是芯片手册上推荐的电路,如AD8138实现的差分输入,也有差分巴伦实现的差分输入,还有AD8352实现的差分输入。在采集板上设置了4通道输入,分别采用不同的芯片实现ADC的差分输入,可以对比各种输入方法的不同特性。

在后续的测试中我选用的是AD8352的输入通道,他的输入电路如下

对于高带宽的应用,ADI是推荐使用这款运放,它兼顾了低频和高频的特性,不像差分巴伦输入时,低频特性很差。

AD9230为实现良好的性能,需要提供稳定的时钟输入,一般的应用中使用FPGA输出时钟给ADC,这样存在的问题就是时钟抖动很大,无法充分实现ADC高速200M采集性能。

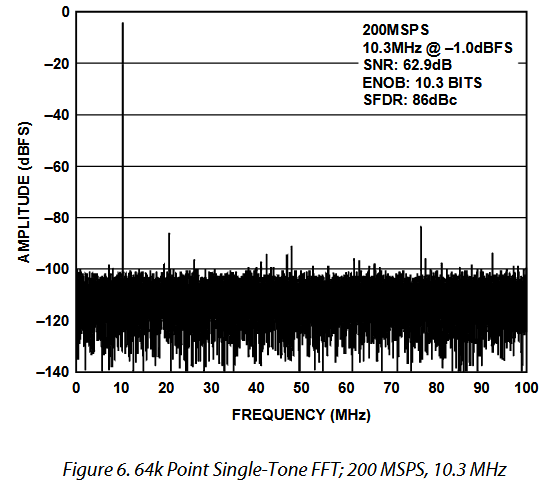

ADI提供的手册中有如下的图:

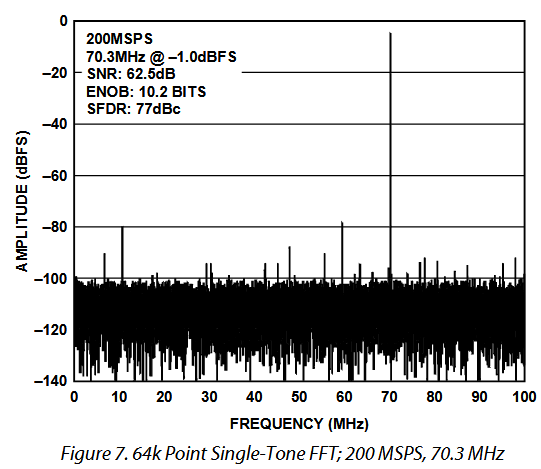

10.3M是的单信号输入能做到SNR为62.9dB,有效位数为10.3bits。

70.3M是的单信号输入能做到SNR为62.5dB,有效位数为10.2bits。

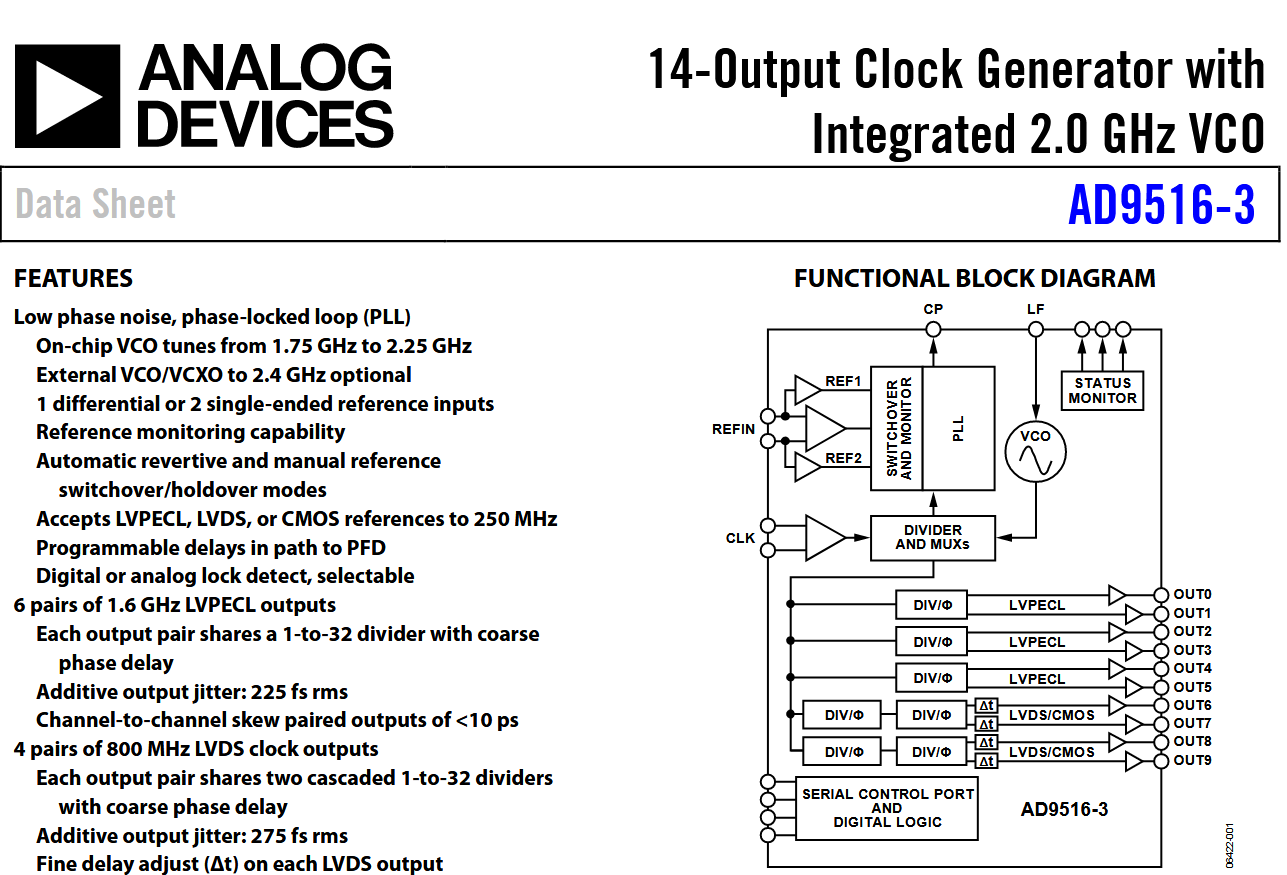

如果是使用FPGA输出的时钟频率,是无法实现上面的性能的,所以这里我使用了一块ADI的AD9516_3,给AD9230提供完美的时钟。

AD9516_3在高速ADC方案中,是很常用的芯片。具体的使用可以到ADI的官网去查询,提供了非常丰富的资料和配置软件。

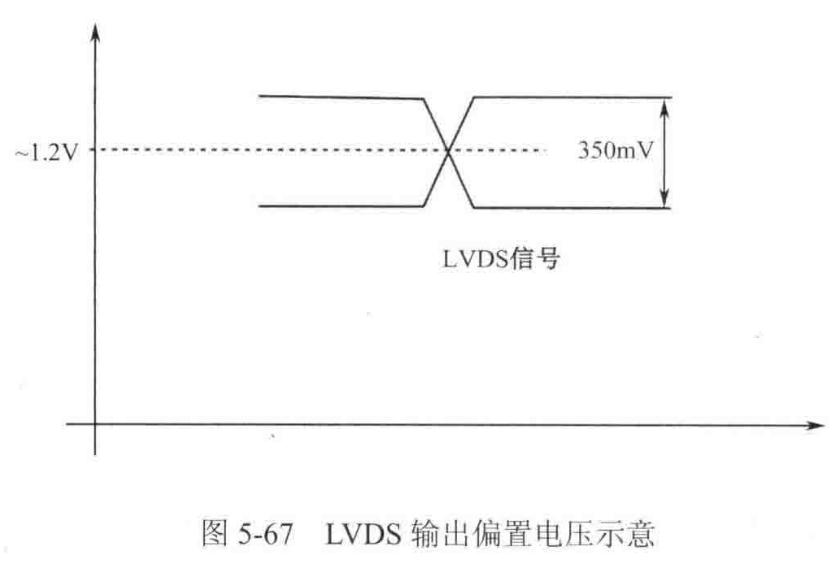

从上面可以知道,AD9230是1.8V供电的,LVDS差分输出的电路。

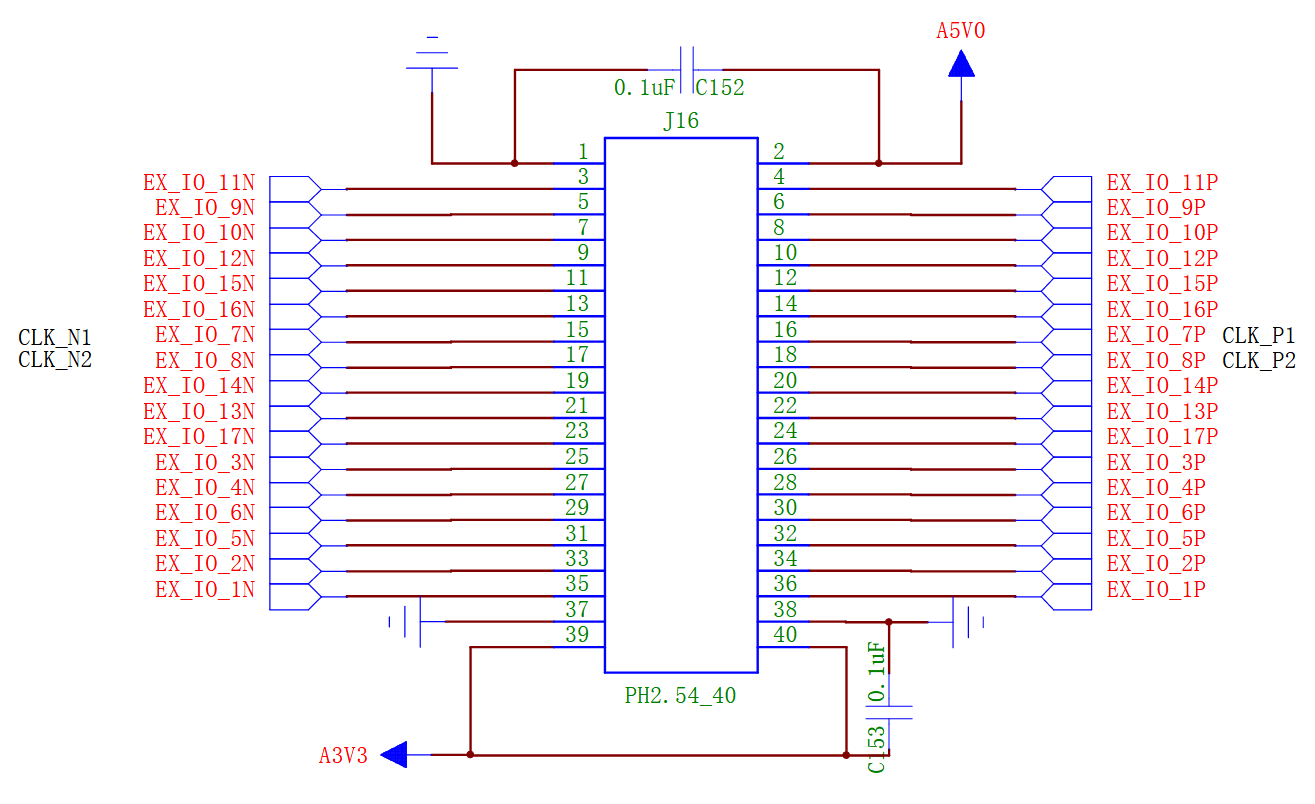

盘古50K开发板提供了一个40PIN的接口,连到PGL50H的bank2上,bank电压是3,3V供电的。

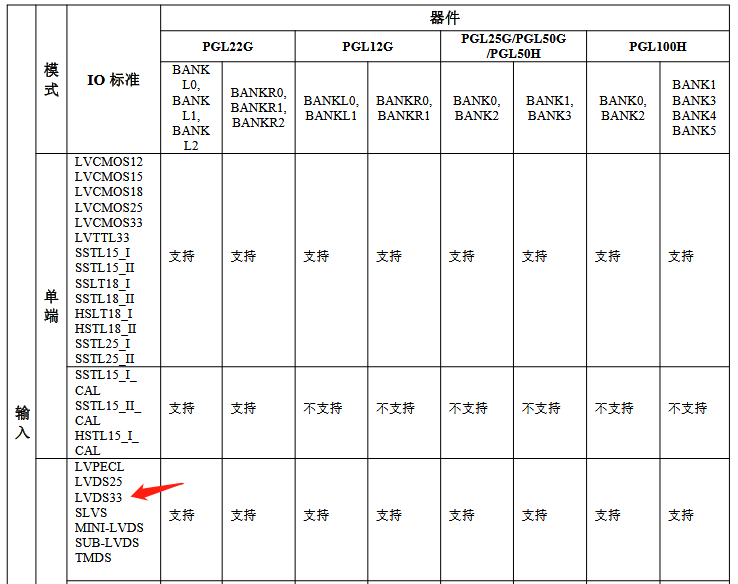

看到这里可能会想,接口电平不匹配,能用吗?这就是紫光同创提供的这款FPGA给我带来的一个小小的惊喜,PGL50H支持LVDS33的电平,这样就完美实现兼容。

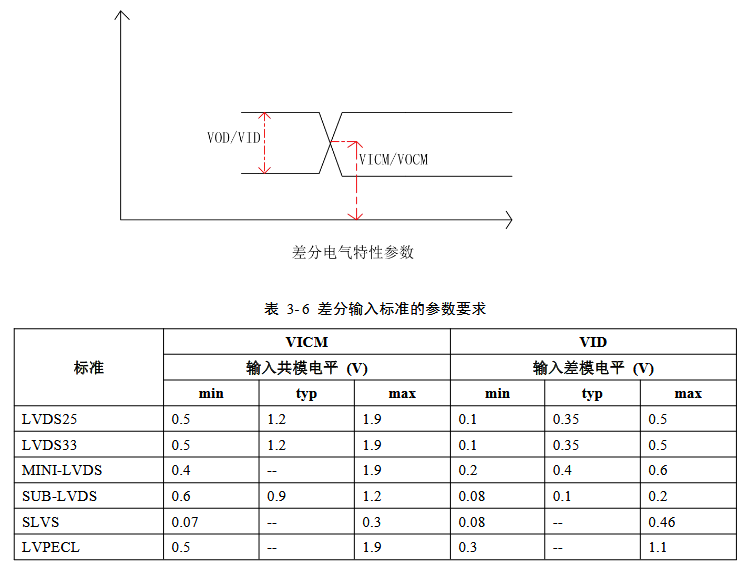

查询紫光最新的数据手册可以看到

支持LVDS33在xilinx的spartan-6的FPGA是支持的,后来xilinx 7系的FPGA改用了HR和HP不同的I/O类型,就不再支持LVDS33。紫光支持LVDS33也是提供了很多的方便。

从手册中提供的电平特性也能看出,可以直接把ADC的LVDS输出直接连到PGL50H的差分输入引脚。

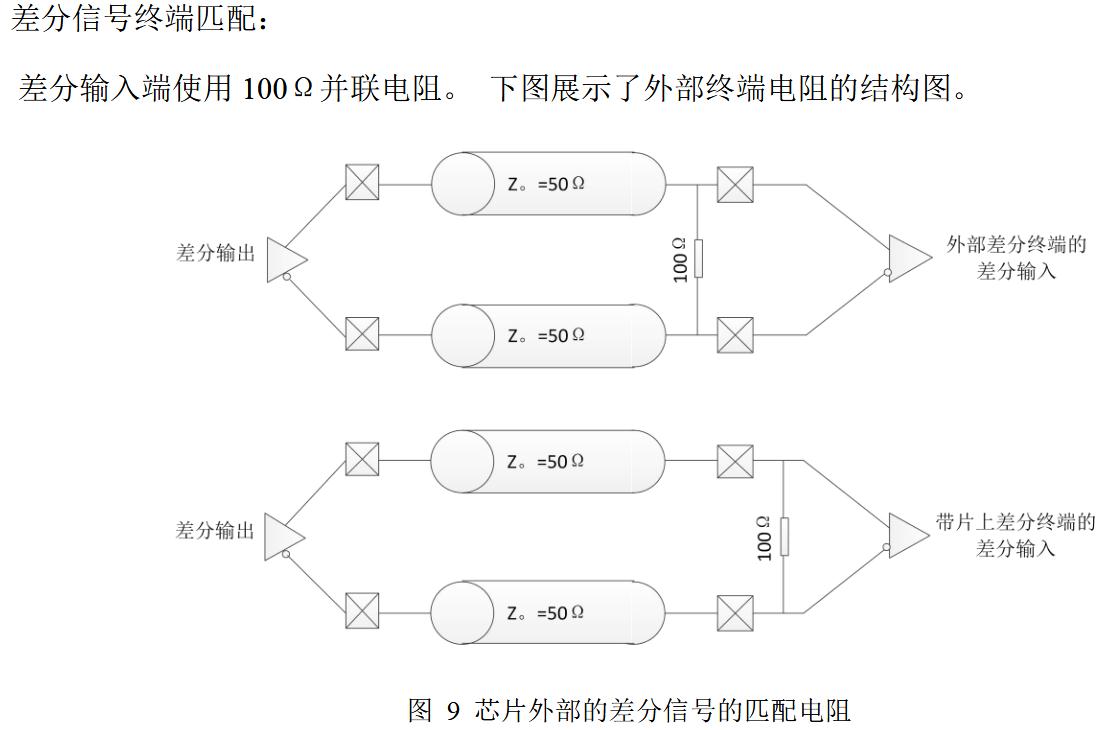

LVDS的连接中要注意100欧的终端电阻,PGL提供了内部终端电阻可以配置使用,也可以使用外部的电阻,我这里使用了外部的电阻,便于调试。

下面是AD9230的原理图部分

盘古50K开发板提供了一个40PIN的接口,连接在PGL50H的Bank2上,连接图如下

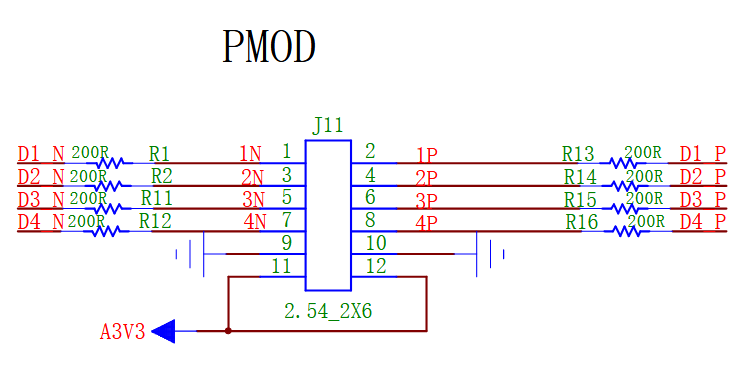

40PIN的接口提供的I/O的数量正好可以驱动AD9230,如果还需要其他的引脚可以使用开发板提供的PMOD接口。

我这里使用了PMOD接口用来连接一个显示屏,用于输出显示波形。

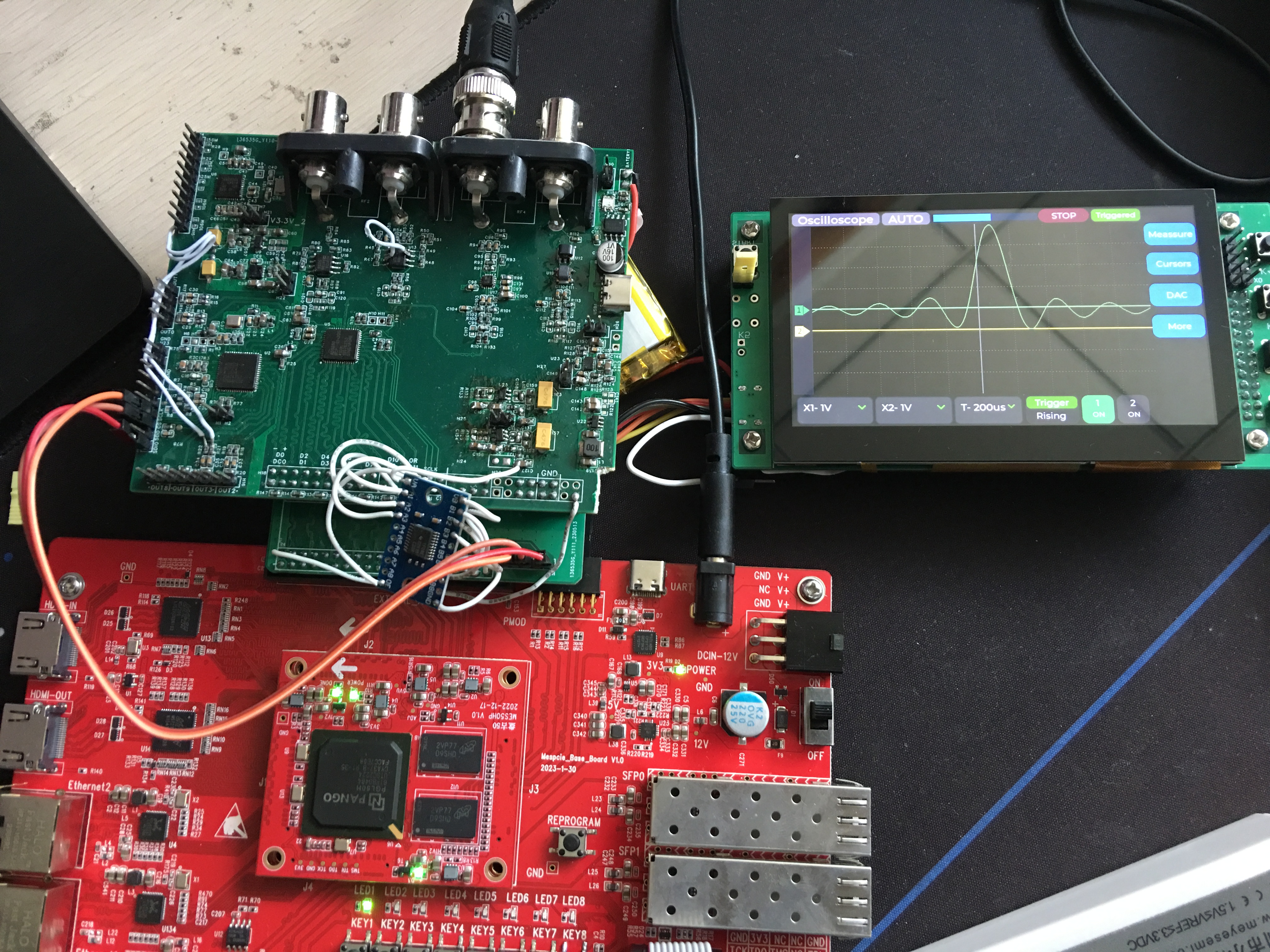

下面的图实现了硬件的基本采集功能,显示屏上显示的是采集到的sinc波形。

更多回帖