转载自博客园网友wahahahehehe

了解RISC-V之前,先熟悉一个概念,指令集架构(Instruction Set Architecture, ISA )。

还记得用C语言的编写的hello world程序吗?

void main(){ printf("Hello, World!");}

该程序在PC、8位MCU、32位MCU这些不同的平台上都能正常运行,这是为什么呢?

答案就是有一套标准规范,正因为编译器和芯片设计时都遵循这套规范,使得高级语言编写的程序经指定编译器编译后能直接运行在对应的芯片上。

这套标准规范就是 指令集架构 (Instruction Set Architecture,ISA)。

ISA主要分为复杂指令集(Complex Instruction Set Computer,CISC)和精简指令集(Reduced Instruction Set Computer,RISC),典型代表如下:

| 类型 | 名称 | 特点 | 应用领域 |

|---|---|---|---|

| 复杂指令集CISC | x86 | 性能高速度快兼容性好 | PC服务器 |

| 精简指令集RISC | ARM | 生态成熟非离散需授权 | 移动设备嵌入式设备 |

| RISC-V | 开源模块化简洁可拓展 | 物联网人工智能边缘计算 |

ISA是底层硬件电路面向上层软件程序提供的一层 接口规范 ,即机器语言程序所运行的计算机硬件和软件之间的“ 桥梁 ”。ISA主要定义了如下内容:

ISA规定了机器级程序的格式和行为,即ISA具有软件看得见(能感觉到)的特性,因此用机器指令或汇编指令编写机器级程序时,必须熟悉对应平台的ISA。不过程序员大多使用高级语言(C/C++、Java)编写程序,由工具链编译转换为对应的机器语言,不需要了解ISA和底层硬件的执行机理。

RISC由美国加州大学伯克利分校教授David Patterson发明。

RISC-V (读作”risk-five“),表示第五代精简指令集,起源于2010年伯克利大学并行计算实验室(Par Lab) 的1位教授和2个研究生的一个项目(该项目也由David Patterson指导),希望选择一款指令集用于科研和教学,该项目在x86、ARM等指令集架构中徘徊,最终决定自己设计一个全新的指令集,RISC-V由此诞生。RISC-V的最初目标是实用、开源、可在学术上使用,并且在任何硬件或软件设计中部署时无需版税。

2015年,为了更好的推动RISC-V在技术和商业上的发展,3位创始人做了如下安排:

2019年,RISC-V基金会宣布将总部迁往瑞士,改名 RISC-V国际基金会 。作为全球性非营利组织,已在全球70多个国家拥有 2000+ 成员。包括华为、中兴、阿里巴巴、沁恒微电子、乐鑫等众多国内企业。

通过十多年的发展,RISC-V这一星星之火已有燎原之势。倪光南院士表示,未来RISC-V很可能发展成为世界主流CPU之一,从而在CPU领域形成Intel (x86)、ARM、RISC-V三分天下的格局。

RISC-V 指令集规范官方下载地址:https://riscv.org/technical/specifications/

(1)模块化的指令子集

RISC-V指令集采用模块化的方式进行组织设计,由基本指令集和扩展指令集组成,每个模块用一个英文字母表示。

其中,整数(Integer)指令集用字母“ I ”表示,这是RISC-V处理器最基本也是唯一强制要求实现的指令集。其他指令集均为可选模块,可自行选择是否支持。

RISC-V指令模块描述如下:

| 类型 | 指令集 | 指令数 | 状态 | 描述 |

|---|---|---|---|---|

| 基本指令集 | RV32I | 47 | 批准 | 32位地址与整数指令支持32个通用寄存器 |

| RV32E | 47 | 草稿 | RV32I的子集支持16个通用寄存器 | |

| RV64I | 59 | 批准 | 64位地址与整数指令集及部分32位整数指令支持32个通用寄存器 | |

| RV128I | 71 | 草稿 | 128位地址与整数指令集及部分64位和32位整数指令支持32个通用寄存器 | |

| 扩展指令集 | M | 8 | 批准 | 乘法(Multiplication)与除法指令 |

| A | 11 | 批准 | 存储器原子(Automic)操作指令 | |

| F | 26 | 批准 | 单精度(32bit)浮点(Float)运算指令 | |

| D | 26 | 批准 | 双精度(64bit)浮点(Double)运算指令 | |

| C | 46 | 批准 | 压缩(Compressed)指令,指令长度位16bit | |

| Zicsr | 6 | 批准 | 控制和状态寄存器访问指令 |

上表基于20191213版非特权指令集规范手册,最新指令模块说明参考官网:https://riscv.org/technical/specifications/

通常把模块“ I ”、“ M ”、“ A ”、 “F ”和“ D ”的特定组合“ IMAFD ”称为通用组合(General),用字母“ G ”表示。如用RV32G表示RV32IMAFD。

(2)可配置的寄存器

RV32I支持32个通用寄存器x0~x31,每个寄存器长度均为32位,其中寄存器x0恒为0,剩余31个为任意读/写的通用寄存器。

为了增加汇编程序的阅读性,汇编编程时通常采用应用程序二进制接口协议(Application Binary Interface,ABI)定义的寄存器名称。

RV32I通用寄存器如下:

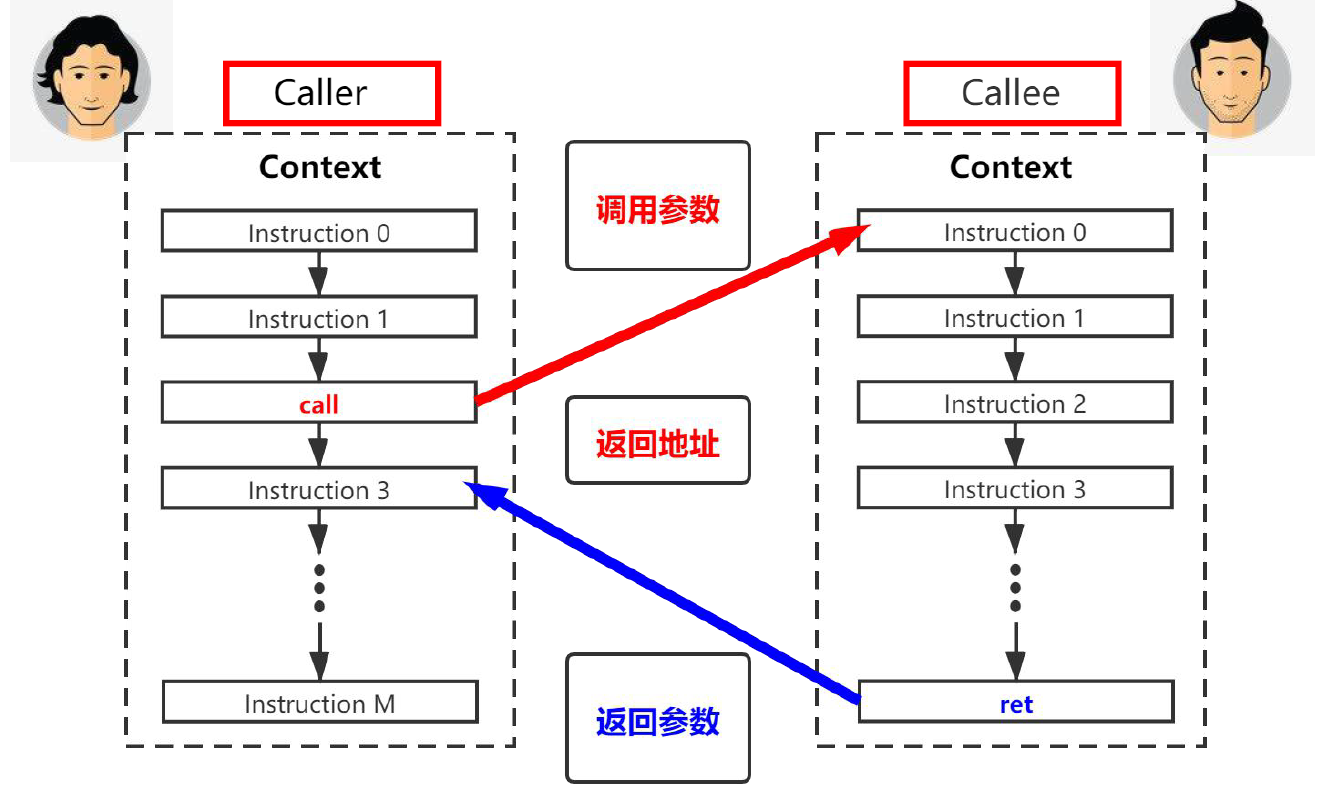

| 寄存器名称 | ABI名称 | 说明 | 存储者 |

|---|---|---|---|

| x0 | zero | 读取时总为0,写入时不起任何效果 | N/A |

| x1 | ra | 程序返回地址 | Caller |

| x2 | sp | 栈空间指针 | callee |

| x3 | gp | 全局变量指针(基地址) | / |

| x4 | tp | 线程变量指针(基地址) | / |

| x5 ~ x7 | t0 ~ t2 | 临时寄存器 | Caller |

| x8 | s0/fp | 保存寄存器/帧指针(配合栈指针界定函数栈) | Callee |

| x9 | s1 | 保存寄存器(被调用函数使用时需备份并在退出时恢复) | Callee |

| x10, x11 | a0, a1 | 函数参数寄存器(用于函数参数/返回值) | Caller |

| x12 ~ x17 | a2 ~ a7 | 函数参数寄存器(用于函数参数) | Caller |

| x18 ~ x27 | s2 ~ s11 | 保存寄存器(被调用函数使用时需备份并在退出时恢复) | Callee |

| x28 ~ x31 | t3 ~ t6 | 临时寄存器 | Caller |

此外,RISC-V还定义了一组控制和状态寄存器(Control and Status Registers, CSR ),用于记录内核运行状态。详情参考特权指令集规范:https://riscv.org/technical/specifications/

**(3)特权级别 **

RISC-V规定如下四个特权级别(privilege level):

| 等级(Level) | 编码(Encoding) | 名称(Name) | 缩写(Abbreviation) |

|---|---|---|---|

| 0 | 00 | 用户/应用模式(User/Application) | U |

| 1 | 01 | 管理员模式(Supervisor ) | S |

| 2 | 10 | Reserved | - |

| 3 | 11 | 机器模式(Machine) | M |

通过不同特权模式的组合,可设计面向不同应用场景的处理器,如:

| 模式数量 | 支持模式 | 目标应用 |

|---|---|---|

| 1 | M | 简单嵌入式系统 |

| 2 | M,U | 安全嵌入式系统 |

| 3 | M,S,U | 支持Unix、Linux、Windows等操作系统 |

沁恒微电子从2017年开始关注并研究RISC-V开源指令集的32位MCU架构,针对快速中断响应、高带宽数据DMA进行优化,自定义压缩指令,研发设计硬件压栈(HPE,Hardware Prologue/Epilogue),并创新性提出免表中断(VTF,Vector Table Free)技术,即免查表方式中断寻址技术,同时引入两线仿真调试接口。

目前已形成了侧重于低功耗或高性能等多个版本的RISC-V处理器。特点如下:

| Core | 特点 |

|---|---|

| 支持指令 | 流水线 |

| V2A | RV32EC |

| V3A | RV32IMAC |

| V4A | RV32IMAC |

| V4B | RV32IMAC |

| V4C | RV32IMAC |

| V4F | RV32IMAFC |

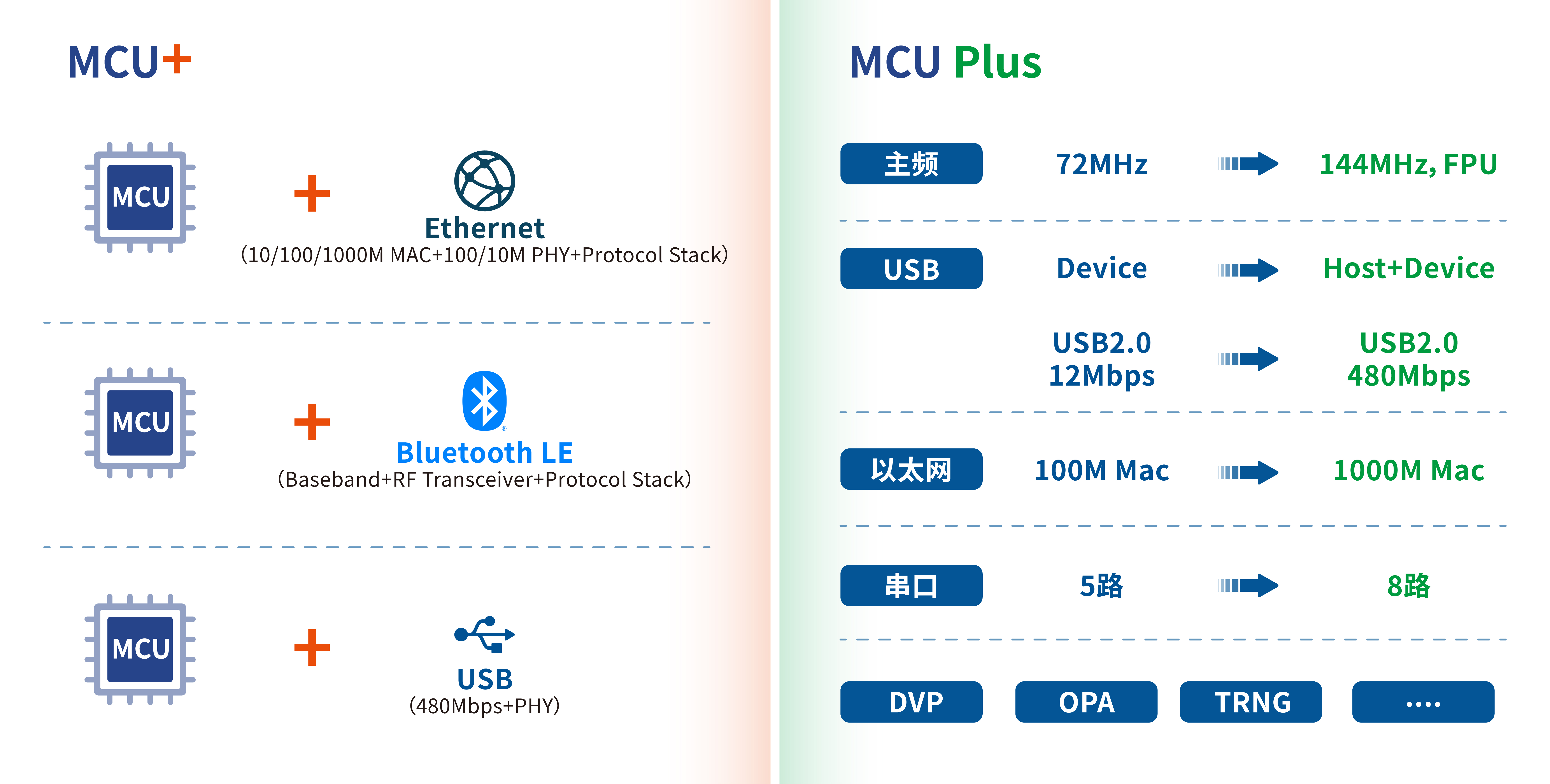

沁恒微电子结合多年USB、低功耗蓝牙、以太网等接口的设计经验,基于多款自研RISC-V处理器,并基于32位通用MCU架构外加USB高速PHY、蓝牙收发器、以太网PHY等专业接口模块推出增强版MCU+系列产品。

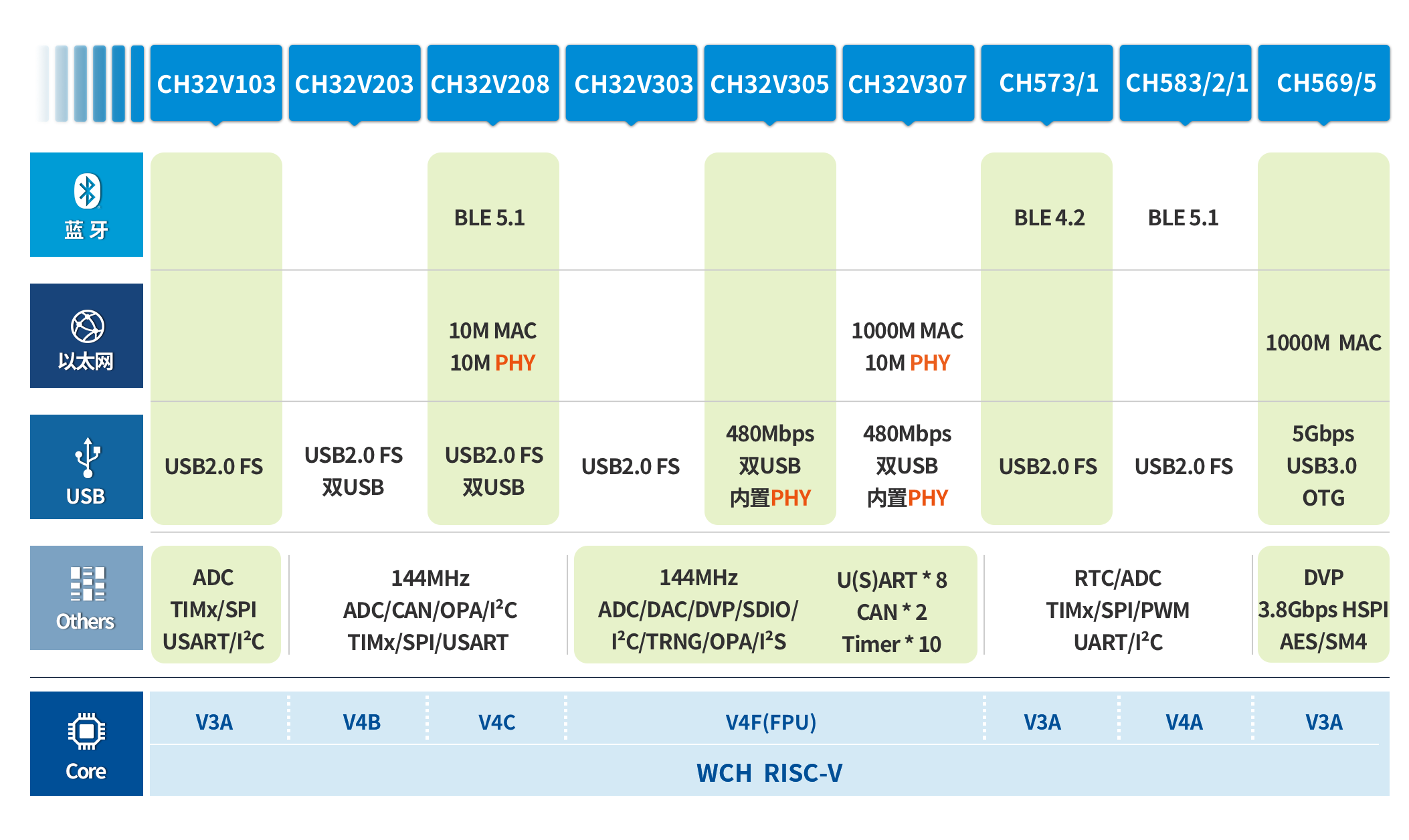

沁恒RISC-V系列MCU Roadmap如下:

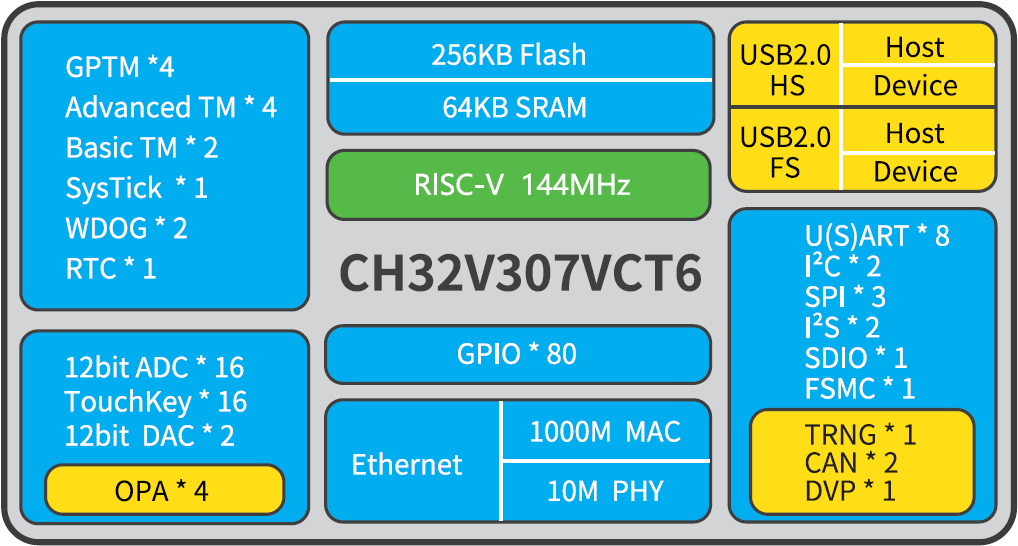

本教程基于沁恒微电子工业级互联型RISC-V MCU CH32V307,通过讲解RISC-V常用汇编指令,分析CH32V307的每个外设功能及使用方法,配合详细的示例代码,帮助大家熟悉RISC-V平台的嵌入式开发。

CH32V307配备了硬件堆栈区、快速中断入口,在标准RISC-V基础上大大提高了中断响应速度。加入单精度浮点指令集,扩充堆栈区,具有更高的运算性能。扩展串口U(S)ART数量到8组,电机定时器到4组。提供USB2.0高速接口(480Mbps)并内置了PHY收发器,以太网MAC升级到千兆并集成了10M-PHY模块。

详细参数如下:

沁恒官网资料下载:

更多回帖