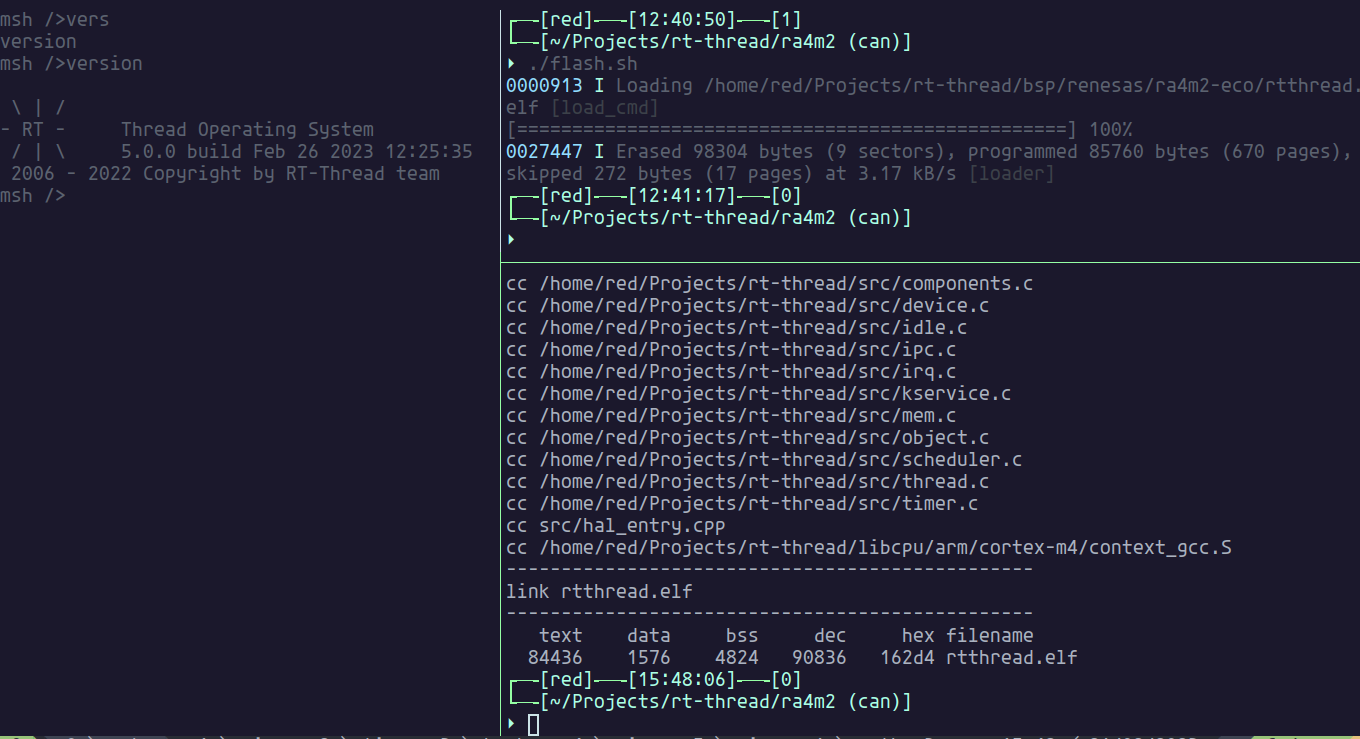

因为官方 RT-Thread 仓库有 bsp/renesas/ra4m2-eco/ 路径,但是发现在 linux 平台无法直接编译通过,缺少连接文件等等.目前这部分修改我 push 到了 我 fork 的 rt-thread 仓库.感兴趣的同学可以看下 can 分支.

最开始尝试使用 openocd 进行烧录,经过一番搜集资料,最后只能实现擦除操作,但是无法正常写入.后来转为使用 pyocd 进行烧录,这部分需要感谢 [url=home.php?mod=space&uid=3623068]@知之为知之zhl[/url] 的文章 【RA4M2设计挑战赛】开发板开箱、资料获取、开发环境搭建

pack:

- ./tools/Renesas.RA_DFP.4.2.0.pack

pyocd flash --target=R7FA4M2AD --erase=auto --frequency=1000000 rtthread.elf这里主要碰到了三个问题:

但是如果要保证 PCLKA 为 100MHz,经过测试,选择使用 HOCO 时钟源(内部高速时钟),具体 patch 为:

diff --git a/bsp/renesas/ra4m2-eco/ra_gen/bsp_clock_cfg.h b/bsp/renesas/ra4m2-eco/ra_gen/bsp_clock_cfg.h

index 585e51190..9895f8649 100644

--- a/bsp/renesas/ra4m2-eco/ra_gen/bsp_clock_cfg.h

+++ b/bsp/renesas/ra4m2-eco/ra_gen/bsp_clock_cfg.h

[url=home.php?mod=space&uid=1999721]@@[/url] -3,18 +3,22 @@

#define BSP_CLOCK_CFG_H_

#define BSP_CFG_CLOCKS_SECURE (0)

#define BSP_CFG_CLOCKS_OVERRIDE (0)

-#define BSP_CFG_XTAL_HZ (24000000) /* XTAL 24000000Hz */

+#define BSP_CFG_XTAL_HZ (12000000) /* XTAL 12000000Hz */

#define BSP_CFG_HOCO_FREQUENCY (2) /* HOCO 20MHz */

-#define BSP_CFG_PLL_SOURCE (BSP_CLOCKS_SOURCE_CLOCK_MAIN_OSC) /* PLL Src: XTAL */

-#define BSP_CFG_PLL_DIV (BSP_CLOCKS_PLL_DIV_3) /* PLL Div /3 */

-#define BSP_CFG_PLL_MUL BSP_CLOCKS_PLL_MUL(25U,0U) /* PLL Mul x25.0 */

+#define BSP_CFG_PLL_SOURCE (BSP_CLOCKS_SOURCE_CLOCK_HOCO) /* PLL Src: XTAL 使用外部晶振作为 pll 时钟源 */

+#define BSP_CFG_PLL_DIV (BSP_CLOCKS_PLL_DIV_1) /* PLL Div /3 */

+#define BSP_CFG_PLL_MUL BSP_CLOCKS_PLL_MUL(10U,0U) /* PLL Mul x25.0 */

+

串口无法输入,只能输出,这里涉及到两个问题

diff --git a/bsp/renesas/ra4m2-eco/script/fsp.ld b/bsp/renesas/ra4m2-eco/script/fsp.ld

index 2f97f05c5..f09a78a9a 100644

--- a/bsp/renesas/ra4m2-eco/script/fsp.ld

+++ b/bsp/renesas/ra4m2-eco/script/fsp.ld

@@ -171,6 +171,22 @@ SECTIONS

KEEP(*(.init))

KEEP(*(.fini))

+ /* section information for finsh shell */

+ . = ALIGN(4);

+ __fsymtab_start = .;

+ KEEP(*(FSymTab))

+ __fsymtab_end = .;

+

+ . = ALIGN(4);

+ __vsymtab_start = .;

+ KEEP(*(VSymTab))

+ __vsymtab_end = .;

+

+ . = ALIGN(4);

+ __rt_init_start = .;

+ KEEP(*(SORT(.rti_fn*)))

+ __rt_init_end = .;

+

/* .ctors */

*crtbegin.o(.ctors)

*crtbegin?.o(.ctors)

diff --git a/bsp/renesas/ra4m2-eco/ra_gen/hal_data.c b/bsp/renesas/ra4m2-eco/ra_gen/hal_data.c

index 7f964d9ef..c788f8568 100644

--- a/bsp/renesas/ra4m2-eco/ra_gen/hal_data.c

+++ b/bsp/renesas/ra4m2-eco/ra_gen/hal_data.c

@@ -78,46 +78,6 @@ const sci_spi_extended_cfg_t g_sci_spi9_cfg_extend =

}

};

-const spi_cfg_t g_sci_spi9_cfg =

-{

- .channel = 9,

- .operating_mode = SPI_MODE_MASTER,

- .clk_phase = SPI_CLK_PHASE_EDGE_ODD,

- .clk_polarity = SPI_CLK_POLARITY_LOW,

- .mode_fault = SPI_MODE_FAULT_ERROR_DISABLE,

- .bit_order = SPI_BIT_ORDER_MSB_FIRST,

-#define RA_NOT_DEFINED (1)

-#if (RA_NOT_DEFINED == g_transfer0)

- .p_transfer_tx = NULL,

-#else

- .p_transfer_tx = &g_transfer0,

-#endif

-#if (RA_NOT_DEFINED == g_transfer1)

- .p_transfer_rx = NULL,

-#else

- .p_transfer_rx = &g_transfer1,

-#endif

-#undef RA_NOT_DEFINED

- .p_callback = sci_spi9_callback,

- .p_context = NULL,

- .rxi_irq = VECTOR_NUMBER_SCI9_RXI,

- .txi_irq = VECTOR_NUMBER_SCI9_TXI,

- .tei_irq = VECTOR_NUMBER_SCI9_TEI,

- .eri_irq = VECTOR_NUMBER_SCI9_ERI,

- .rxi_ipl = (12),

- .txi_ipl = (12),

- .tei_ipl = (12),

- .eri_ipl = (12),

- .p_extend = &g_sci_spi9_cfg_extend,

-};

-/* Instance structure to use this module. */

-const spi_instance_t g_sci_spi9 =

-{

- .p_ctrl = &g_sci_spi9_ctrl,

- .p_cfg = &g_sci_spi9_cfg,

- .p_api = &g_spi_on_sci

-};

-

sci_uart_instance_ctrl_t g_uart9_ctrl;

baud_setting_t g_uart9_baud_setting =

@@ -176,23 +136,23 @@ sci_uart_instance_ctrl_t g_uart9_ctrl;

.txi_ipl = (12),

.tei_ipl = (12),

.eri_ipl = (12),

-#if defined(VECTOR_NUMBER_SCI4_RXI)

- .rxi_irq = VECTOR_NUMBER_SCI4_RXI,

+#if defined(VECTOR_NUMBER_SCI9_RXI)

+ .rxi_irq = VECTOR_NUMBER_SCI9_RXI,

#else

.rxi_irq = FSP_INVALID_VECTOR,

#endif

-#if defined(VECTOR_NUMBER_SCI4_TXI)

- .txi_irq = VECTOR_NUMBER_SCI4_TXI,

+#if defined(VECTOR_NUMBER_SCI9_TXI)

+ .txi_irq = VECTOR_NUMBER_SCI9_TXI,

#else

.txi_irq = FSP_INVALID_VECTOR,

#endif

-#if defined(VECTOR_NUMBER_SCI4_TEI)

- .tei_irq = VECTOR_NUMBER_SCI4_TEI,

+#if defined(VECTOR_NUMBER_SCI9_TEI)

+ .tei_irq = VECTOR_NUMBER_SCI9_TEI,

#else

.tei_irq = FSP_INVALID_VECTOR,

#endif

-#if defined(VECTOR_NUMBER_SCI4_ERI)

- .eri_irq = VECTOR_NUMBER_SCI4_ERI,

+#if defined(VECTOR_NUMBER_SCI9_ERI)

+ .eri_irq = VECTOR_NUMBER_SCI9_ERI,

#else

.eri_irq = FSP_INVALID_VECTOR,

#endif

diff --git a/bsp/renesas/ra4m2-eco/ra_gen/vector_data.c b/bsp/renesas/ra4m2-eco/ra_gen/vector_data.c

index 55ac127a1..19f650cba 100644

--- a/bsp/renesas/ra4m2-eco/ra_gen/vector_data.c

+++ b/bsp/renesas/ra4m2-eco/ra_gen/vector_data.c

@@ -4,7 +4,7 @@

#if VECTOR_DATA_IRQ_COUNT > 0

BSP_DONT_REMOVE const fsp_vector_t g_vector_table[BSP_ICU_VECTOR_MAX_ENTRIES] BSP_PLACE_IN_SECTION(BSP_SECTION_APPLICATION_VECTORS) =

{

- [0] = sci_uart_rxi_isr, /* SCI0 RXI (Receive data full) */

+ [0] = sci_uart_rxi_isr, /* SCI0 RXI (Receive data full) */

[1] = sci_uart_txi_isr, /* SCI0 TXI (Transmit data empty) */

[2] = sci_uart_tei_isr, /* SCI0 TEI (Transmit end) */

[3] = sci_uart_eri_isr, /* SCI0 ERI (Receive error) */

@@ -12,10 +12,10 @@

[5] = sci_uart_txi_isr, /* SCI4 TXI (Transmit data empty) */

[6] = sci_uart_tei_isr, /* SCI4 TEI (Transmit end) */

[7] = sci_uart_eri_isr, /* SCI4 ERI (Receive error) */

- [8] = sci_spi_rxi_isr, /* SCI9 RXI (Received data full) */

- [9] = sci_spi_txi_isr, /* SCI9 TXI (Transmit data empty) */

- [10] = sci_spi_tei_isr, /* SCI9 TEI (Transmit end) */

- [11] = sci_spi_eri_isr, /* SCI9 ERI (Receive error) */

+ [8] = sci_uart_rxi_isr, /* SCI9 RXI (Received data full) */

+ [9] = sci_uart_txi_isr, /* SCI9 TXI (Transmit data empty) */

+ [10] = sci_uart_tei_isr, /* SCI9 TEI (Transmit end) */

+ [11] = sci_uart_eri_isr, /* SCI9 ERI (Receive error) */

};

const bsp_interrupt_event_t g_interrupt_event_link_select[BSP_ICU_VECTOR_MAX_ENTRIES] =

{

@@ -32,4 +32,4 @@

[10] = BSP_PRV_IELS_ENUM(EVENT_SCI9_TEI), /* SCI9 TEI (Transmit end) */

[11] = BSP_PRV_IELS_ENUM(EVENT_SCI9_ERI), /* SCI9 ERI (Receive error) */

};

- #endif

\ No newline at end of file

+ #endif

diff --git a/bsp/renesas/ra4m2-eco/ra_gen/vector_data.h b/bsp/renesas/ra4m2-eco/ra_gen/vector_data.h

index 50341d279..178048a6c 100644

--- a/bsp/renesas/ra4m2-eco/ra_gen/vector_data.h

+++ b/bsp/renesas/ra4m2-eco/ra_gen/vector_data.h

@@ -13,10 +13,6 @@

void sci_uart_txi_isr(void);

void sci_uart_tei_isr(void);

void sci_uart_eri_isr(void);

- void sci_spi_rxi_isr(void);

- void sci_spi_txi_isr(void);

- void sci_spi_tei_isr(void);

- void sci_spi_eri_isr(void);

/* Vector table allocations */

#define VECTOR_NUMBER_SCI0_RXI ((IRQn_Type) 0) /* SCI0 RXI (Receive data full) */

@@ -46,4 +42,4 @@

#ifdef __cplusplus

}

#endif

- #endif /* VECTOR_DATA_H */

\ No newline at end of file

+ #endif /* VECTOR_DATA_H */

更多回帖