前言

大家好,非常感谢电子发烧友与正点原子提供的DFPGL22G开发板,这是正点原子基于国产FPGA厂商紫光同创设计的开发板。

我是大学是信息工程专业,毕业从事多年的单片机方向开发工作,FPGA虽然大学的时候学过这方面的课程,基于Quartus软件开发环境开发Altera的芯片,学的还是VHDL语言,但是有10多年没有用过FPGA,很多的知识差不多也全忘记了。

FPGA开发知识储备

在发烧友“短短管理员”通知我成功试用的时候,我就在开始逐步的学习这方面知识和查看开发板的相关资料。

对于我来说,FPGA的基本知识概念我还有一些映像,但是硬件描述语法这些我是全忘了,加上大学学的是VHDL,而紫光这款芯片和官方EDA软件支持的是Verilog开发语言。

所以我首先需要学习Verilog语法,好在这个语法与C还是有一定的相似性,所以上手不难,但是想要学精,那是必须得下一番苦功夫。

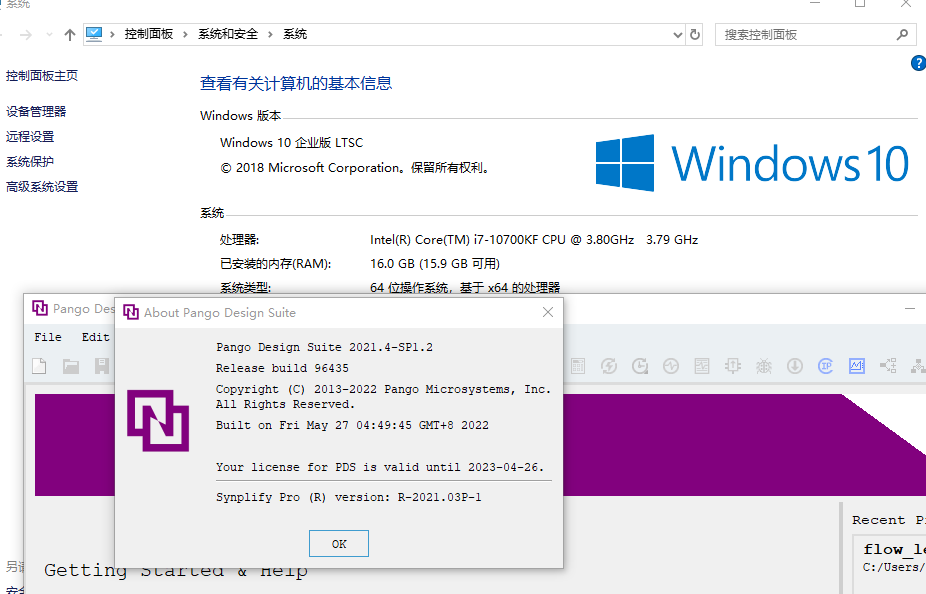

另外就是紫光的PDS软件使用了,这软件使用的是WIN7-64位,毕竟这种专业软件更新的本来就慢。但是WIN10好像也能使用,我在WIN10的电脑上也安装一次,能正常安装。

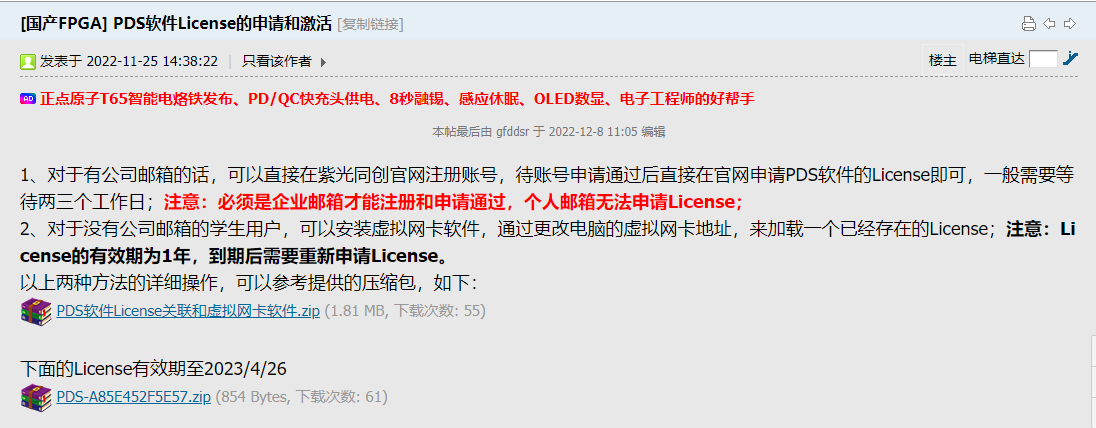

另外就是紫光PDS软件的License,虽然申请License是免费的,但是官方要求必须使用企业邮箱或者教育邮箱才行,而我这边目前没有个人的企业邮箱。

正在范畴之际,看到正点原子的论坛,里面有一个解决方法,可以用一个别人申请的License,因为License是与网卡的MAC地址绑定的,所以需要安装一个虚拟网卡软件,模拟出一个特定MAC地址的网卡。具体的操作方法详见如下链接。

openedv论坛

唯一比较遗憾的是,这个License在2023年4月23有效期就要到期了,还能用几个月,就先这么用着吧。

先学Verilog语法

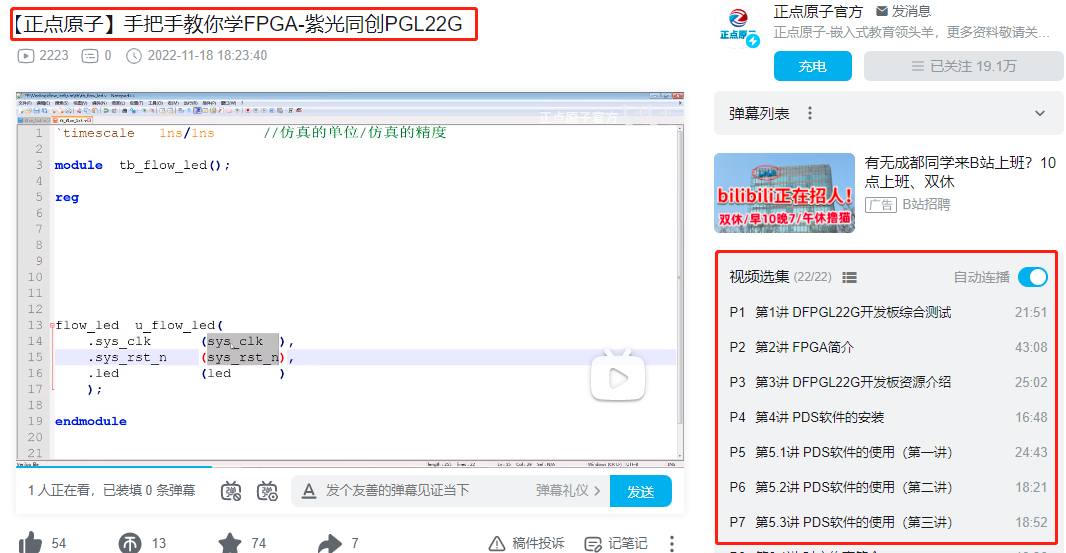

我的学习历程是,先在B站上把正点原子的这款开发板的视频全看了一遍。视频也不多,对于Verilog语法讲解更是只有5个视频。看完正点原子的视频之后,开发环境搭建好了,对FPGA开发流程有了一个基本认知。

但是正点原子的视频看完,感觉在语法方面,写个LED流水灯,写个38译码器应该是没问题,但是下一步用FPGA做什么,感觉就有点迷茫了。

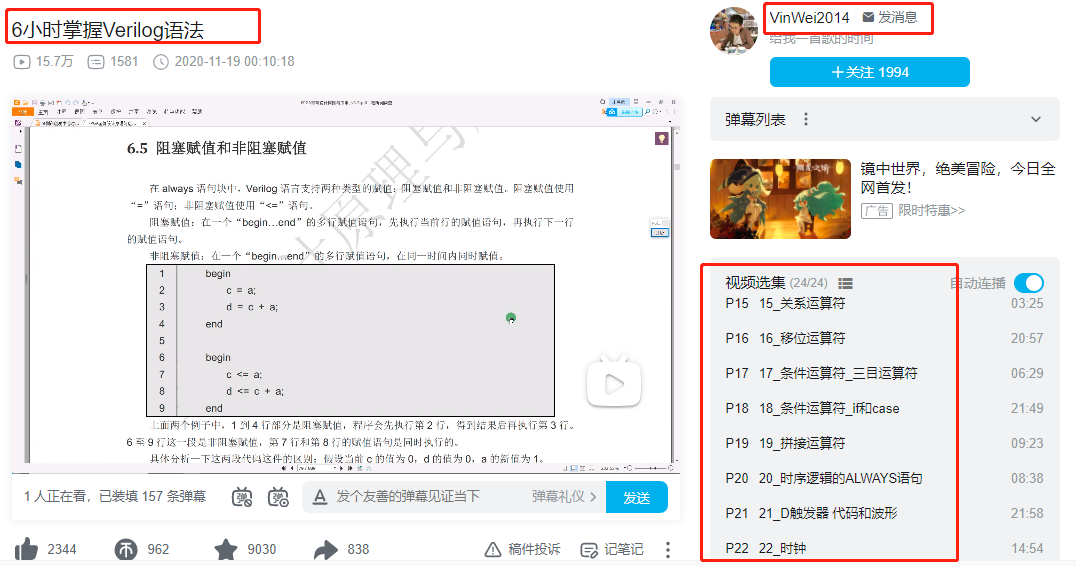

所以我进一步系统的学习了Verilog语法。我的目标是需要知道一个知识框架(大纲),至于具体的怎么写代码,具体的知识点,可以在用的相关内容的时候,在去学习。所以我又在B站上看了Verilog语法视频。

当我把两套视频看完了之后,心中顿时有了一个大概,就可以对照的正点原子的《开发指南》开始动手了。视频开完的感受是:

1、从视频上来讲,《6小时掌握Verilog语法》讲的要比原子哥讲的要全面。基本上也够Verilog开发了,所以,可以跳过原子哥的Verilog语法篇,直接看《6小时掌握Verilog语法》。

2、对于我来说,大学学习FPGA也就只做了一个38译码器和状态机,而且还是单个文件搞定,对于模块例化,完全没概念,也是在看完视频才知道怎么去例化。这方面可以参看原子哥的《开发指南》。

总体来说,原子哥的《开发指南》要比视频讲的要详细很多,知识点讲的要更透彻一些。(这部分的视频做的不如STM32讲的那么细致,有可能学习FPGA毕竟是少数人)。

Verilog语法学习总结

1、Verilog语法入门确实简单,很多的地方与C还是很相似。

2、Verilog语法实际上就是告诉EDA软件,怎么在FPGA内部布线,去描述内部的接线组合关系。这部分的代码,我称之为有效代码。这部分的内容也很简单,入门很快。但是,Verilog语法的难点,反而是调试部分相关的代码。比如在FPGA开发过程中,需要测试信号,需要调试,这时候需要额外去编写一个测试代码文件,这部分代码主要功能就是给测试激励信号,我个人认为这部分内容反而有点难。

3、最后一个重点就是思维的转换。在我们单片机开发,C语言的编写,最后的目标是形成一串串指令,然后在单片机内部依次执行。而我们的Verilog语言的最终目标是,在FPGA芯片内部形成电路连线组合关系,搭建能实现特定功能的电路。这应该是二者最大的区别。

紫光PGL22G芯片了解

在编写FPGA的代码之前,出于职业习惯(硬件工程师),我比较好奇芯片的硬件电路板该如何设计?假如给我一颗FPGA芯片,能不能画出针对这芯片的应用电路板,所以我还是先看了一下PGL22G芯片的数据手册。

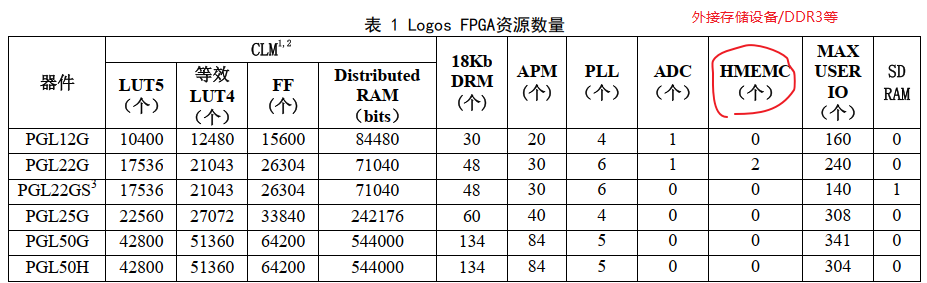

PGL22G芯片属于Logos系列,而《Logos系列FPGA器件数据手册.pdf》整个手册也就40多页,而且全中文,一小会儿就看完了。

总体来说,FPGA内部最主要的就是基本逻辑单元CLM,而APM可以组成加法器和乘法器。其它的就是IO,很多的IO。最多就有个ADC。

这与我们单片机(内部一大堆外设,数据手册都是几百上千页)比较起来,就要精简很多。

如何设计出基于紫光PGL22G这个芯片的最小系统?

一般一个FPGA的最小系统组成由,电源电路,复位电路,外部时钟电路,下载电路,以及SDRAM和外部FLASH。

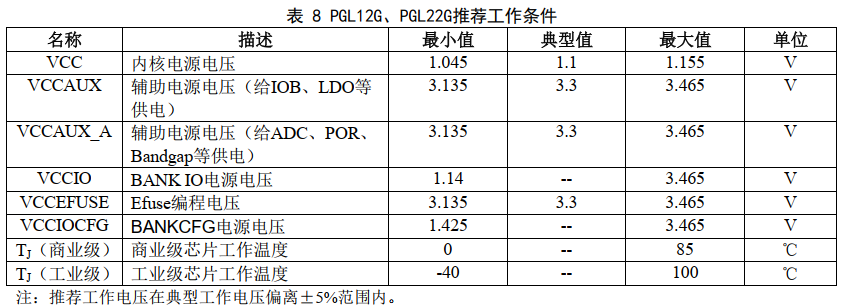

首先是电源电路,这个PGL22G芯片,需要内核电源1.1V,辅助电源3.3V,然后就是BANK IO电源。

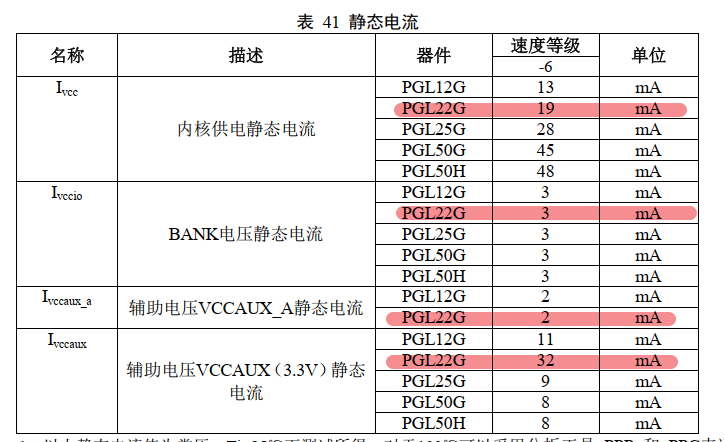

从上表可以看出,FPGA的电流不太高,就是几十个mA级别。这里正点原子直接用了一个1拖4路的DC-DC电源芯片,将5V降压为1.1V、1.35V、1.8V、3.3V生成了4路电源。

复位电路,外部时钟电路,这个FPGA似乎没有专用的复位引脚,随便拿一个普通的IO都可以当做复位引脚,到时候在软件中进行绑定。而时钟电路则使用的外部有源晶振,直接50MHZ输入。

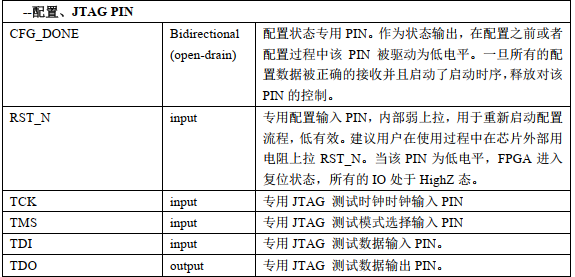

下载电路采用外部JTAG下载器,下载接口有固定的引脚。

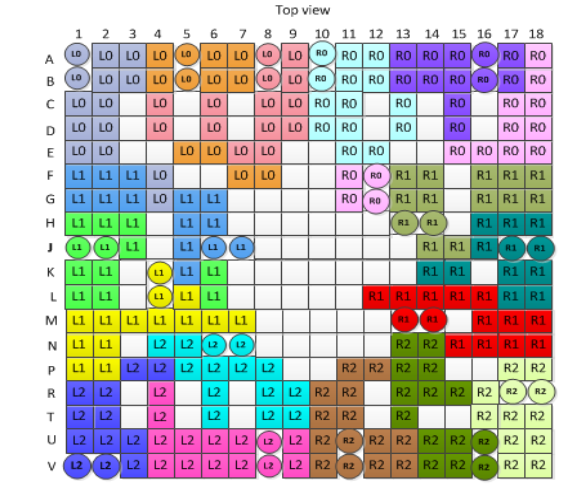

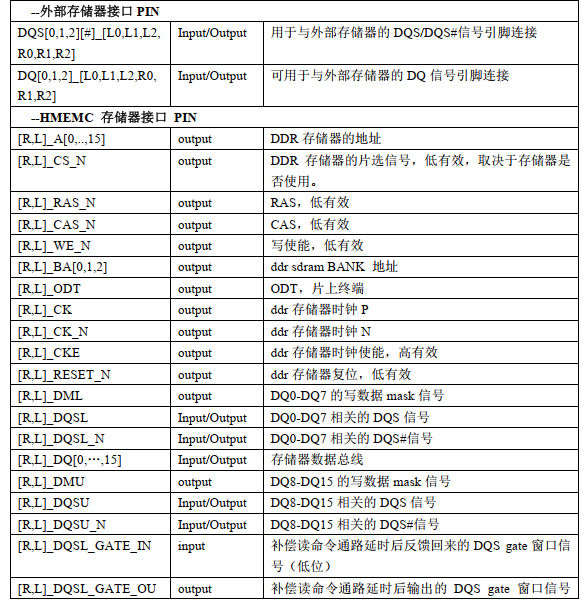

SDRAM和外部FLASH的接口的选择范围应该是只能在下图范围任意选择(??)。

不过,这里我有个疑问:

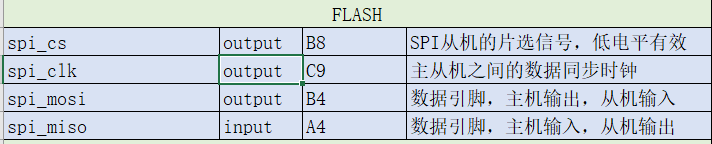

在正点原子的开发板中,FLASH用的引脚是B8、C9、B4、A4,比如,在流水灯的PDS工程中,没有设置这几个FLASH用引脚。FPGA怎么知道需要从哪几个引脚去读取FLASH?

大致看了一下FPGA的数据手册,再对比着原子哥的原理图,对紫光PGL22G芯片基本上有了一个大致的了解。同时也体会到就算是画一个FPGA的最小系统也是比较麻烦的存在,SDARAM的等长走线,里面涉及一部分的高速走线,感觉没有太大的把握。以后如果真的做FPGA的项目,还是考虑使用核心板的方式吧。

最后在说说关于FPGA的学习计划

关于前面花费这么多时间看视频,我个人觉得对我自己还是很有必要的。虽然“光看不练,等于白干”,但是至少在后面写代码的时候,遇到问题,至少我能知道怎么去查找资料,该使用怎样的关键字。起码,有一个基本的Verilog语法框架。

接下来的事情就是跟着原子哥的《开发指南》手册,依次做一遍。先熟悉下Verilog语法和PDS软件的使用方法。

更多回帖