虚拟化在基础设施应用中无处不见,它通过在同一系统硬件上并行地运行多个隔离环境,来提供安全性,提高效率和减少成本。每个环境运行在一个虚拟机上,让其感觉它独占处理器,外设,系统内存和IO设备。

系统性能对保证虚拟化的环境不会影响用户体验很重要。虚拟化环境的性能取决于以下因素:传输带宽,延迟和优先级, hypervisor和内存地址翻译开销,并行执行上下文的数量。Arm系统IP考虑了这些因素,与优化的驱动程序一起,为下一代虚拟机提供了最好的总体系统性能。

Arm提供的参考平台和软件框架对使能arm生态的虚拟化是关键。构架标准保证跨平台的统一性,同时允许系统供应商的差异化。Linaro,arm和生态伙伴一起,为构建工具和驱动贡献力量,帮助加速系统开发。

Arm系统IP由构建Armv8.x CPU内核为中心的高效系统的构件组成。这些IP已经进化了几代,以解决云基础设施平台的关键性能和弹性问题。使能虚拟化的关键IP是SMMU和GIC。

虚拟化的一个关键需求是允许每个虚拟机操作它自己的地址空间和对系统各种master的物理内存访问的硬件管理。Arm新System MMU, MMU-600,支持stage-1和 stage-2地址翻译,具有地址空间映射和安全机制来防止非法访问。在一个典型系统中, stage-1将来自IO master的虚拟地址(VA)翻译为中间物理地址(Intermediate Physical address, IPA); 这个地址空间一般由操作系统管理。MMU-600支持嵌套式翻译,MMU为一个请求进行stage-1和stage-2翻译。

MMU-600支持PCIe Gen4的 Address Translation Service(ATS),使基于PCIe的IO设备或加速器可以提前预取地址转换,并它放到IO设备的Address Translation Cache(ATC)。 通过这个流程,IO master可以通过设备ATC发出已经翻译过地址(translated address)的DMA请求,因此避免了在MMU中地址翻译的开销。

Page Request Interface (PRI)使un-pinned系统内存页成为可能,从而进一步提升系统性能。通过PRI,IO Master预取转换可以帮助从系统盘中取数据到系统内存页,而不会导致有害的page fault效果。这可以极大提供IO Master的效率,因为从系统盘到系统内存的时间不再被实际传输观测到。此外,MMU使IO Master可以访问大很多的系统内存,因为可以利用虚拟内存带来的好处。

具有Single Root IO Virtualization (SR-IOV)功能的PCIe Root Complex (RC)使虚拟PCIe功能可以集成到系统中,提供IO虚拟化。在PCIe RC中,给每对Virtual Function (VF)和Physical Function (PF)映射分配唯一的PCIe Requestor ID(RID), RID被映射到一个系统中唯一的StreamID. MMU-600使用这个StreamID映射虚拟地址到物理地址。MMU-600支持2^36个StreamID, MMU-600可以同时支持百万个VF-PF。SR-IOV使系统数据流旁路hypervisor虚拟栈中的软件switch层。

在虚拟机环境中,VF被分配给一个虚拟处理单元(Virtual Processing Element, VPE),系统数据流直接在VF和VPE间流动。因此,消除了在软件模拟层的IO开销,显著减少了虚拟化环境的IO开销。

如PCIe ATS流程定义中的一样,MMU-600支持将硬件使失效一个翻译(hardware invalidation of translation)传播到ATC,确保IO Master总是缓存最新的内存翻译。因为使失效操作完全是由硬件完成的,软件的开销被最小化,从而提升总体系统性能。MMU-600是非常有弹性的,可以用于小型网卡到大型服务器系统。

基础设施系统广泛包含从处理来自终端设备的网络数据流的部署在edge的小型smart NIC到部署在中央数据中心的大型服务器。这些系统配置通常有不同的功耗和面积需求。MMU-600设计的弹性让解决方案提供商可以定制系统来满足特定的功耗面积目标,同时保持跨应用的MMU软件驱动的通用性。

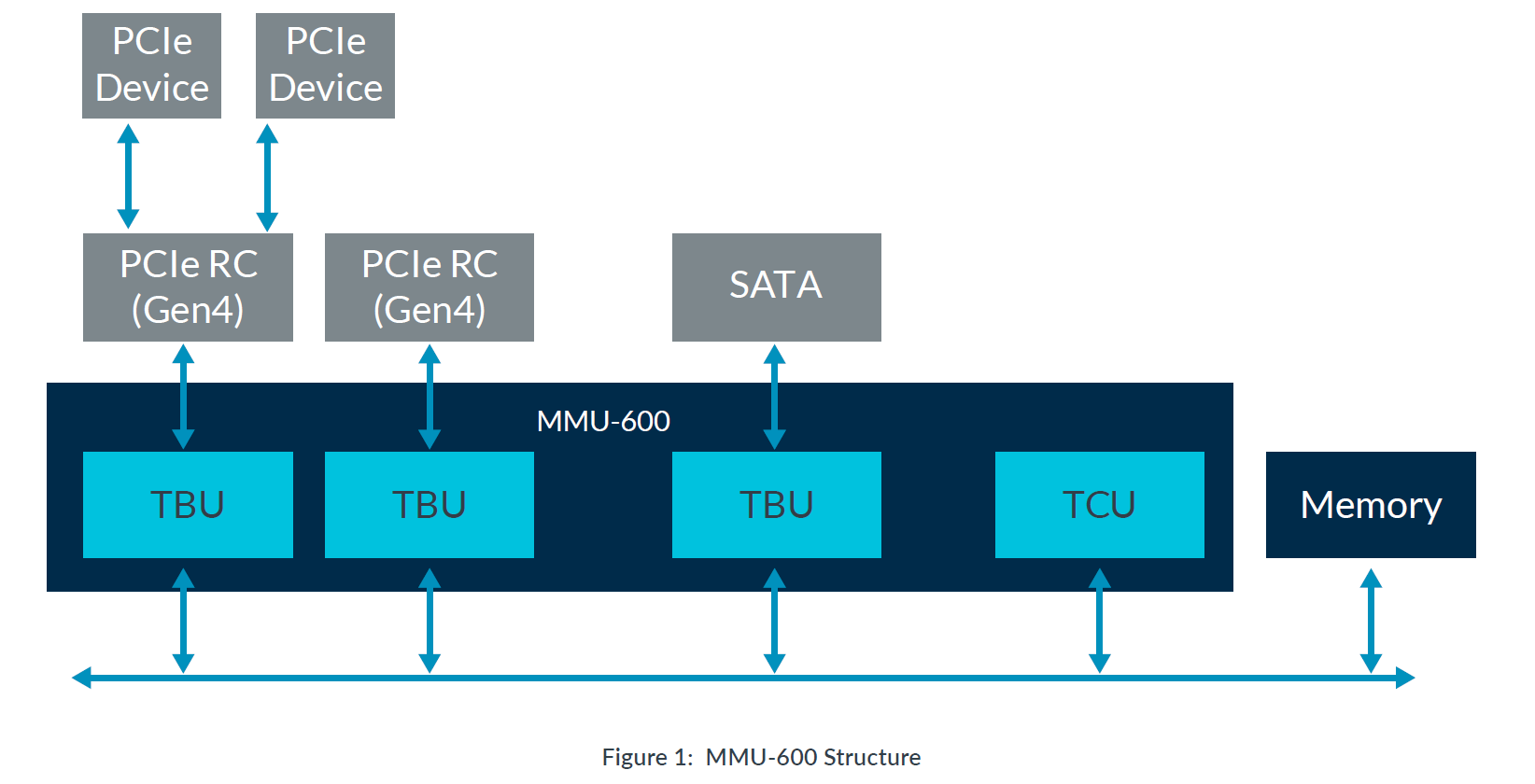

MMU-600由两大部分组成: Translation Buffer Unit (TBU)和Translation Cache Unit(TCU)。 TBU由一个Translation Lookaside Buffer(TLB)组成,而集中式的Translation Cache Unit(TCU)有一个大的translation cache并且负责page table walk。 Hit在TBU-TLB的translation被马上服务,这个传输被发送到系统总线上。TBU-TLB miss的情况下,一个特殊的传输被发送给TCU来取地址翻译。TCU cache hit的话,返回地址翻译结果,否则需要在系统内存中进行page table walk。

如图1所示,一个TCU可以服务多个TBU。TBU和TCU之间的通讯是利用AXI Stream总线,使用SMMU特有的称之为Distributed Translation Interface (DTI)的协议,这使分布式的MMU构架成为可能。通过让TLB靠近IO Master,利用AXI Stream总线上的消息与TCU通讯方式,有助于系统设计的弹性。

当运行在虚拟化环境时,及时地将中断和异常通知到虚拟处理单元是很重要的。GIC-600是GICv3构架兼容的中断控制器,它具有支持很大数量CPU core和多芯片(multi-chip)配置。

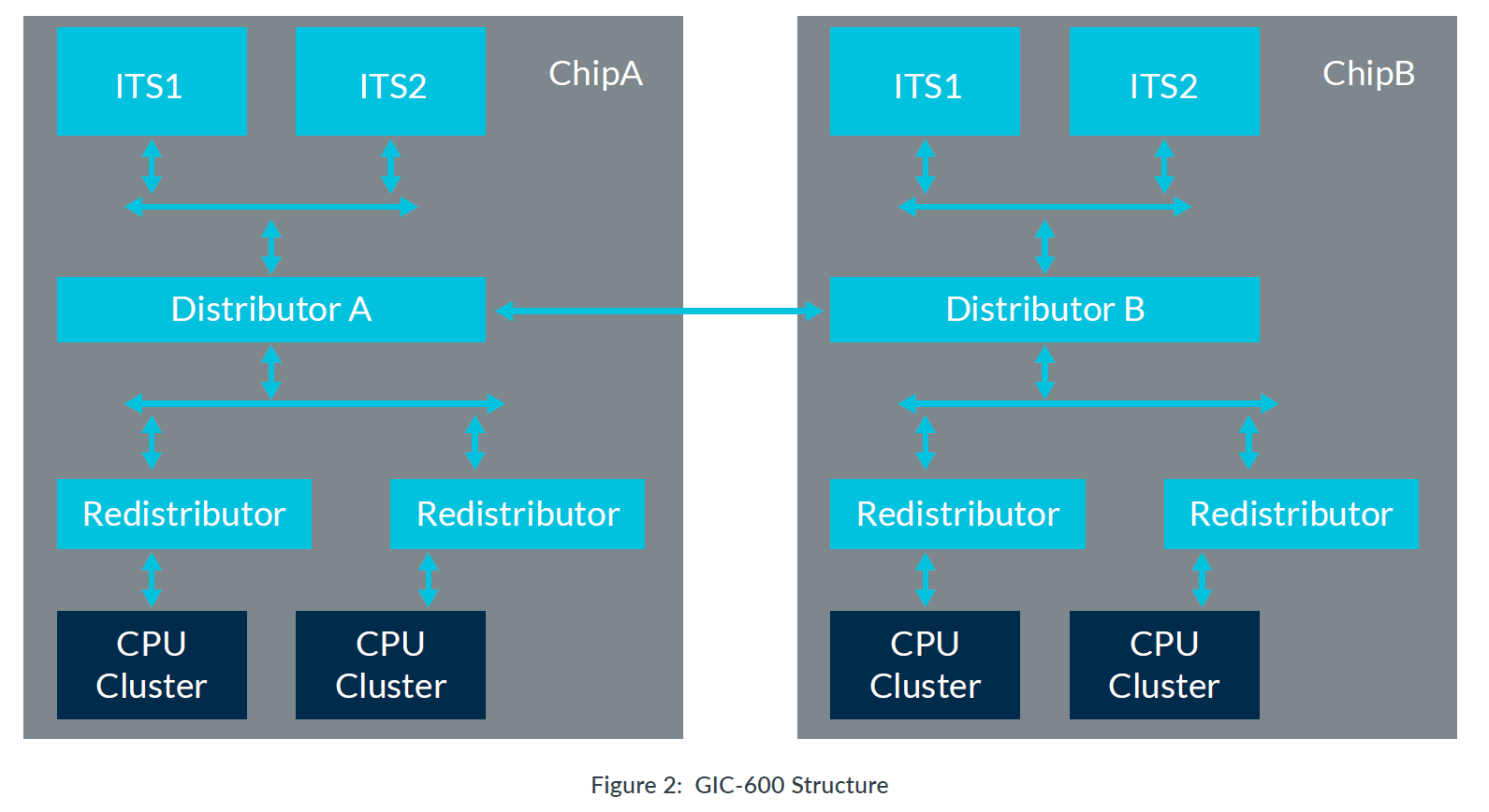

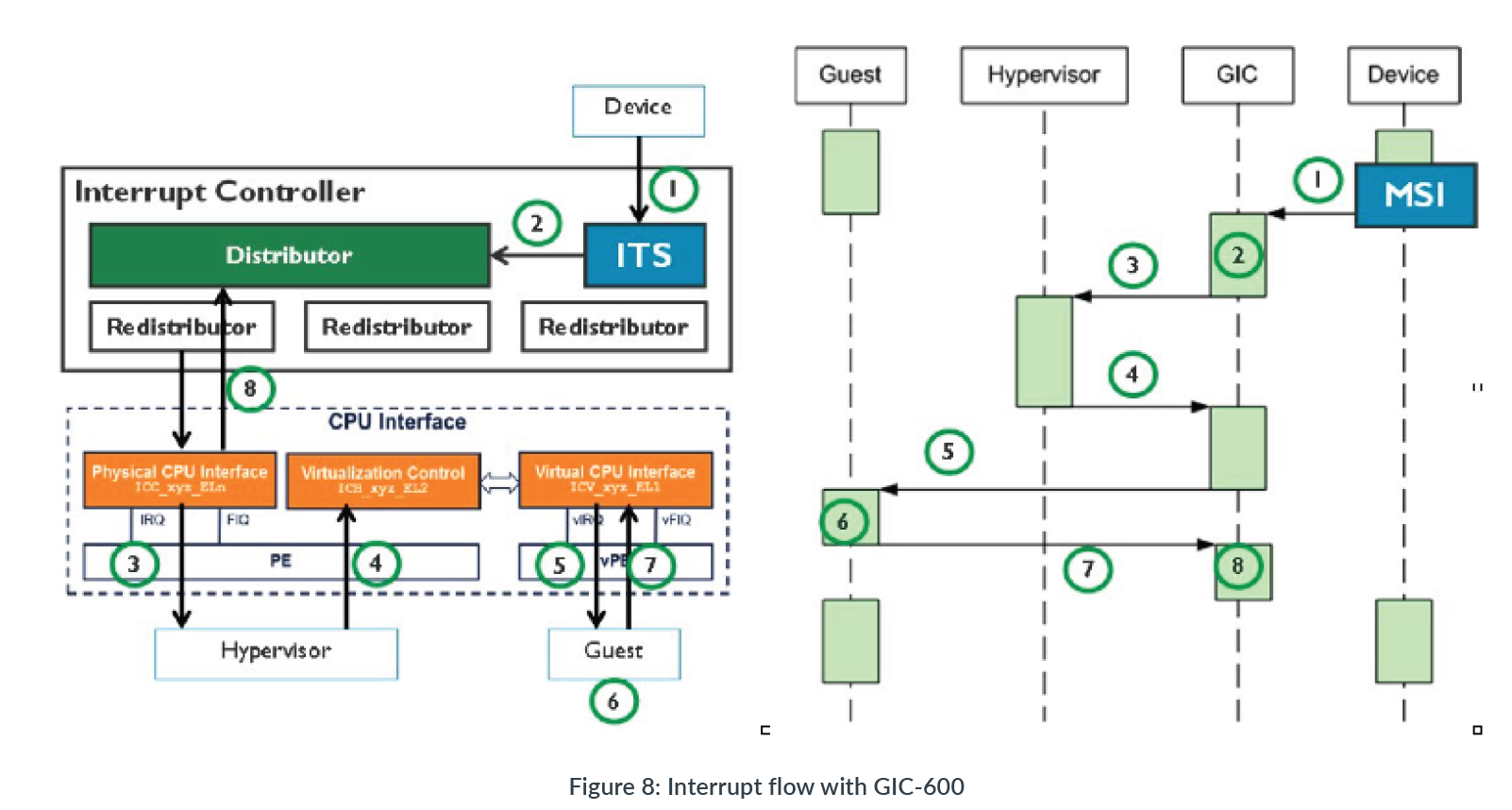

GIC-600结构上由 Interrupt Translation Service (ITS)模块,Distributor和Redistributor组成。ITS模块将Message Signaled Interrupt(MSI/MSI-X)中断翻译成Arm Locality-Specific Peripheral Interrupt(LPI). Distributor管理中断的发送路线,将中断指向合适的core-cluster来响应这些中断。 Redistributor是每个core特有的接口,它映射进来的中断为core 特定的中断,称为FIQ(Fast Interrupt Request), IRQ (Interrupt Request)或SError(System Error)。在虚拟化环境中,core的中断被虚拟化,进来的物理中断被hypervisor映射给一个虚拟机。

GIC-600允许中断共享并分发给单个芯片上的多个计算和IO域。此外,它也支持同一个封装里跨多个芯片或socket的中断管理(如图2所示),同时提供给系统中所有计算单元一个统一软件视角。Socket内或是Chiplet内的消息被转换为原生的通讯传输协议。

GIC-600支持4种不同的系统中断,它们被映射为core上特定的物理或虚拟中断。

1 Private Peripheral Interrupt (PPI): 它们是要给特定core处理的外设中断。比如, Generic Timer使用PPI来中断它对应的core

2 Software Generated Interrupt (SGI): 这些中断用做 处理器间通讯

3 Shared Peripheral Interrupt (SPI): 它们是全局外设中断,可以发送给一个特定的core或是一组core

4 Locality-specific Peripheral Interrupt (LPI):它们是 message based interrupt, 主要用作翻译MSI/MSI-X中断

GIC-600支持最多为56K个 MSI/MSI-X中断。MSI/MSI-X翻译和中断发送路线表被存在内存中,并可以被GIC 缓存(cache)以减小最近使用过的中断的延迟。目标为一个虚拟机的中断被hypervisor将此物理中断定向到特定的虚拟机。GICv3规范包括CPU Interface寄存器的硬件虚拟化,用来直接控制目标为一个虚拟处理单元的中断。Hypervisor可以控制使能/禁止virtual CPU Interface,virtual interface 寄存器的访问(为了上下文切换),配置 maintenance中断和控制虚拟中断。GIC-600提供了一个接口给hypervisor来注册LPI, SPI和PPI中断,hypervisor然后为每个中断指定目标虚拟机和优先级。所有进来的中断在一个list寄存器中维护,它被用来将中断发给合适的虚拟机,对于LPI,list寄存器被每个虚拟机的表所替代。通过这种机制,映射物理中断到虚拟中断的软件开销被去除。

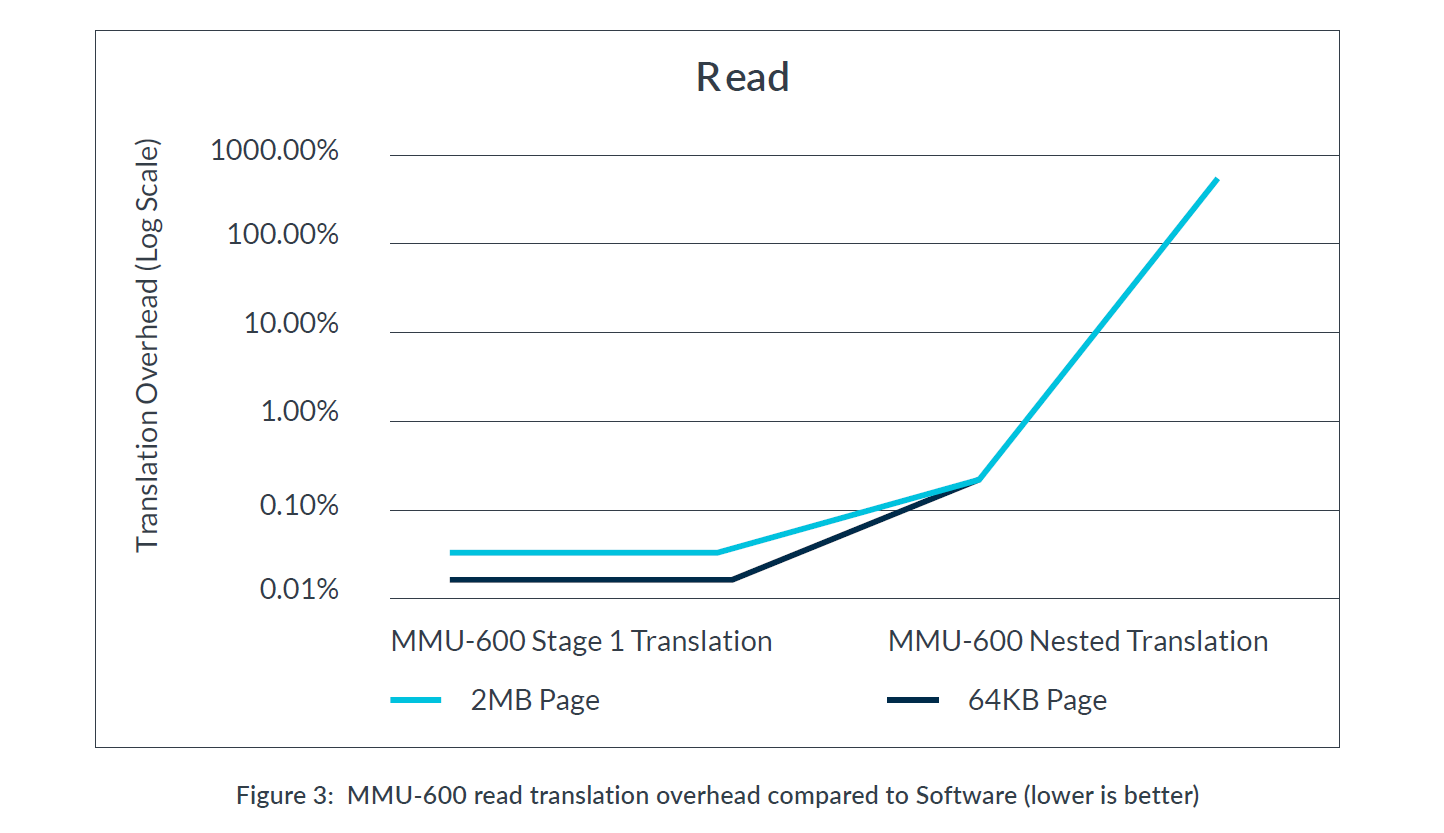

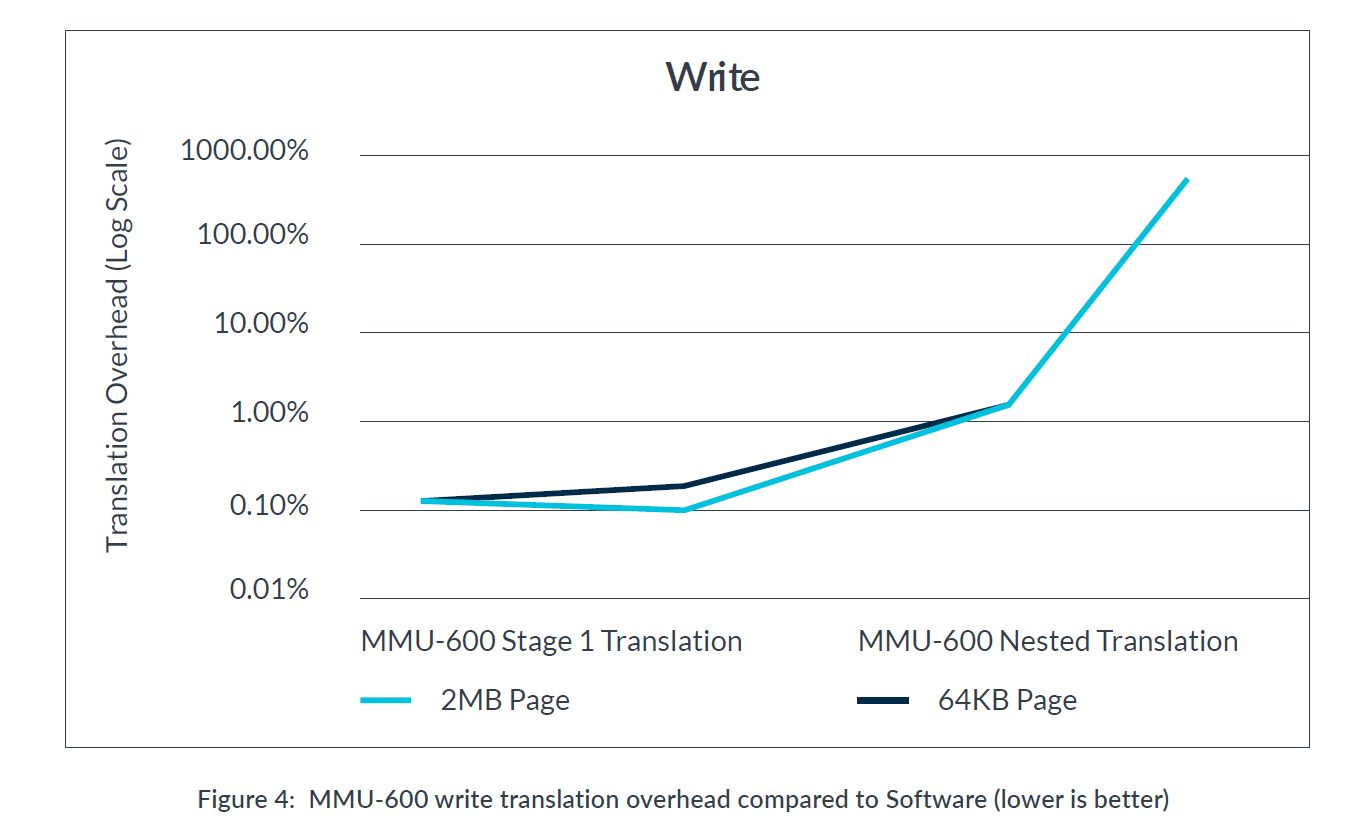

SMMU的主要目标是提供系统中IO组件和CPU本身一样的内存视图。为此,从这些IO组件进来的传输需要经过VA到PA的地址翻译,这需要对页表的多次查找。这些页表通常存在系统内存中,但可以缓存(cache)到SMMU以提供性能。虽然系统可以使用软件进行VA到PA的翻译,但是这与硬件翻译相比会明显拖慢系统。

MMU-600通过预取和缓存转换减小需要访问慢速系统内存的时钟周期,显著提升硬件翻译的性能。相比没有MMU的系统,结果显示了翻译带来的极小系统性能开销,和相对软件翻译数量级的翻译性能提升。

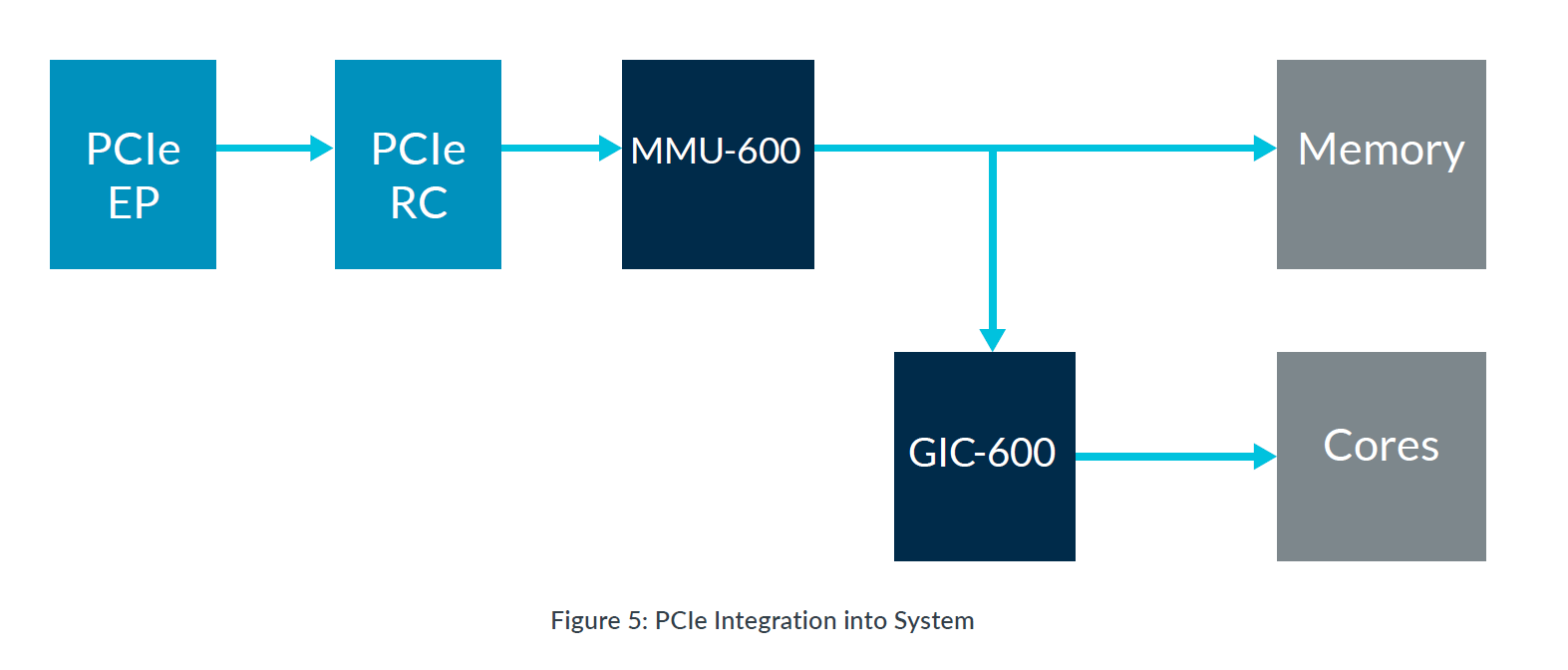

图5显示了GIC-600和MMU-600与PCIe IO Master的接口,利用PCIe RC来讲PCIe 协议转换为AMBA协议。

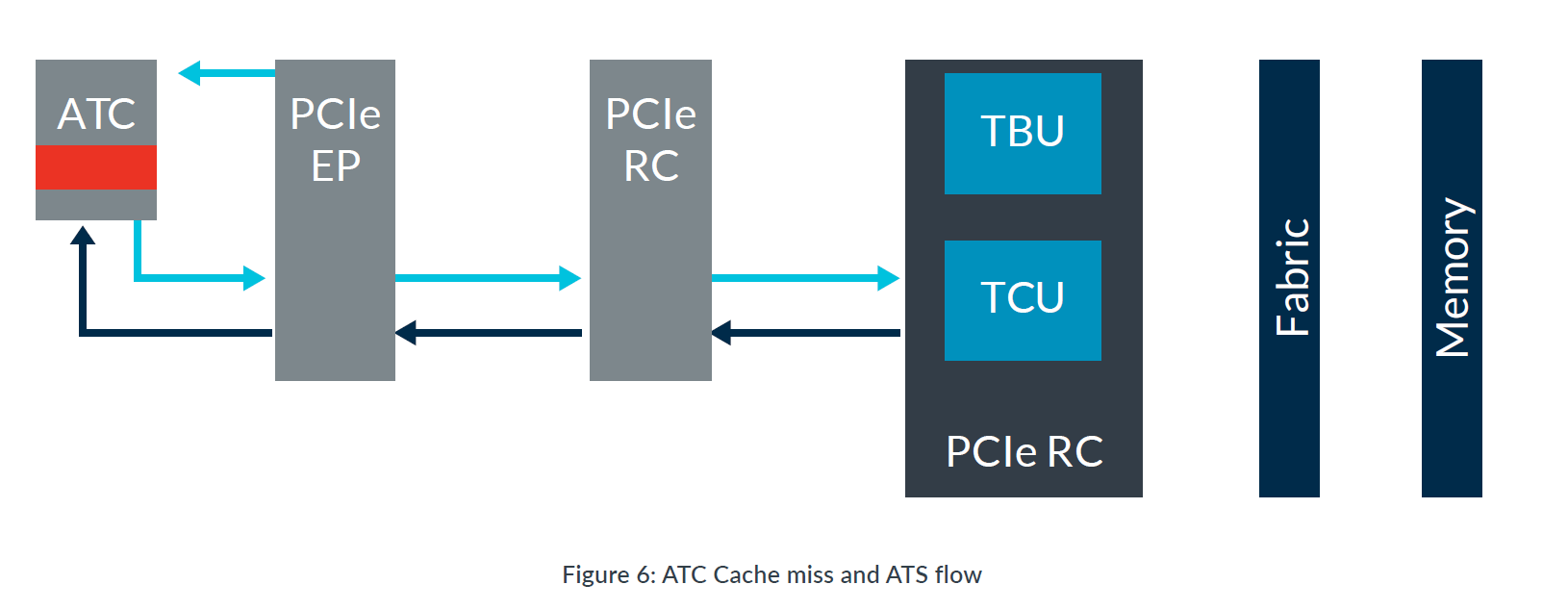

为了填充Address Translation Cache (ATC), 此PCIe Endpoint (EP)产生一个ATS请求给PCIe RC。PCIe RC通过DTI接口给MMU-600 TCU发起一个请求,让TCU预取翻译。如果有效,被请求的翻译结果发给PCIe EP用于填充其ATC。如果翻译无效,一个否定响应发送给PCIe EP.

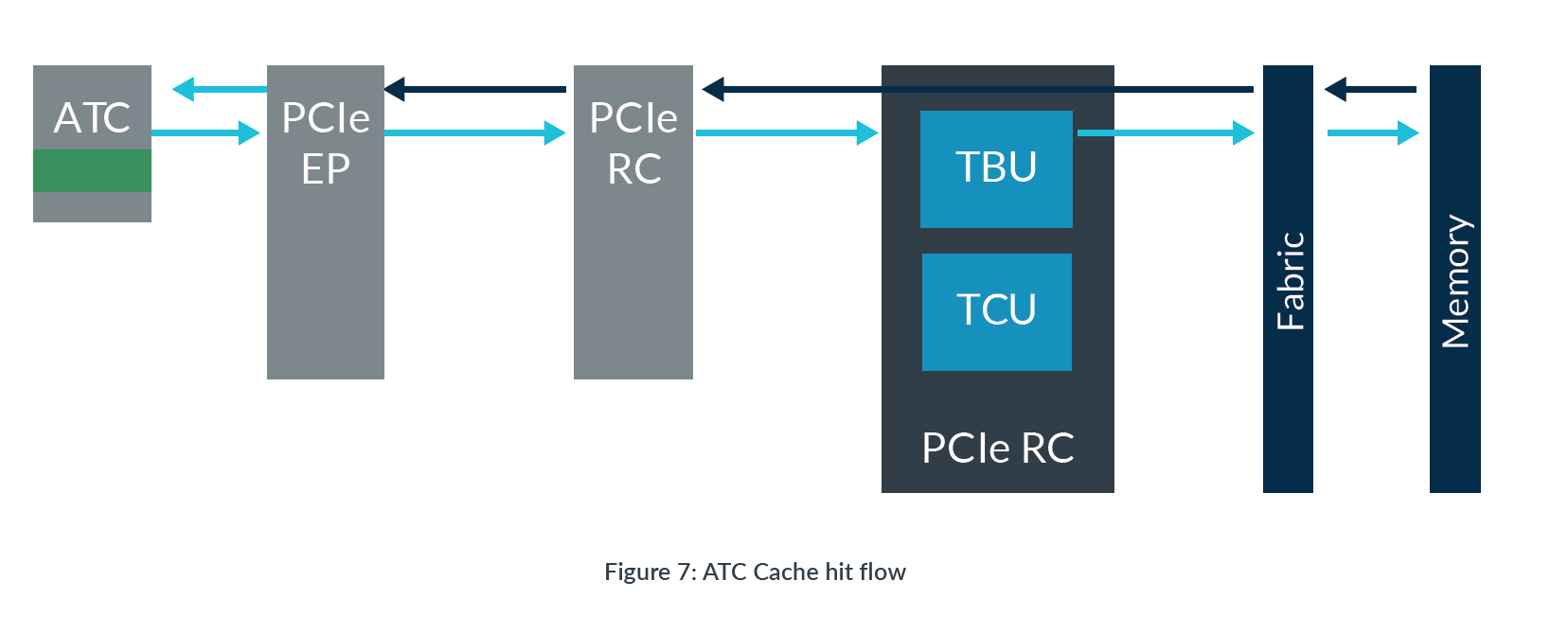

一旦这个翻译在ATC可用,IO Master可以使用这个翻译过的地址发起一个内存访问请求。这些请求从IO Master发送到PCIe RC. 这些请求绕过MMU-600 TBU直接发送到系统内存。

如果一个ATS请求因为翻译不存在结果而失败,PCIe EP可以发送一个PRI传输给MMU-600, MMU-600可以请求系统软件将请求的页面驻留在系统内存。系统软件指示PRI过程的完成,这时PCIe EP可以发起另一ATS请求来填充ATC。

从PCIe来的中断以MSI的形式进入系统。PCIe MSI被GIC-600模块翻译成Arm LPI中断。这些中断被发送给SoC中的Distributor,由它发送给合适的运行hypervisor的 物理CPU core. Hypervisor更新list寄存器来映射进来的中断为要发送给特定虚拟机的虚拟中断。

原作者:修志龙_ZenonXiu

更多回帖