关于你的第一个疑问,当你屏蔽掉RCC->CFGR0 |= (uint32_t)(3<<22); rcc-="">CFGR0 |= (uint32_t)(3<<22);这两行代码之后,在RCC配置完成之后将RCC_CFGR0寄存器的值打印出来为0x35040a,,位17默认为0,HSE 4分频进入PLL,如下图。即sysclk大小为32/4*15=120MHz,MCO输出120MHz。当注释掉这两行代码,HSE会按照位17默认配置进行4分频;

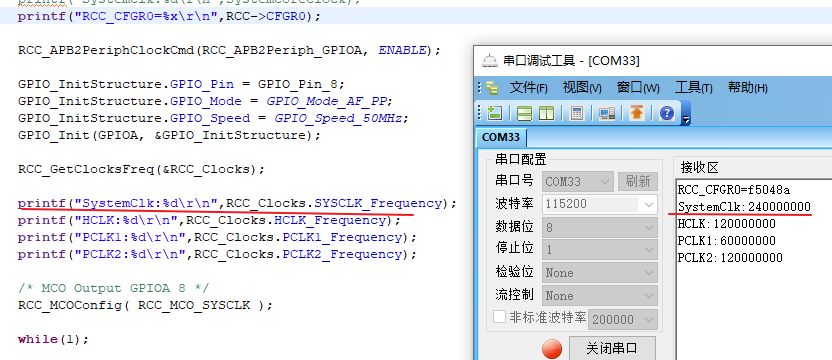

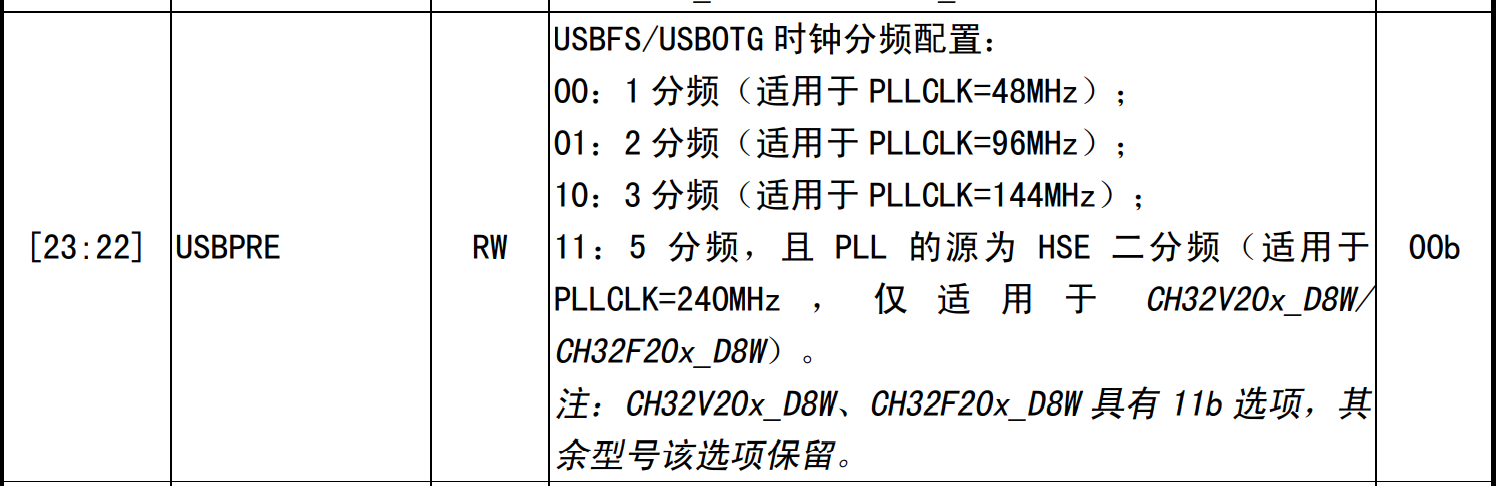

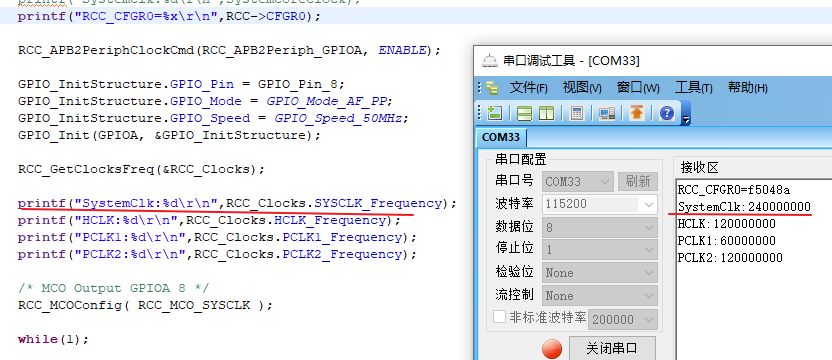

关于你的第二个问题,当不注释掉这两行代码的时候,sysclk打印输出即MCO引脚输出都是240MHz,我这边测试都是没问题的,如下图2。测试的时候注意示波器的采样率不要低于所测量的数值。否则会测试不准,采样率最好大于240MHz.

图1

图2

关于你的第一个疑问,当你屏蔽掉RCC->CFGR0 |= (uint32_t)(3<<22); rcc-="">CFGR0 |= (uint32_t)(3<<22);这两行代码之后,在RCC配置完成之后将RCC_CFGR0寄存器的值打印出来为0x35040a,,位17默认为0,HSE 4分频进入PLL,如下图。即sysclk大小为32/4*15=120MHz,MCO输出120MHz。当注释掉这两行代码,HSE会按照位17默认配置进行4分频;

关于你的第二个问题,当不注释掉这两行代码的时候,sysclk打印输出即MCO引脚输出都是240MHz,我这边测试都是没问题的,如下图2。测试的时候注意示波器的采样率不要低于所测量的数值。否则会测试不准,采样率最好大于240MHz.

图1

图2

举报

举报

举报

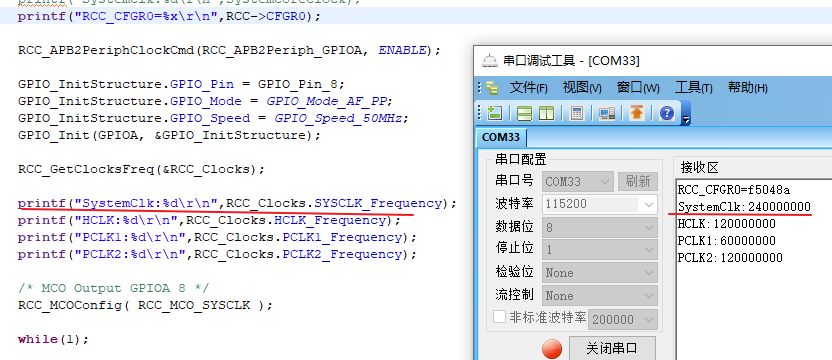

举报