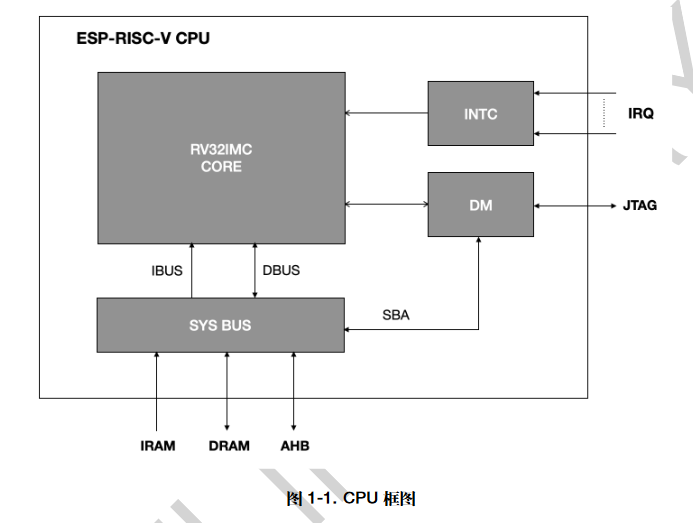

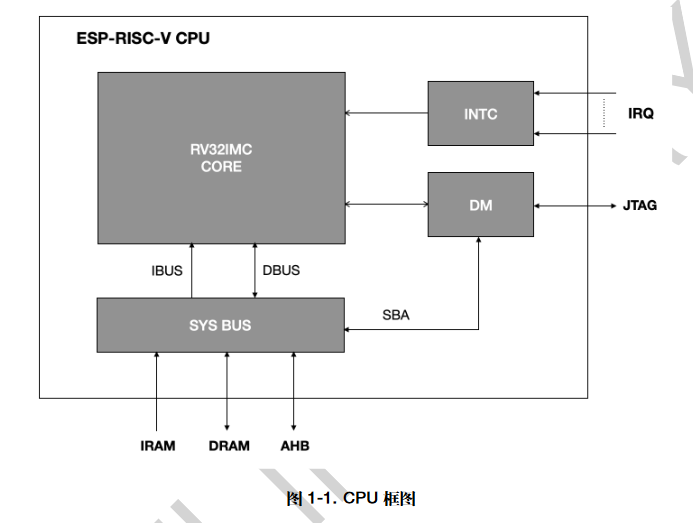

ESPRISCV CPU

概述

ESP-RISC-V CPU是基于RISC-V ISA的32位内核,包括基本整数(I),乘法/除法(M)和压缩(C)标准扩展。ESP-RISC-V CPU内核具有4级有序标量流水线,针对面积、功耗、性能等进行了优化。CPU内核架构包含中断控制器(INTC)、调试模块(DM)和用于访问存储器和外设的系统总线(SYS BUS)接口。

特性

- 时钟工作频率高达160 MHz

- 通过IRAM/DRAM接口零等待周期访问片上SRAM和缓存中的程序和数据

- 中断控制器(INTC)具有多达31个向量中断,可配置优先级和阈值级别

- 调试模块(DM)符合RISC-V调试规范v0.13,支持通过行业标准的JTAG/USB端口连接外部调试器

- 调试器通过系统总线(SBA)直接访问存储器和外设

- 硬件触发器符合RISC-V调试规范v0.13,具有多达8个断点/观察点

- 物理存储器保护(PMP),最多可配置16个区域

- 32位AHB系统总线,用于访问外设

- 可配置的核心性能指标事件