一种校验码、循环码(

通信),简称,是常用的具有错误、错误能力的校验码,在早期中使用。和计算机同步通信的数据校验。

CRC存储过程后除了,在接收方进行校验,以在接收码有错误时,若对CRC码有一定的错误则被错误地识别出是否有一个CRC码式,所以数据用同样的方生成某字位为不同类型,如果余数不为0,则说明错误,不同的错误位置余数。错误位置和余数的关系是确定的。

在系统中,在进行通信通道前线的标准中,CRC可能会在不同类型中进行不同的类型。

当应用

FPGA 进行通信系统设计时,我们发射端数据进行 CRC 正交频分复用、信道、干扰、路由等模拟编码处理,生成端口添加到端口,再进行需要调整到中或发射的发射端。

CRC校验,需要考虑两个因素:一是输入数据位宽;二是CRC生成式校验。

数据位宽,根据系统设计需要确定,CRC生成式根据相关协议或标准确定。

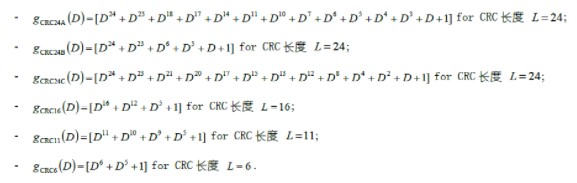

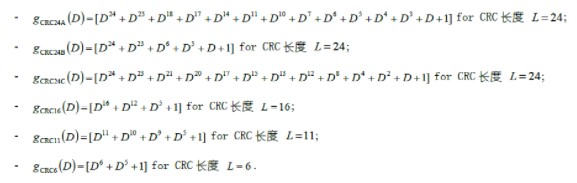

例如,在5GNR中,CRC生成式有以下几种:

代码,我们怎么用verilog HDL或VHDL去实现呢?

首先了解CRC校验的原理,我们剩下的事情就是搬砖的了。

人并且总是喜欢偷懒,“拿来主义”的存在,甚嚣尘上。

热心农家们,一边写代码,一边维护各种开源网站,各种技术博客,于是“号”。

就这样,总有人在地热血沸腾地成为我们。

一个是easics,一个是outputlogic。

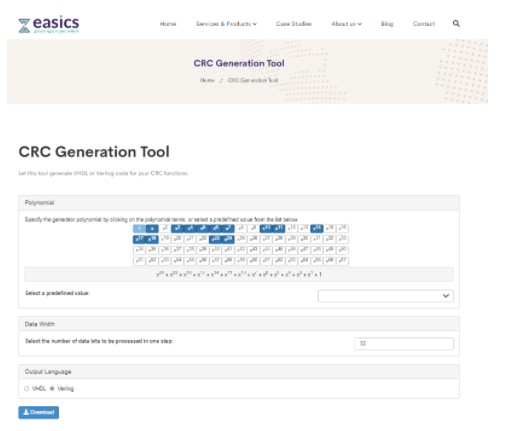

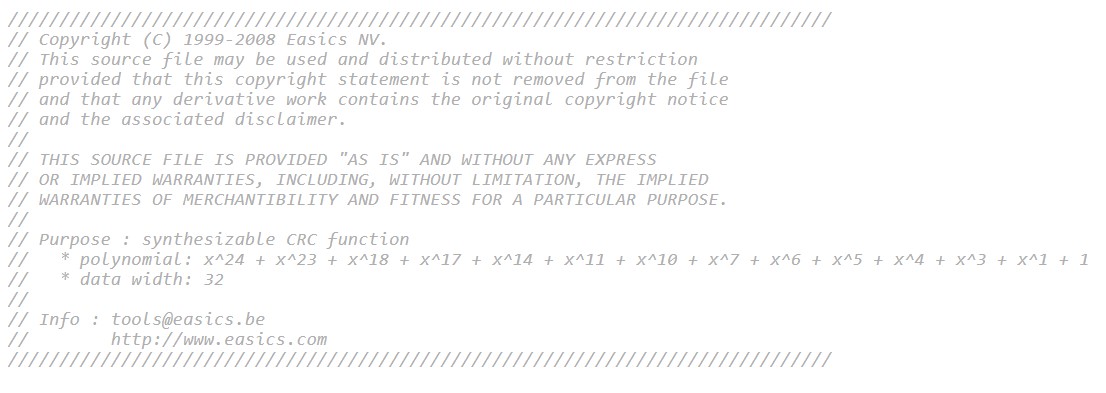

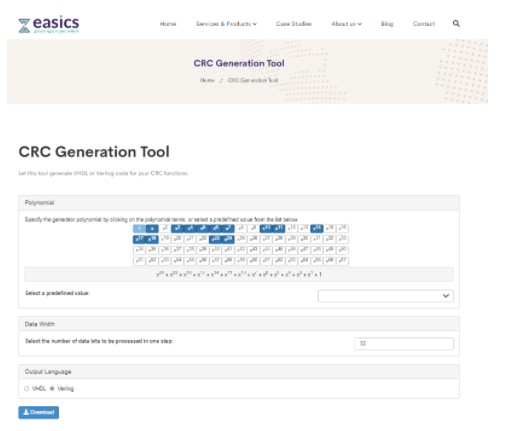

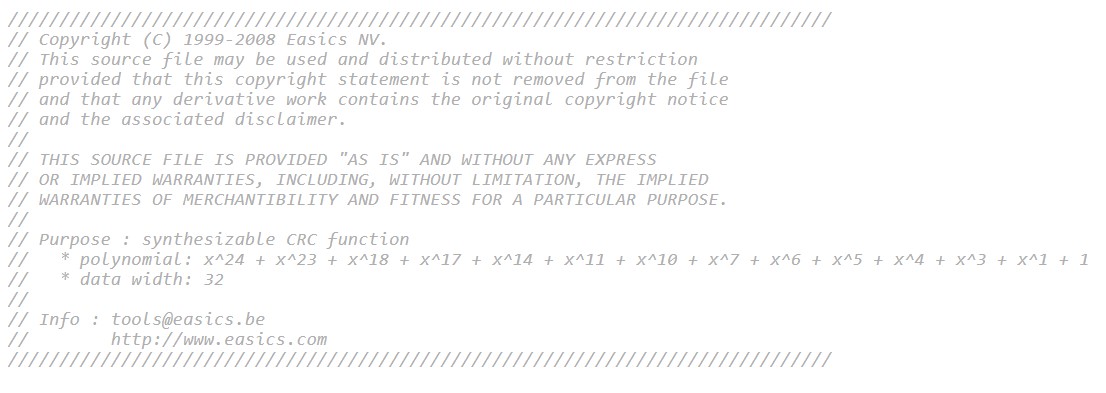

在easics的CRC生成工具中,我们选择好格式,确定好位宽和输出语言,于是一个crc功能的verilog代码就生成了。

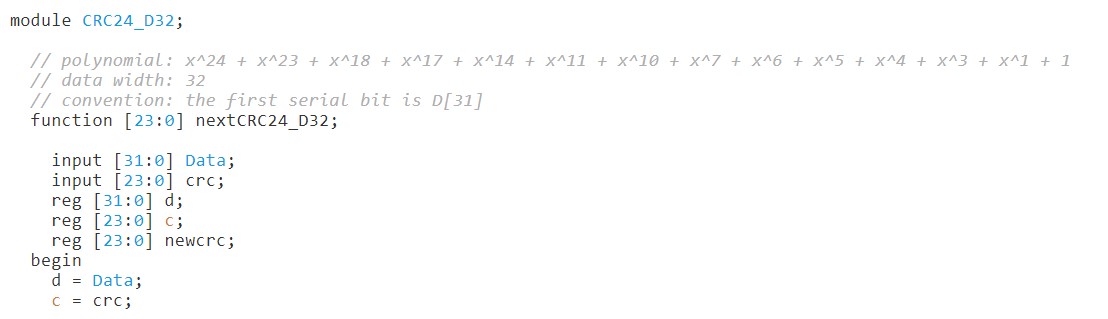

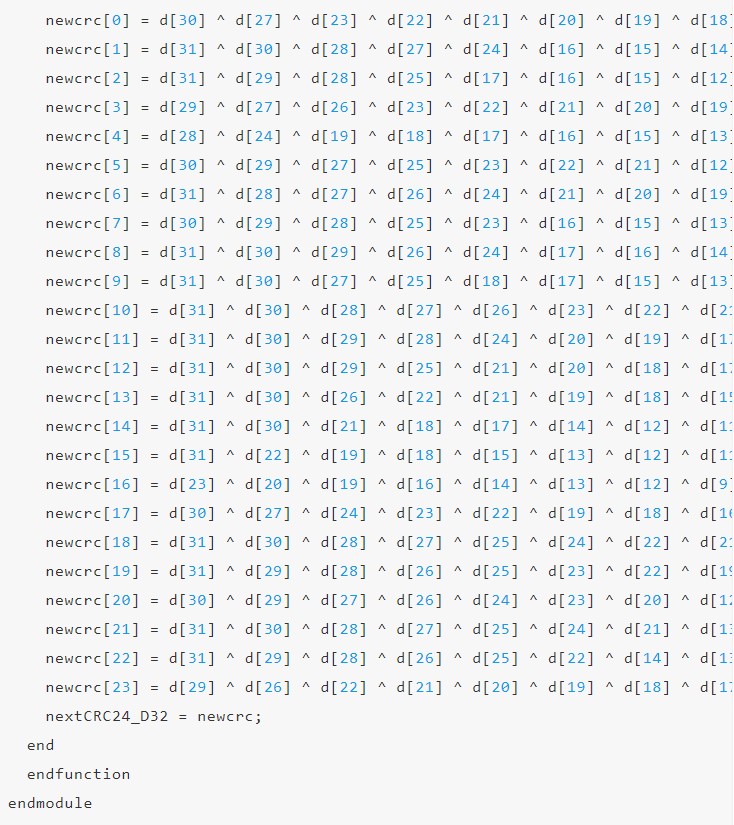

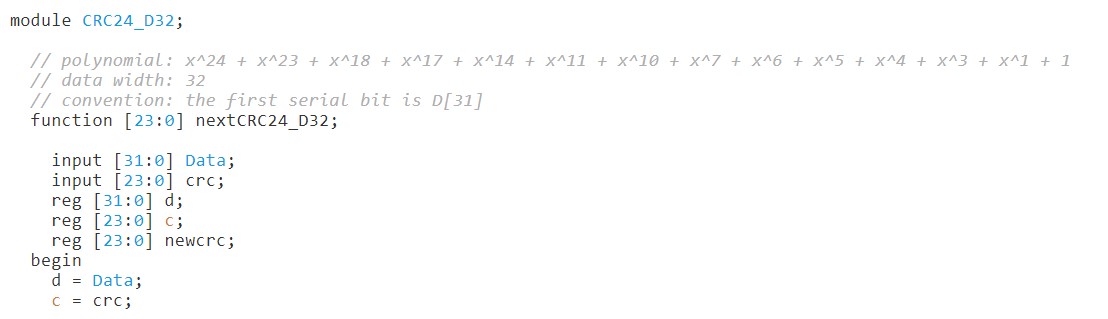

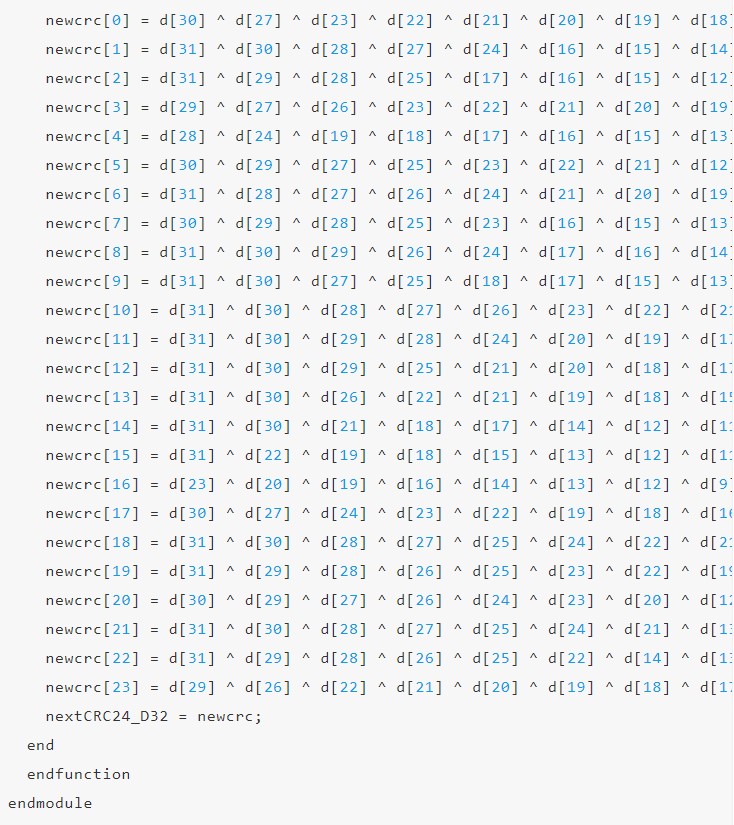

代码如下:

当然,这不是一个可以直接使用的模块,还需要手动改一下格式。

有没有更完整的CRC生成器呢?

输出逻辑出现了。只需要两步,就可以完成。

设定数据位宽,选择式位宽,若具体,如USB、PCIe等,可直接好。然后点击“应用”,step2,协议协议类型,生成verilog,完成!

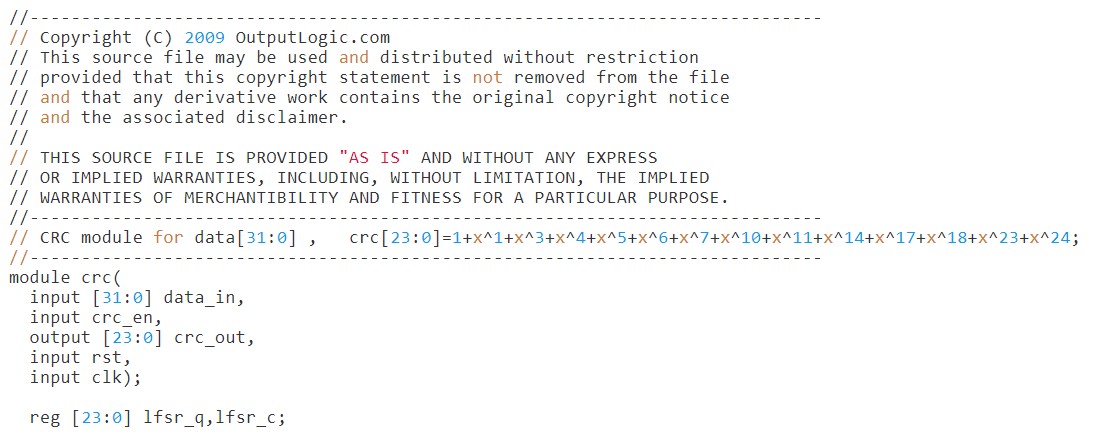

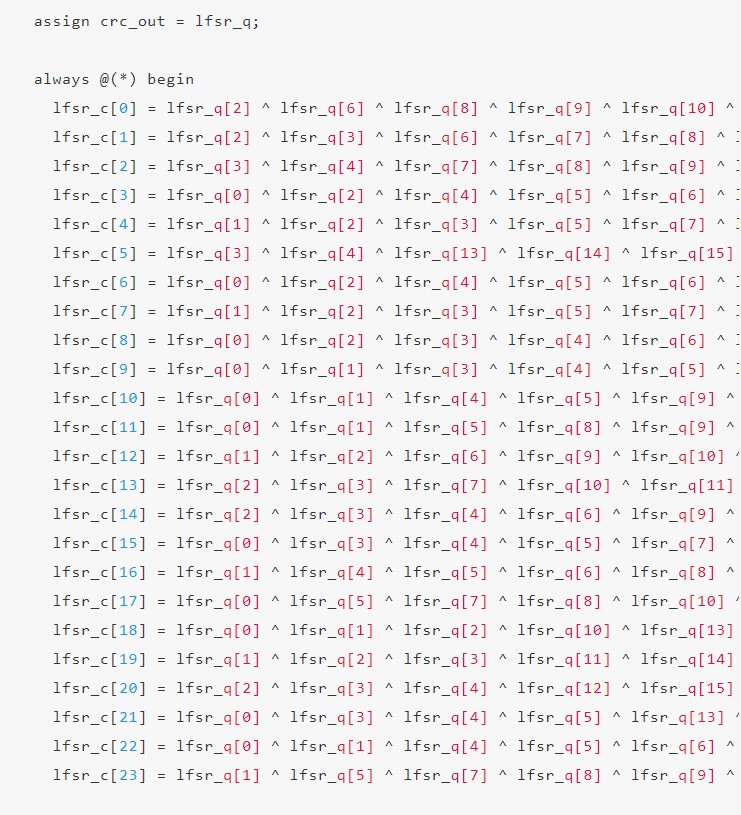

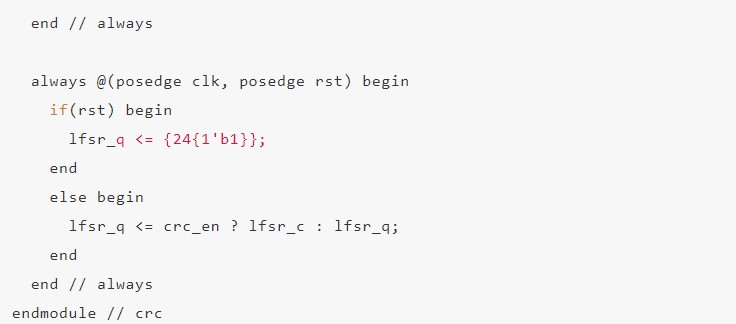

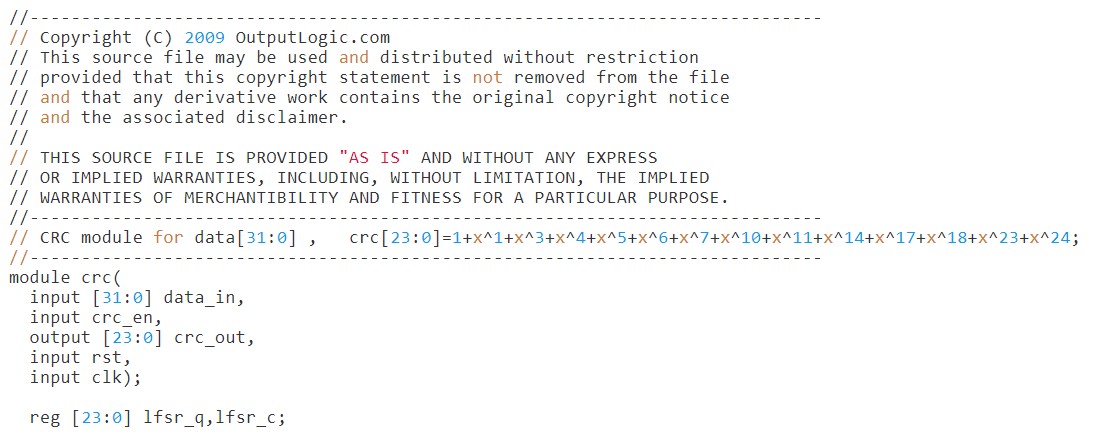

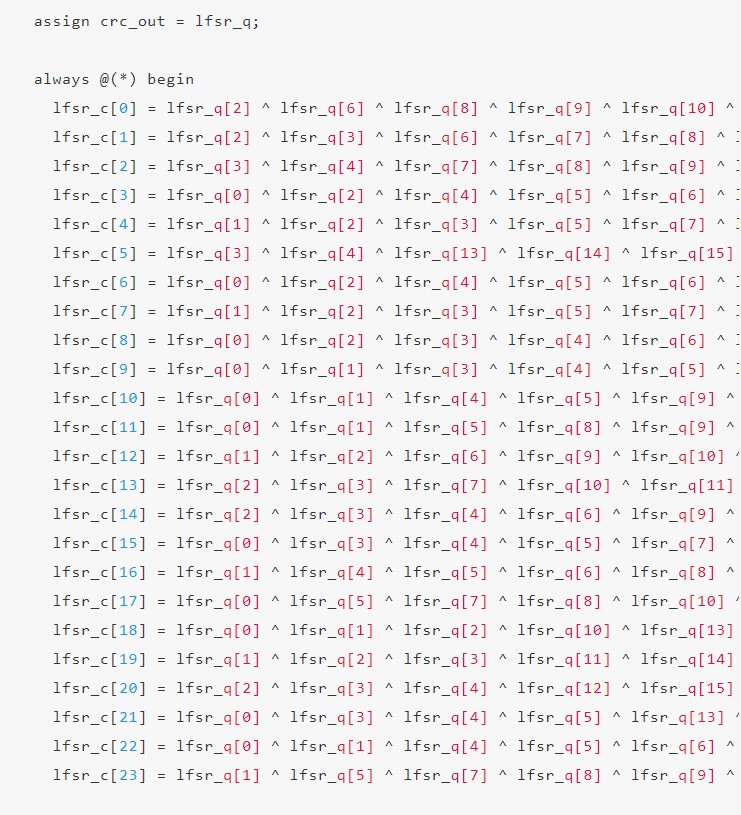

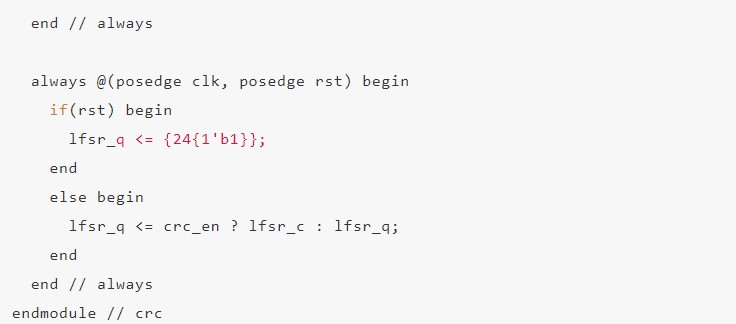

源代码如下:

赶紧试试吧,三分钟搞定CRC模块,效率直线上升码农。

原作者:刘多强