1、使用CMSDK搭建CortexM3SoC

需要软件

Modelsim-Intel FPGA Starter Edition 10.5b 综合工具

Xilinx FPGA: VIVADO 2018.2

Intel FPGA: Quartus Prime 19.1

Windows Subsystem for Linux(WSL)

make

minicom

软件编译调试工具

Keil uVision5

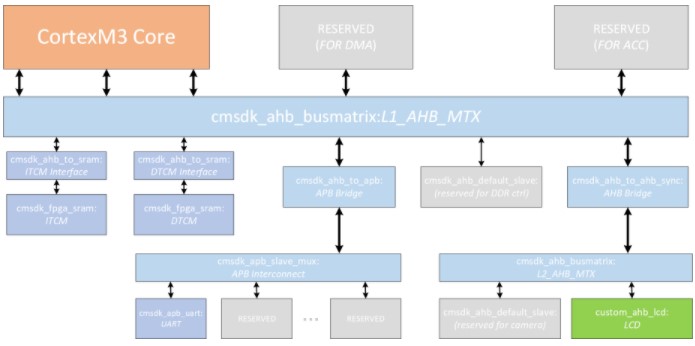

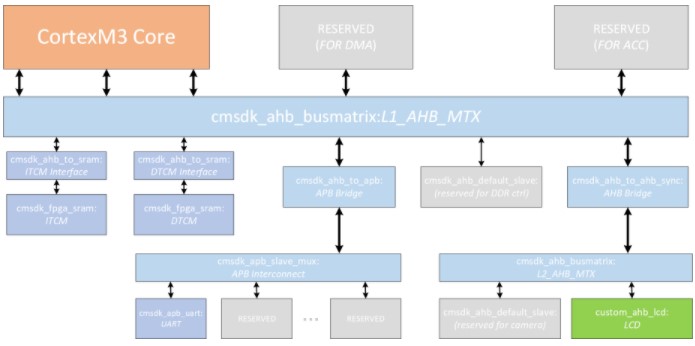

当前版本SoC架构

如下图所示,整个SoC基于CMSDK开发,除顶层模块与添加到自定义LCD外设模块外,无需添加或编写任何verilog代码。

当前版本SoC采用两级AHB总线:

第一级AHB总线矩阵上总共有5个SlavePort,分别连接CortexM3的ICODE、DCODE以及SYS总线Master,剩下两个SlavePort被设置为Default模式,预留给DMA与加速器;总共有5个MasterPort,分别连接I/D TCM总线接口、APB桥、AHB同步桥以及预留给DDR控制器的DefaultSlave。

第二级AHB总线矩阵只有1个SlavePort,连接AHB同步桥的Master接口;2个MasterPort分别连接预留给摄像头的DefaultSlave与自定义LCD屏幕的驱动硬件。

APB桥总共支持16个APB外设,目前只挂载了1个UART,剩余15个被设置为Default模式。

原作者:天津