在当前的RTL设计中,国内仍以Verilog/VHDL为主,且不可否认未来或许很长一段时间仍旧是以Verilog/VHDL为主。SpinalHDL作为一门新的硬件描述语言,其充分考虑了这一点,也为我们在SpinalHDL的设计中提供了集成现有RTL设计(IP)的渠道——BlackBox。

BlackBox

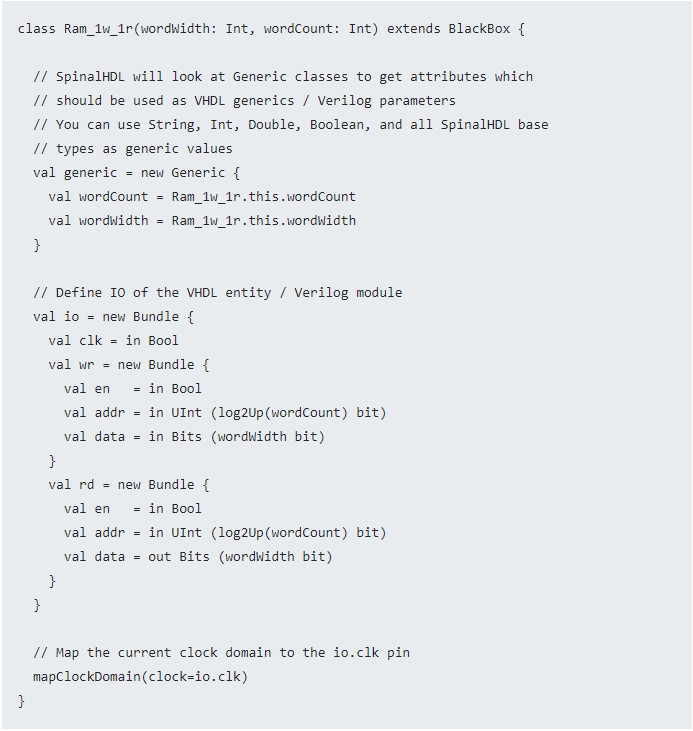

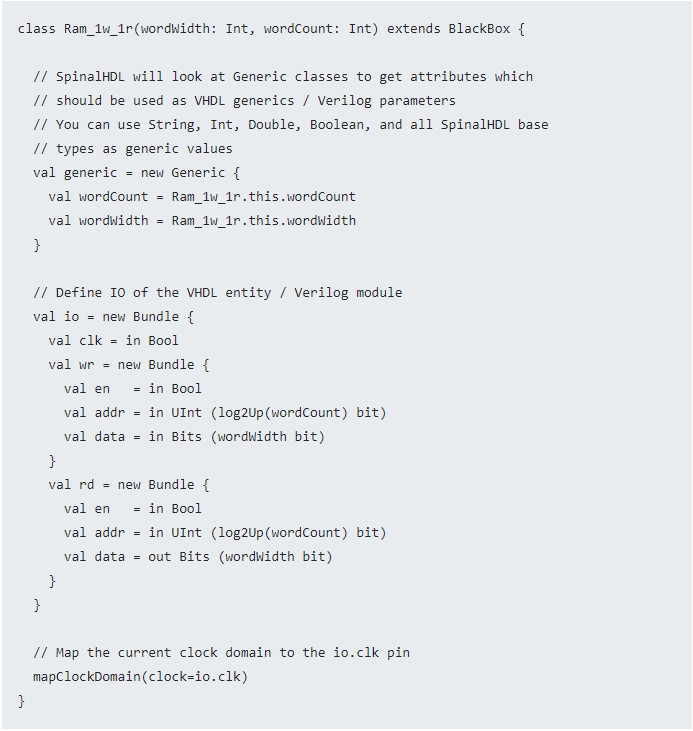

顾名思义,SpinalHDL将待集成的RTL设计当作一个黑盒对待,不关心内部的设计,只关心顶层接口及parameter参数(这也是我们在RTL里例化IP时常用的)。我们来看SpinalHDL-doc给出的example:

整个代码里做了三件事:参数声明、端口声明,时钟域映射。

参数声明

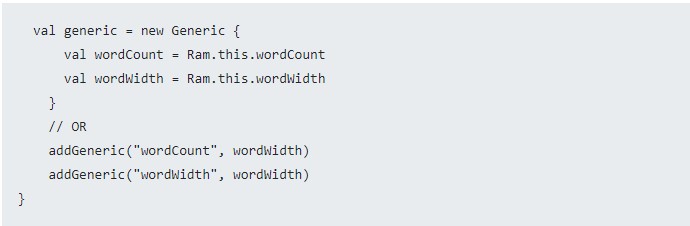

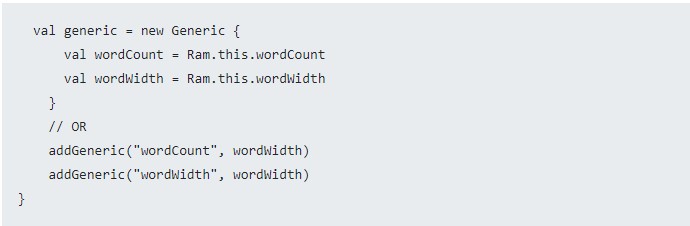

在上例中,Ram_1w_1r IP包含两个参数wordCount、wordWidth,在SpinalHDL里需要将参数“透传”给IP用于在例化时使用,在SpinalHDL里通过Generic来实现,它提供了两种方式(个人更倾向第二种):

端口声明

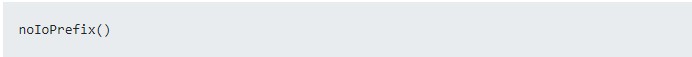

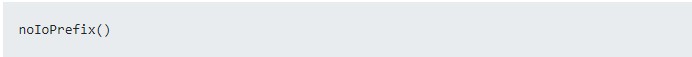

端口声明无特别指出,仅仅是将待集成的IP的端口进行重新声明即可,有一点值得注意的是在上例中例化时端口名会带有“io_”前缀,欲避免该问题可添加下述语句:

时钟域映射

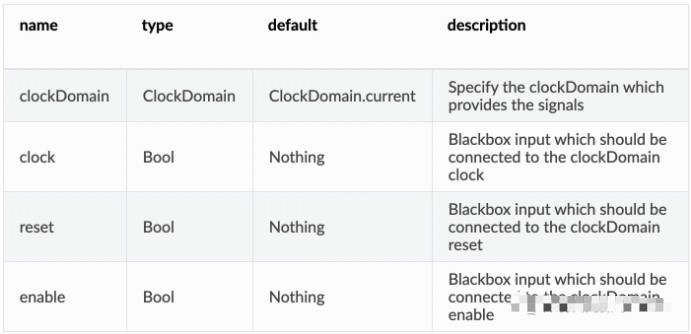

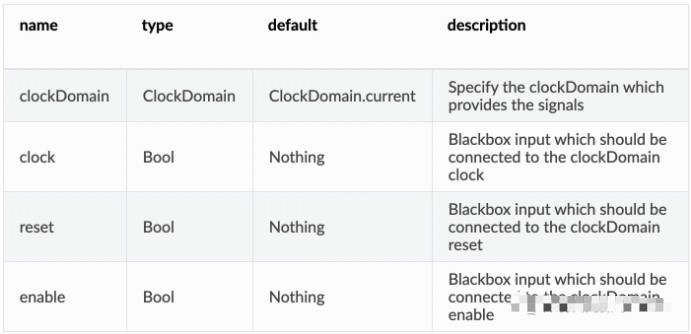

在集成IP时需显示映射IP的时钟与复位信号,SpinalHDL提供了mapClockDomain、mapCurrentClockDomain两个函数用于时钟映射,mapClockDomain参数列表如下(mapCurrentClockDomain除了不包含clockDomain外无差别):

指定IP代码路径

SpinalHDL集成Verilator

仿真器仿真接口,在对带RTL IP的代码进行仿真时,需指定RTL IP代码的路径,SpinalHDL提供了addRTLPath()函数用于集成RTL IP:

IP 例化

对于IP的例化在SpinalHDL里无差别,如下例所示:

个人改进

在上例中,20~25行仍像在写RTL代码时进行连线,如果这个IP在整个工程例使用一次还好,如果调用很多次岂不是又回到Verilog里成了“连线工程师”?

解决这一麻烦的方式可借助Scala的伴生对象。下面给出一个小的example,在SpinalHDL例例化一个带层次结构的RTL代码(RTL代码本身没什么意义,主要展示带层次结构的RTL代码在SpinalHDL中设计仿真的实现)。

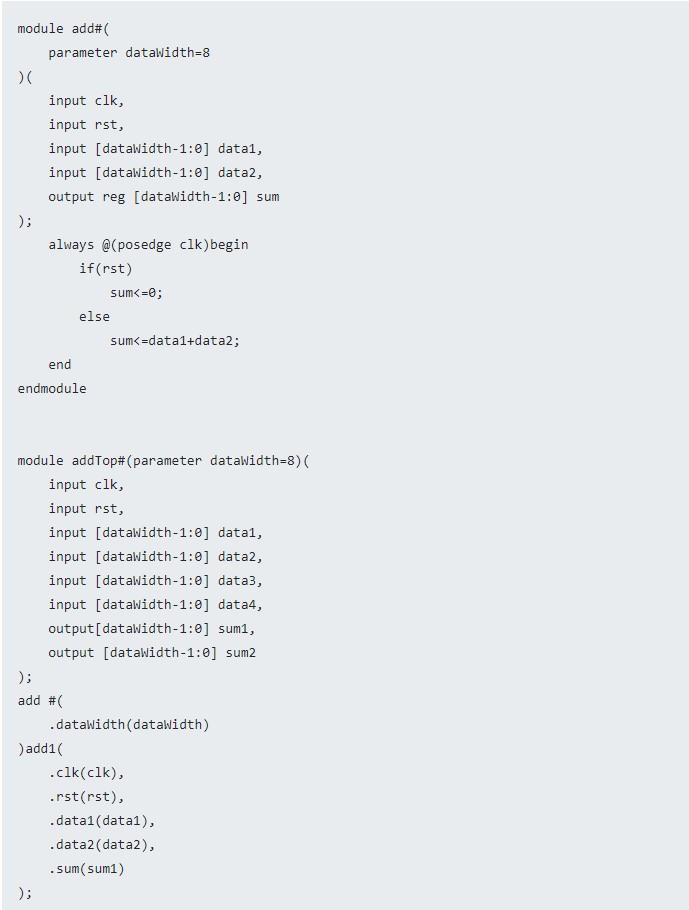

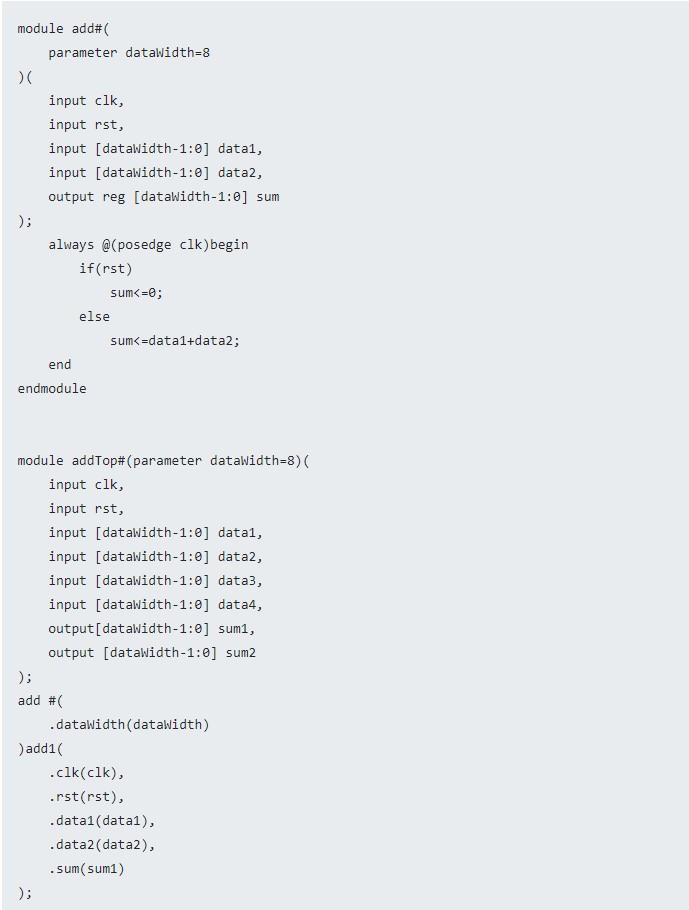

RTL代码分两个文件:

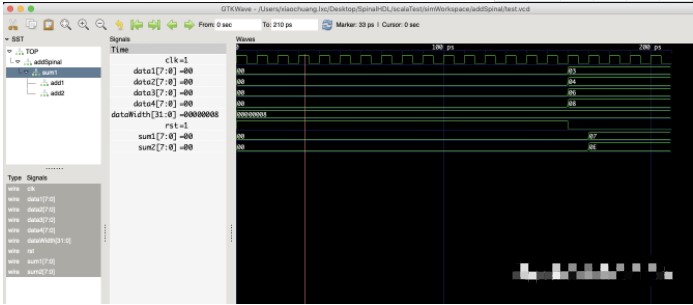

SpinalHDL IP集成:

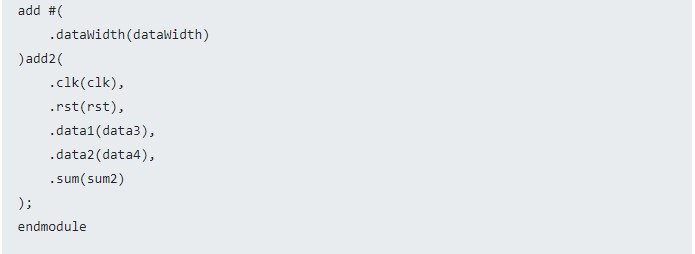

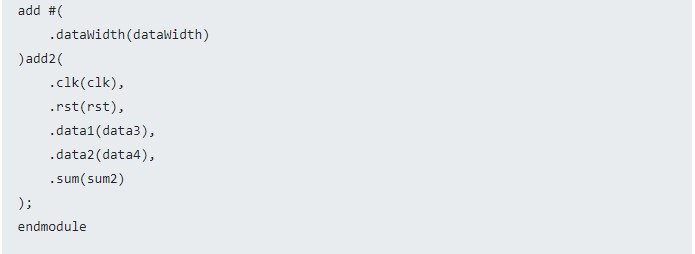

在上述SpinaHDL代码例,定义了addTop类用于集成Verilog 代码,同时定义伴生对象addTop,用于在IP例化时使用。伴生对象中的apply函数里进行IP端口连线,例化时仅需像40行所示将端口放进参数列表里即可。生成的RTL代码如下:

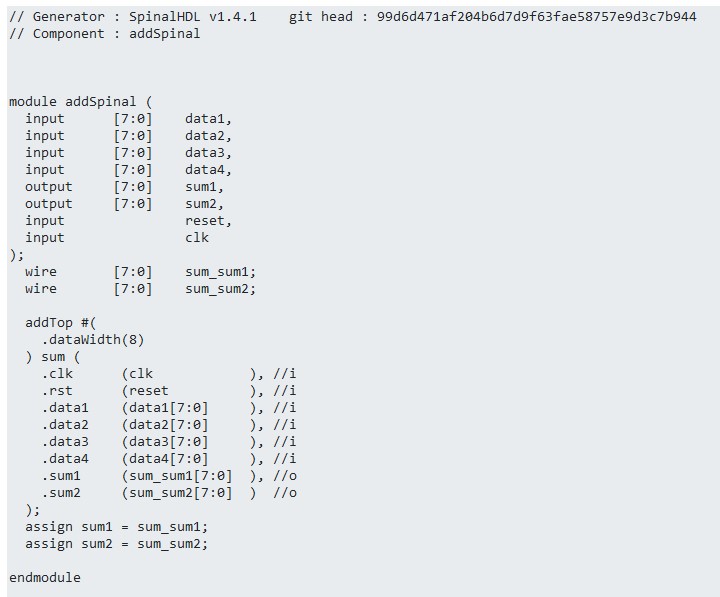

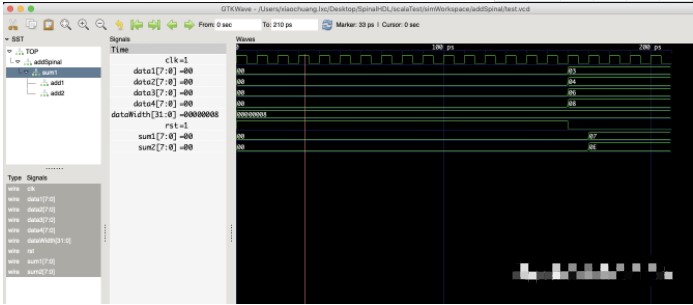

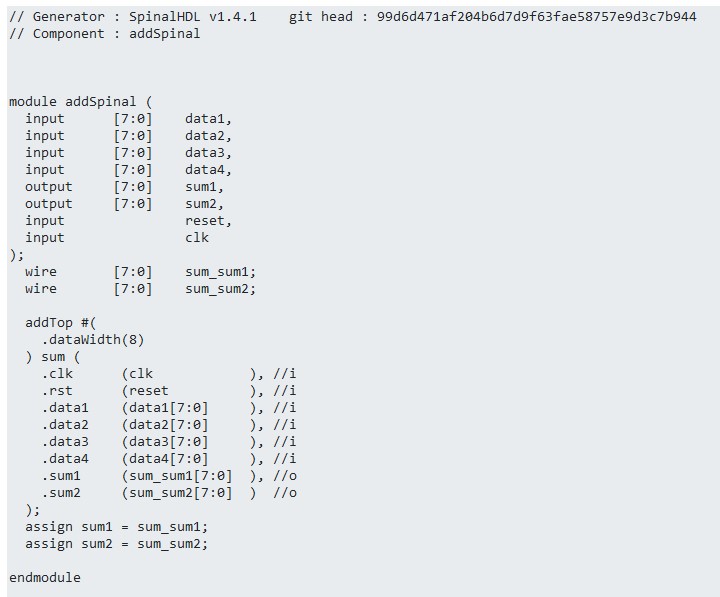

同时做***代码里面的信号均可获取到:

END

原作者:玉骐