CA-IS3092W是集成隔离电源的隔离式RS-485/RS-422收发器,隔离电源的输出VISO有5V和3.3V两种选项,通过SEL管脚选择,可提供最大负载100mA。芯片内置微变压器,由于变压器尺寸和功率的限制,通过微型变压器的开关频率相对较高,到约70MHz。短时间内大电流的切换会产生电磁辐射,引起较大的di/dt及di/dt噪声。器件工作所产生的噪声落在30MHz至1GHz范围内,产生辐射干扰问题。

通过合适的PCB布局和其他方法的设计,此产品可以满足在非屏蔽应用环境下的EN55032的classA类辐射标准。下面介绍几种抑制辐射的方法。

本文仅仅从电路上总结抑制辐射干扰的办法,在芯片应用中,整体方案可以加法拉第屏蔽罩,大幅度降低辐射干扰。

GNDA 和 GNDB 拼接电容

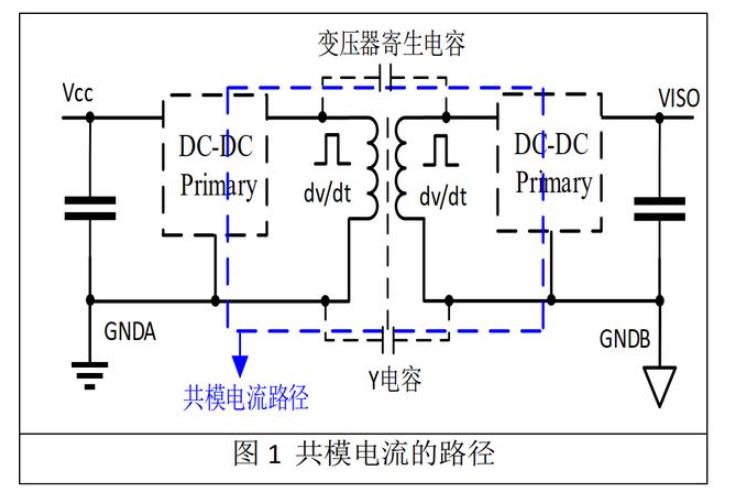

芯片内部开关器件是其中一个噪声源,芯片内置的微型变压器是另外一个噪声源。理想的变压器,仅仅流过变压器原边线圈中的电流耦合到副边。但是,微型变压器的漏感及初级的层间电容、原副边之间的耦合电容等寄生参数则为寄生电流提供了耦合到副边的通道。如果有一条通路,为这些寄生电流提供返回原边的路径,那么将不会产生很大的辐射。如果没有这种路径,这些寄生电流成为在次级侧输出 VISO 和 GNDB 上的共模电流,这些共模电流会形成偶极天线,产生较强的辐射干扰。

CA-3092W 芯片内部已经做了相应的优化措施, 尽可能地降低辐射干扰。在芯片应用时,如果在原边地和副边地之间加入 Y 电容, 这些次级侧的共模电流被 Y 电容旁路,返回初级。 Y 电容为共模电流提供一个低阻抗返回路径, 大大降低辐射干扰。 Y 电容越大,相对效果越好。 隔离栅上的拼接电容为共模电流提供必要的低阻抗返回路径,同时系统仍能保持所需的高压隔离,如图1 所示。

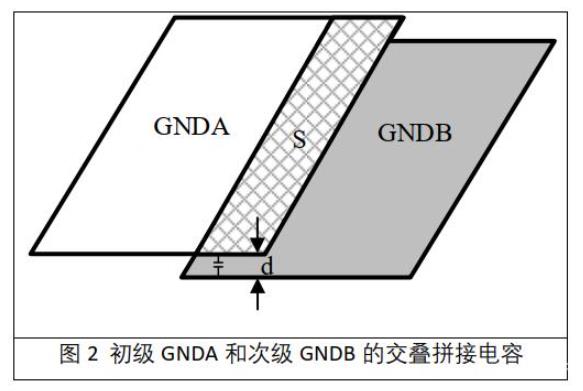

分立器件的 Y 电容耐压存在分布电感, 导致高频特性效果稍差。 使用 PCB 拼接电容更为可靠的一种方式。 当 PCB 的两信号层大面积覆铜交叠时,就会形成一个电容。 这种拼接电容,分布电感极低,高频特性比较好,可以覆盖较宽的频率。 拼接电容量计算如下:C=εr*ε0*S*/d 。

其中:

εr 为 PCB 两层信号层的相对介电常数, 对于常用的 FR4 材料,其值约为 4.5;

ε0为自由空间的介电常数 8.854*10-12F/m;

S 为两层信号层的交叠面积;

d 为两信号层的相对间距。

拼接电容的大小与铜箔厚度关系不大,使用常规1OZ 厚度的铜箔即可。 如当 d 为 0.000456m, S 约为0.0022m2, 计算拼接电容为C=4.5*8.544*0.0022/0.000465pF=181.9pF。

初级地平面层和次级地平面层交叠,形式拼接电容。 由于爬电距离和电气距离的要求,此拼接电容的距离应不低于 0.4mm。 对于 4 层 PCB,一般应置于中间两层。如图 2 所示。

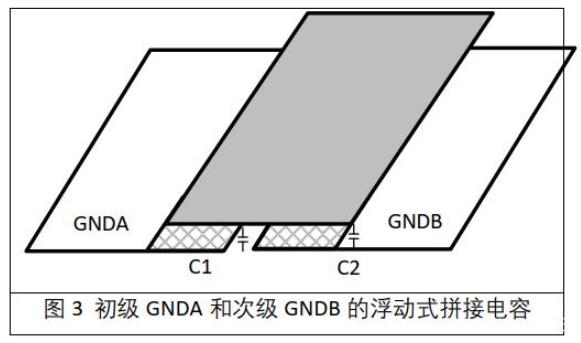

拼接电容除了上述交叠的方式, 也可以采用浮动式的拼接方式来实现。 如图 3 所示。总的拼接电容相当于 C1 和 C2 的串联效果。

实验表明, 拼接电容提供了共模电电流返回初级侧的路径,减少对外辐射, 对于改善 RE 辐射起到较大的作用。

举报

举报

举报

举报