一.内存接口的概念

S3C2440是SOC,所以会有很多外设,一般驱动外设的方法可以分为:

通过CPU访问相应的的寄存器,然后通过控制器驱动外设

CPU直接访问外设地址,驱动外设

后一种访问方式是CPU直接对内存地址的访问,即通过内存接口访问外设,CPU通过片选线选定外设,通过地址线先选定地址,通过数据线进行控制。

我们称这种外设为内存类设备,通常有:NOR FLASH、网卡、SDRAM……

那CPU是如何通过这些总线来驱动内存类设备呢?这就涉及到存储控制器了,下面就来介绍一下存储控制器的原理。

二.存储控制器(内存控制器)

2.1 什么是存储控制器?

存储控制器是按照一定的时序规则对存储器的访问进行必要控制的设备,包括地址信号、数据信号以及各种命令信号的控制,使主设备(访问存储器的设备)能够根据自己的要求使用存储器上的存储资源

存储控制器可以看作CPU与内存之间沟通的桥梁,CPU通过存储控制器来访问内存,比如GPIO、UART、IIC、SDRAM……都属于CPU的统一编址,地址都是CPU统一编排的(NAND FLASH不属于),所以CPU就可以通过存储控制器来访问这些外设的地址。

2.2 S3C2440存储控制器介绍

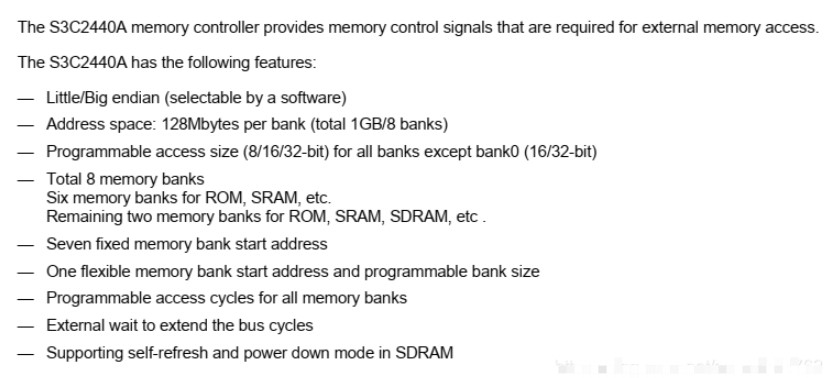

下面是S3C2440的存储控制器介绍:

其中主要的信息为:

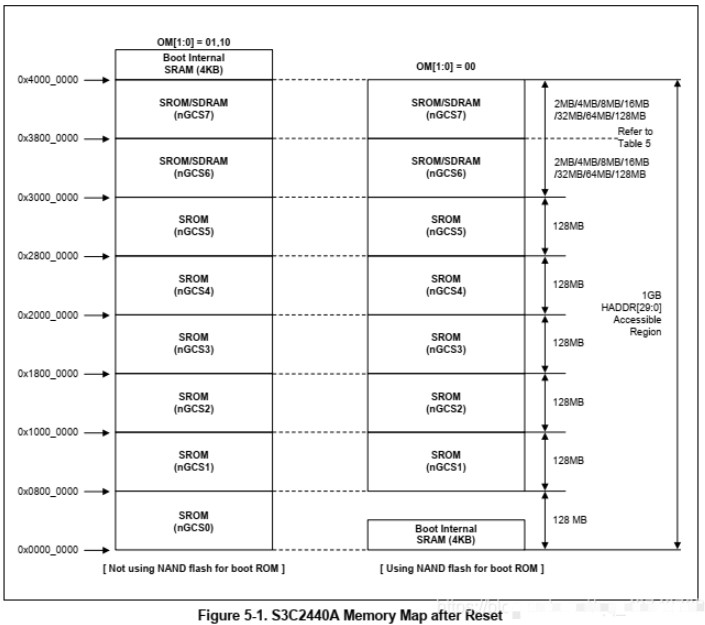

总共1GB的内存,分为8BANK,每个BANK的地址大小为128MB

BANK的位宽是可编程的

BANK0~BANK7的起始地址是固定的

此外,为了访问这1GB的空间,存储控制器引出了27根地址线ADDR0~ADDR27,这时候我们算一下:2^27=128M,这明明是一个BANK的空间呀,怎么可以访问8个BANK的空间呢?

其实还有8根片选线nGCS0~nGCS7,用来选择某一块BANK,就是8个BANK将1GB空间划分为8块128MB大小的空间,当访问某一块范围内的地址时,将此块的片选信号拉低就可以,这8个BANK的地址空间如下:

注意:S3C2440是32位CPU,理论上可使用的地址大小为4GB,除了上面这由于连接外设的1GB外,还有一部分空间是CPU内部寄存器使用了,剩下的地址空间没有使用。

2.3 存储控制器如何处理不同位宽的外设

有的外设位宽是8bit,有的是16bit,有的是32bit,当CPU访问这些外设的内存空间时,那要怎么办?要分情况来吗?

不需要,因为有存储控制器!CPU只需要向存储控制器提供地址,由存储控制器来解决不同位宽的问题。

以ROM为例:CPU想读取ROM中的某块地址中的数据,可ROM的位宽有8bit、16bit、32bit

下面对比一下三种位宽情况下ROM与存储控制器的接线情况:

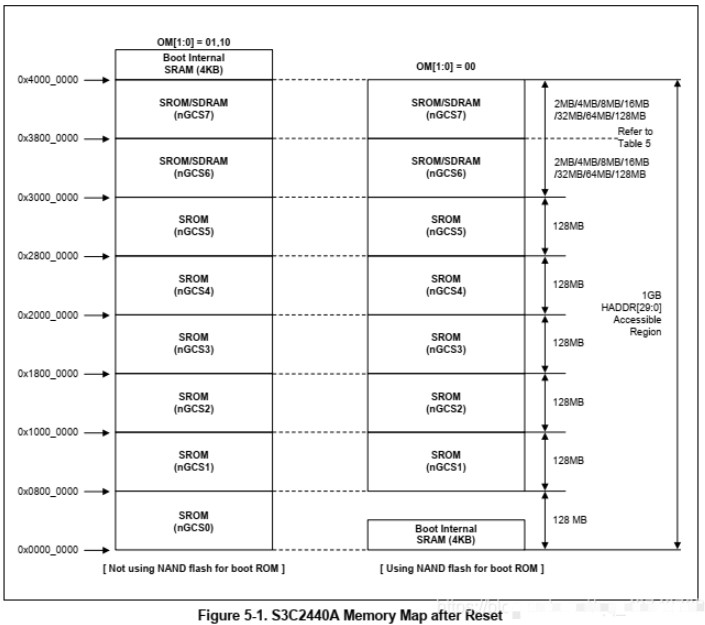

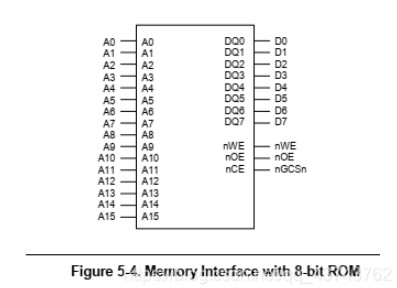

8bit:

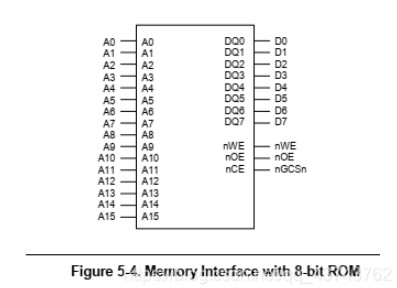

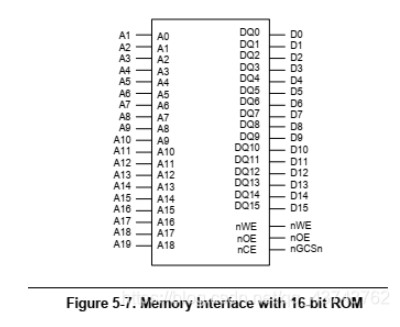

16bit:

32bit:

区别就是地址线的接法,8bit位宽是相对应的A0对A0;16bit位宽是从A1开始对齐的;32bit位宽是从A2开始对齐的,这是因为不同位宽的ROM内部构造不相同。

ROM的内部构造:

8bit带宽:每个地址的空间大小是8bit(1Byte);

16bit带宽:每个地址的空间大小是16bit(2Byte);

32bit带宽:每个地址的空间大小是32bit(4Byte);

表面上看到A0、A1没用到,实际上是起了别的作用:

8bit:内存控制器A0对应ROM的A0

16bit:内存控制器A1对应ROM的A0,内存控制器A0用来确定16bit(2Byte)中的哪一Byte

32bit:内存控制器A2对应ROM的A0,内存控制器A1A0用来确定32bit(4Byte)中的哪一Byte

实际上这些地址线都是有用的!!!

下面通过俩个例子来说明CPU在对不同位宽ROM读取数据时的差异。

例一:

#读取地址3的一个字节数据到R1寄存器

MOV Ro ,#3

LDRB R1, [R0]

读地址3的一个字节(LDRB 代表读取一个字节),CPU会将地址3发送给ROM(通过内存控制器),此时A2A1A0对应:011

8bitROM:A0对应A0,直接取出第三个数据,1Byte

16bitROM:A1对应A0,取出第一个数据,2Byte(一个地址16bit)

32bitROM:A2对应A0,取出第0个数据,4Byte(一个地址32bit)

取出的数据中 包含有我们想要的数据,由内存控制器筛选我们所需要的数据。

过程:CPU发出地址,ROM通过存储控制器收到地址,ROM返回数据给存储控制器,存储控制器筛选所需要的数据,存储控制器返回有用数据给CPU。

存储控制器操作16bit、32bit时会根据A0、A1的信息筛选出所需数据给CPU。

例二:

#从地址4开始读取32bit数据(4Byte)

mov R0, #4

LDR R1, [R0]

CPU去地址4开始读取4Byte数据(32位ARM),地址是以Byte为单位的,地址4就是第四个Byte,此时A2A1A0对应:100

8bit:发送四次地址给ROM,每次得到一个ROM返回的字节(8bit),内存控制器整合4Byte数据

16bit:发送俩次地址给ROM,每次得到俩个ROM返回的字节(16bit),内存控制器整合得到4Byte数据

32bit:发送一次地址给ROM,ROM返回四个字节(32bit),正好是地址4开始的4Byte数据

过程:CPU发出地址给内存控制器,内存控制器收到地址转发给ROM,ROM返回数据,内存控制器组装数据后返回CPU。

2.4 怎么确定芯片的访问地址?

第一步:根据片选信号确定基地址(每个片选线确定的地址块有128MB)

第二步:根据芯片所接地址线确定范围(27根地址线)

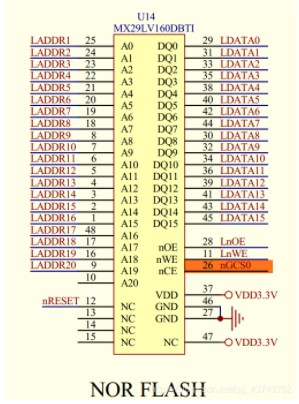

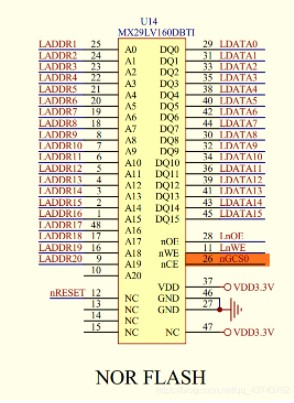

比如:Nor FLASH

片选线0,基地址0X0000_0000,因为这个NOR FLASH是16位的,所以内存控制器的LADDR1接A0,LADDR0用来选择低八位还是高八位。

用到A0~A20总共21条地址线,所以NOR FLASH地址范围是:基地址+地址线确定的范围

即:0X0000_0000~0X001f_ffff 2^21=2M空间。

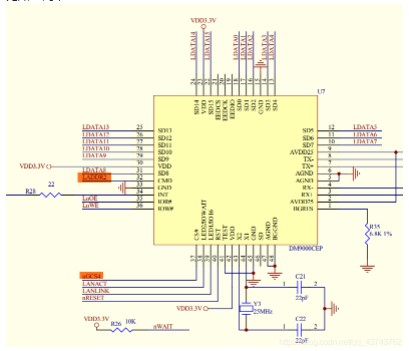

比如:网卡NET

基地址是nGCS4:0X2000_0000 内存控制器的地址线只接了LADDR2,16位数据线,意味着LADDR0也用到了。

网卡的地址范围:基地址+0b000~基地址+0b101 (LADDR1的位置无所谓)即:0X2000_0000~0X2000_0005

访问这些地址就可以访问到DM9000网卡

比如:SDRAM

SDRAM输出是32位,所以LADDR0、LADDR1已经包含了,加上LADDR2~LADDR14、LADDR24、LADDR25总共17条地址线,2^17=128k ,然鹅SDRAM是64M的,实际上是行地址和列地址。(这个问题会在下篇博客中细细分析)

三.时序问题

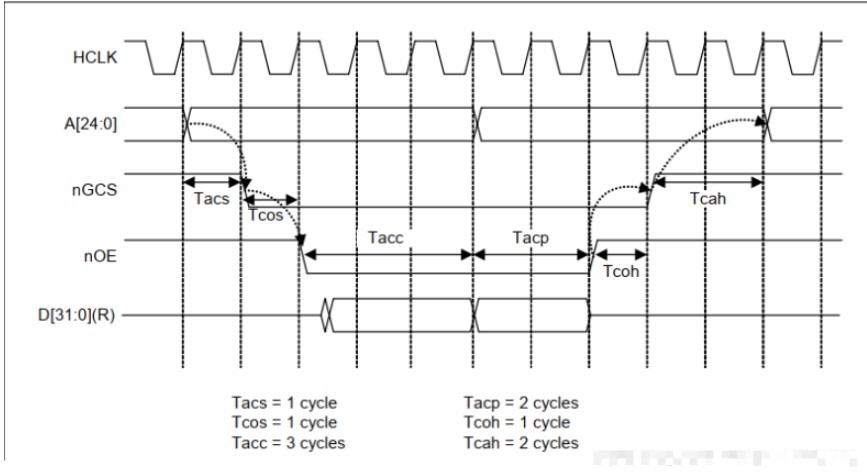

以NOR FLASH读时序为例:

内存控制器与NOR FLASH有地址线LADDRx、数据线LDATAx、片选信号nGCS0、读信号LnOE、写信号LnWE

这些信号控制线协调工作。

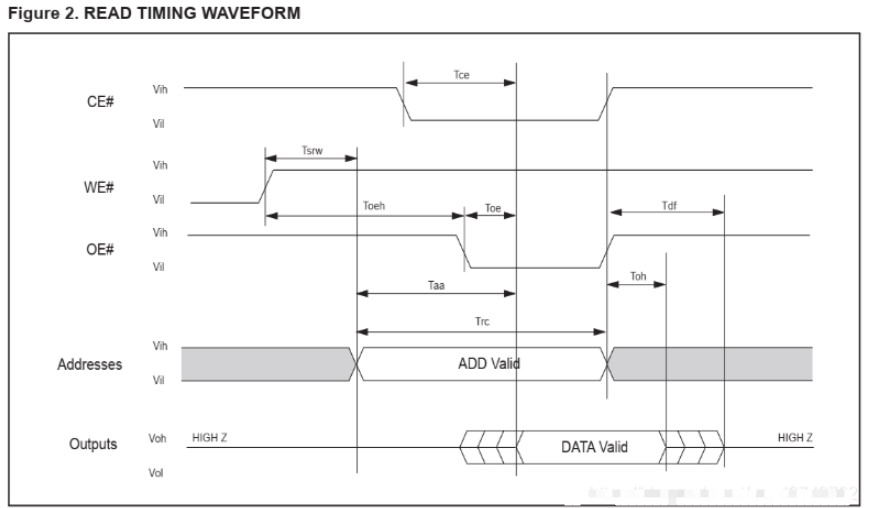

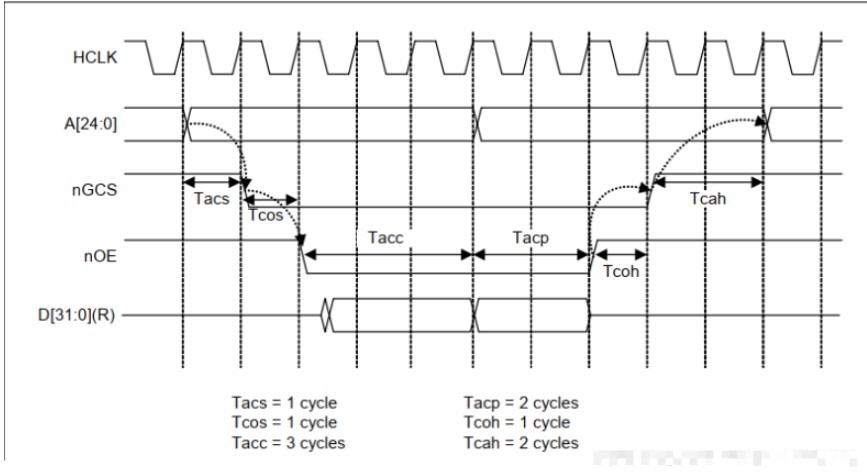

下面是芯片手册中存储控制器对芯片读数据时的时序图:

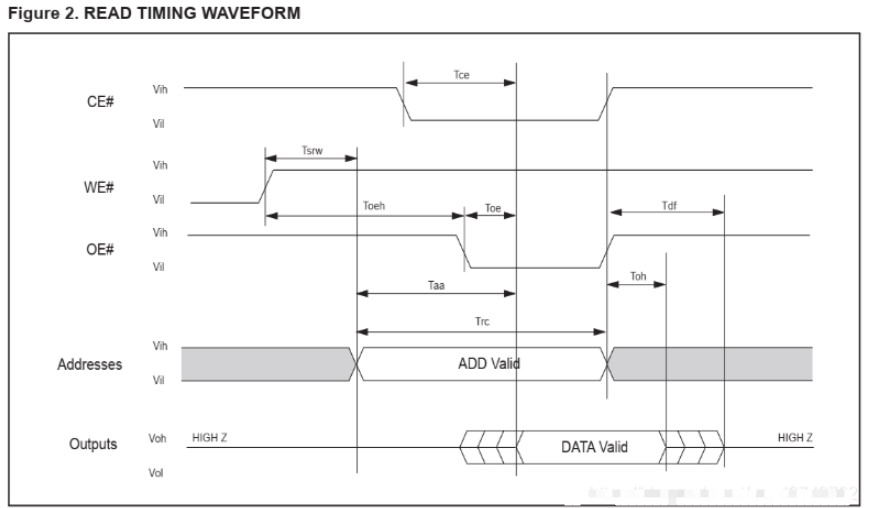

各个信号的持续时间根据外设芯片的性能有差异,可以根据具体芯片的手册进行设置,比如NOR FLASH:

(读时序)

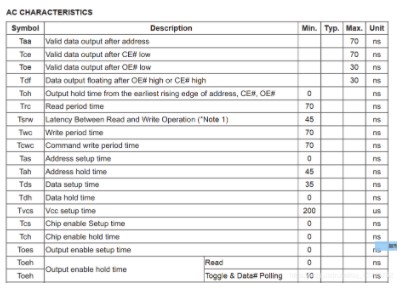

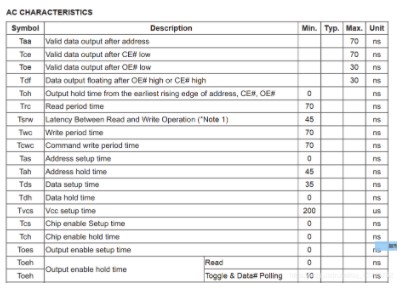

对照AC特性:

然后就是配置各个信号线的时序:

可以看出,Taa=70ns时,同时发出保证了片选线、读信号线、地址线的时序,可以得到有效的数据

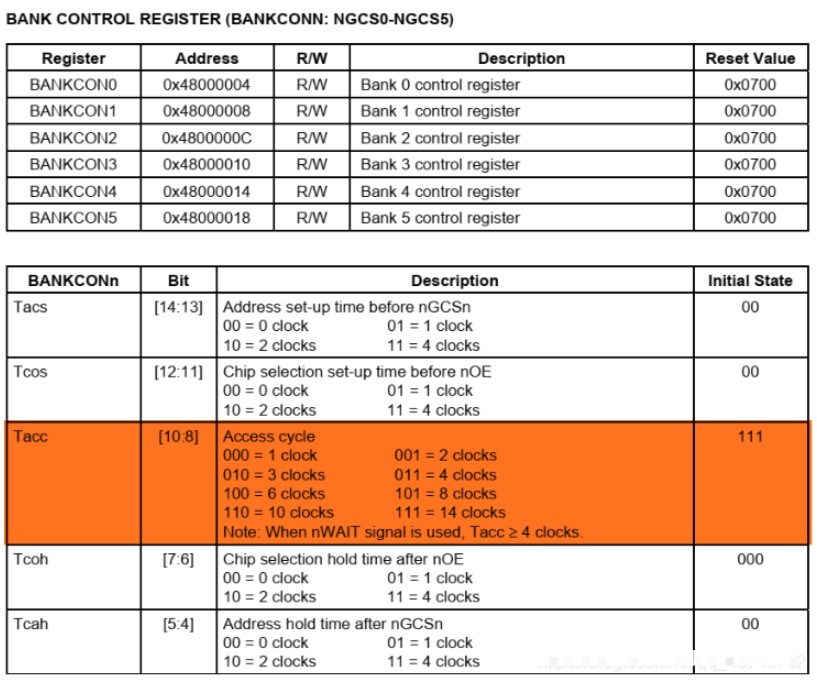

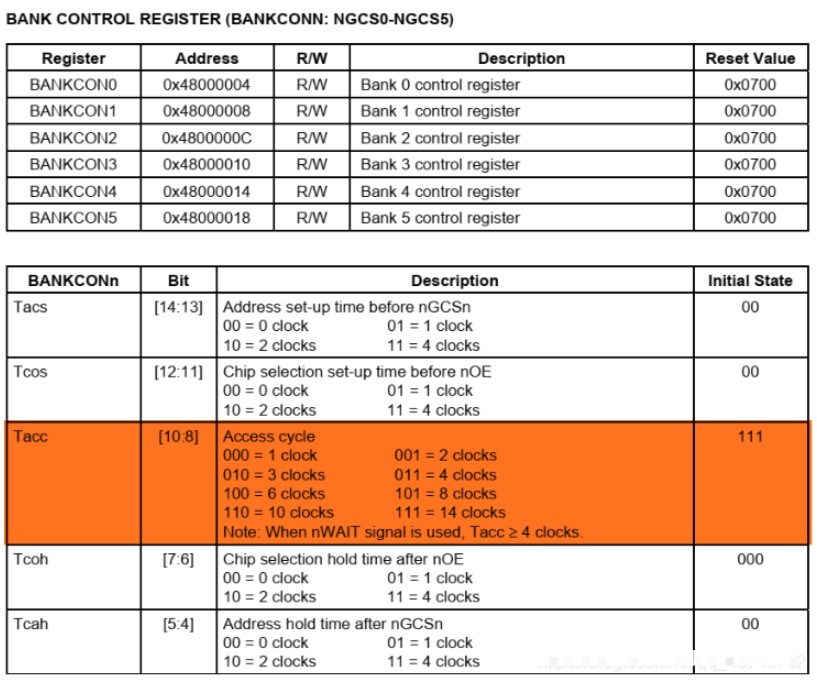

设置寄存器:

板子默认是14clocks,上电时,HCLK默认晶振12MHz,此时的Tacc=1166ns,相当于牺牲了性能来满足各种NOR FLASH。

我们配置当HCLK=100MHz时,1clock=10ns 所以选择8clock:101。

按照寄存器直接配置就可以了,可以通过烧写NOR FLASH的速度来体现时序中Tacc的影响。

原作者:Aspirant-GQ