什么是ARM流水线

流水线(Pipelining)是 RISC(精简指令集)处理器用来执行指令的机制,通过获取指令来加速执行,而其他指令同时被解码和执行。这反过来又允许内存系统和处理器连续工作。每个 ARM 系列的流水线设计都不同。

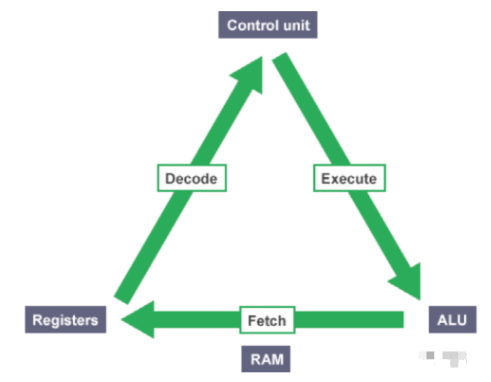

流水线是一种设计技术或过程,它在提高计算机和微控制器处理器中的数据处理效率方面发挥着重要作用。通过将处理器保持在一个连续的获取、解码和执行过程中,称为(FETCH-DECODE-EXECUTE(F&E) 循环)。

由于 RISC 强调编译器的复杂性,ARM 器件需要流水线。每一级流水相当于1个周期,即n个阶段=n个周期。

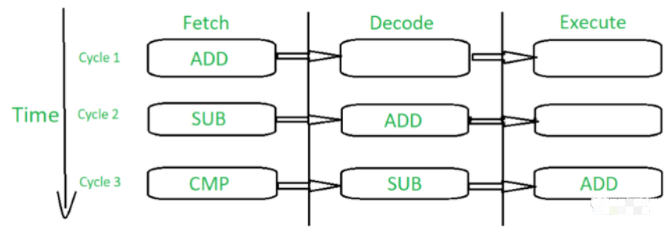

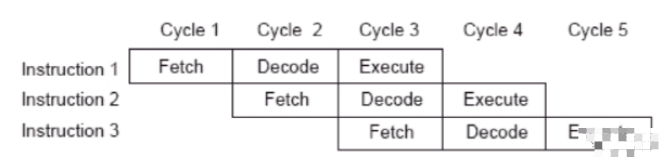

图1 三级流水线示意图

如图1,Fetch (取指)从内存中加载一条指令;Decode(译码)识别要执行的指令;Execute (执行)处理指令并将结果write back(写回)到寄存器;通过重叠执行不同指令的上述不同阶段,提高了执行速度。

图2 F&E循环示意图

ARM 流水线特性

ARM 流水线在完全通过execution stage之前不会处理该指令。在执行阶段,PC总是指向指令地址+8字节;当处理器处于thumb state时,PC 总是指向指令地址 + 4 个字节;在执行分支指令或通过直接修改 PC 进行分支时,会导致 ARM 内核刷新它的流水线;即使已引发中断,执行阶段的指令也会完成其执行。

ARM7系列

如图1所示,它有 3 级流水线。它可以在3个周期内完成它的过程。它具有基本的 FETCH-DECODE-EXECUTE(F&E) 循环。这就是为什么 ARM 7 的吞吐量低于其其他家族成员的原因。它处理 32 位数据。

ARM 9系列

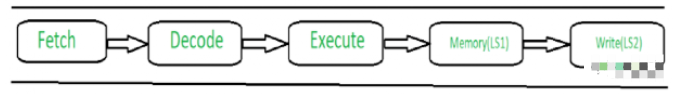

图3 五级流水线示意图

ARM 9 中的流水线与 ARM 7 类似,但ARM 9有 5 个阶段,完成该过程需要5个周期。Fetch(取值)-它将从内存中获取指令。Decode(解码) - 它解码在第一个周期中获取的指令。ALU(arithmetic logic unit,即算术逻辑单元) - 它执行(Execute)在前一阶段已解码的指令。LS1(Memory) 加载/存储由加载或存储指令指定的数据。LS2(Write) 提取(零或符号)扩展由字节或半字加载指令加载的数据。由于阶段和效率的增加,吞吐量比 ARM 7 高 10%-13%。ARM 9 的核心频率略高于 ARM 7。

ARM 10系列

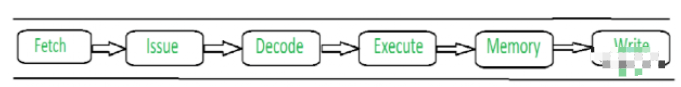

图4 六级流水线示意图

这是一个六级流水线。这又需要 6 个周期才能完成该过程。与 ARM 9 相同,但有一个issue阶段,用于检查指令是否准备好在以便当前阶段解码。它的吞吐量几乎是 ARM 7 的两倍。核心频率高于ARM 9。流水线的阶段数量可能会根据每个周期处理的指令集增加或减少(在大多数情况下,阶段倾向于增加以提高效率)。

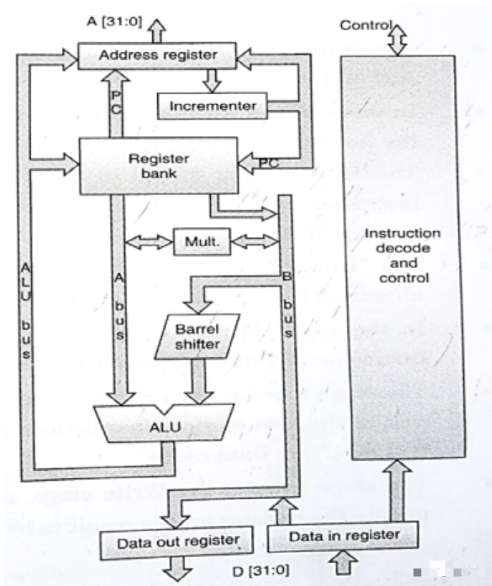

基本ARM微架构

图5 某arm微架构示意图

Barrel Shifter:Barrel Shifter(桶形移位器)是一种数字电路,可以将数据字移位指定位数,而无需使用任何时序逻辑,仅使用纯组合逻辑,即它固有地提供二进制操作。

ALU:该单元执行各种算术和逻辑运算。

Address register and increment:寄存器存储地址,增量器递增相同以指向下一条指令。

Data register:数据寄存器,当数据写入内存或从内存中读取时,它用作一个缓冲区来存储数据。

Instruction Decoder:顾名思义,它对指令进行解码并相应地发出控制信号。因此,指令解码器与发出控制信号的控制逻辑相关联。指令通过数据总线(在底部)获取并提供给指令解码和控制单元。该单元对指令进行解码,,然后指令由 ALU、乘法器和桶形移位器使用寄存器组中的寄存器执行。

CPI和MIPS

CPI( Clock cycle Per Instruction)表示每条计算机指令执行所需的时钟周期,有时简称为指令的平均周期数。可以用来表示CPU的性能。对CPU来说,在一个时钟周期内,CPU仅完成一个最基本的动作。时钟脉冲是计算机的基本工作脉冲,控制着计算机的工作节奏。时钟频率越高,时钟周期就越短,工作速度也就越快。

MIPS是每秒钟处理了多少百万条指令,计算公式:MIPS=主频/CPI * 10的6次方。

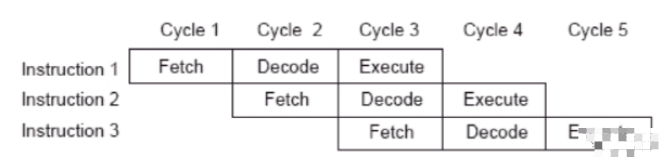

从流水线的角度理解建立时间

建立时间的含义:一个时钟周期内,一级流水的指令执行必须完成;否则可能会出现数据冒险,因为不同指令的流水的不同stage是重叠执行的。

图6 流水线的重叠执行示意图