STM32时钟树

问题1:为什么需要时钟?

答:STM 32的时钟系统类似于人的心脏,需要为芯片提供时钟芯片才能正常工作,而STM32有很多的外设,如果像51单片机那样所有外设共用一个时钟系统的话,那么有些外设用不到那么高的频率,这样便会造成更高的功耗。在同一个电路,时钟越高功耗越大,抗干扰能力也越低,因此STM32采用不同的时钟来为不同的外设提供不同的时钟频率。

时钟树相关知识基础:

STM32有5个时钟源,分别是:1、HSE:高速外部时钟 2、HSI:高速内部时钟 3、LSE:低速外部时钟 4、LSI:低速外部时钟 5、PLL锁相环输出。

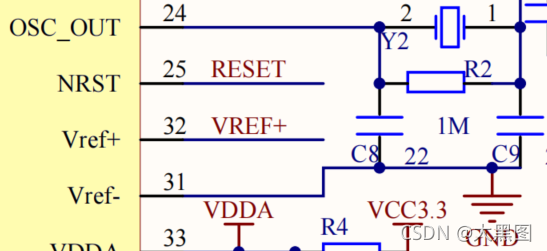

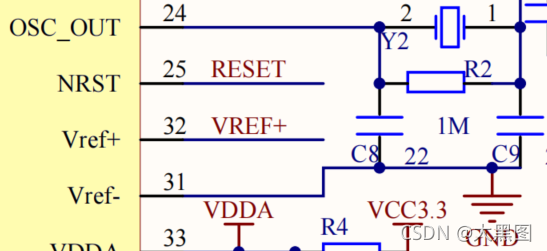

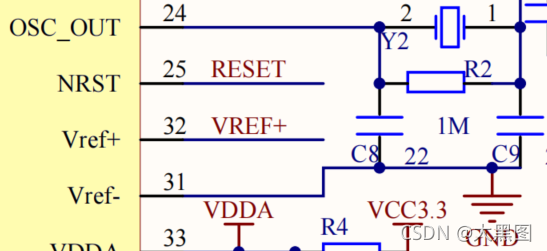

其中HSE的来源为外接晶振,可以选择晶振频率范围为4~16MHZ,一般选择8MHZ。当使用无源晶振时,晶振接STM32的OSC_IN和OSC_OUT引脚,并在晶振两端分别接两个22pF的电容。电路如下图所示。

HSI的时钟来源为内部RC振荡器,频率为8MHZ,精度较低并且容易受温度影响。

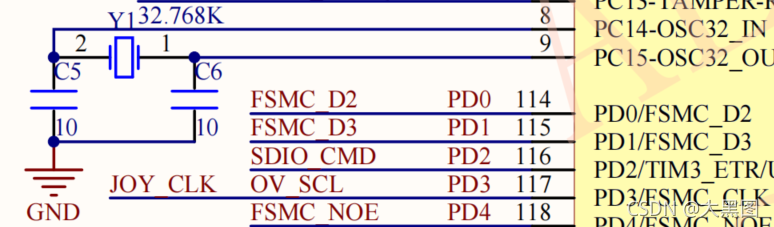

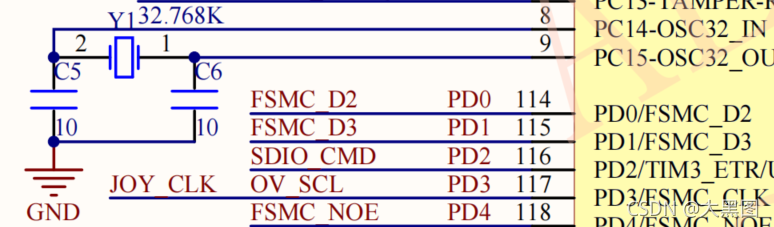

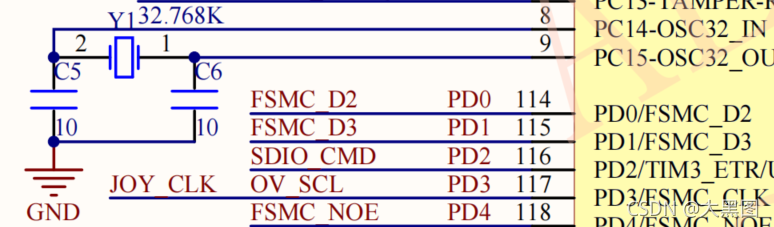

LSE的时钟来源为外接晶振,频率为32.768KHZ,用于RTC时钟。电路如下图所示。

HSI的时钟来源为内部RC振荡器,频率为8MHZ,精度较低并且容易受温度影响。

LSE的时钟来源为外接晶振,频率为32.768KHZ,用于RTC时钟。电路如下图所示。

LSI的时钟来源为内部RC振荡器,频率为40kHZ ,常用于独立看门狗时钟。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。 倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。我们常用8M的外部晶振的9倍频,即72MHz作为系统时钟(SYSCLK)。

LSI的时钟来源为内部RC振荡器,频率为40kHZ ,常用于独立看门狗时钟。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。 倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。我们常用8M的外部晶振的9倍频,即72MHz作为系统时钟(SYSCLK)。

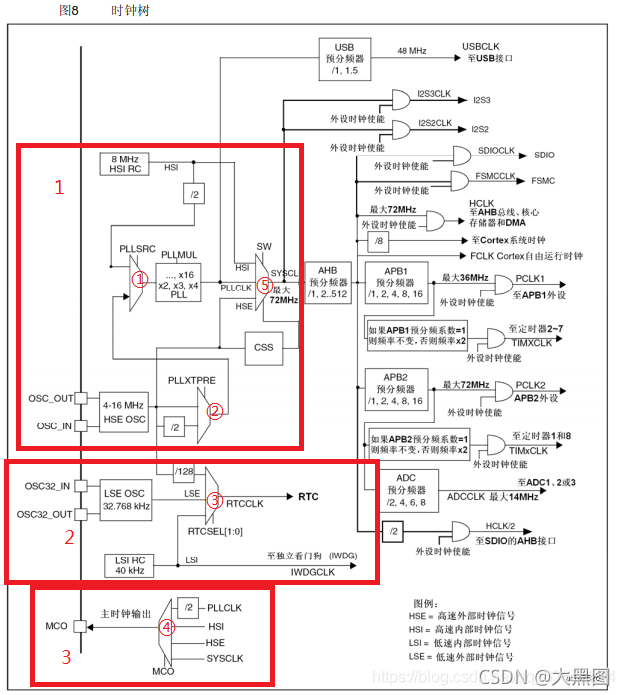

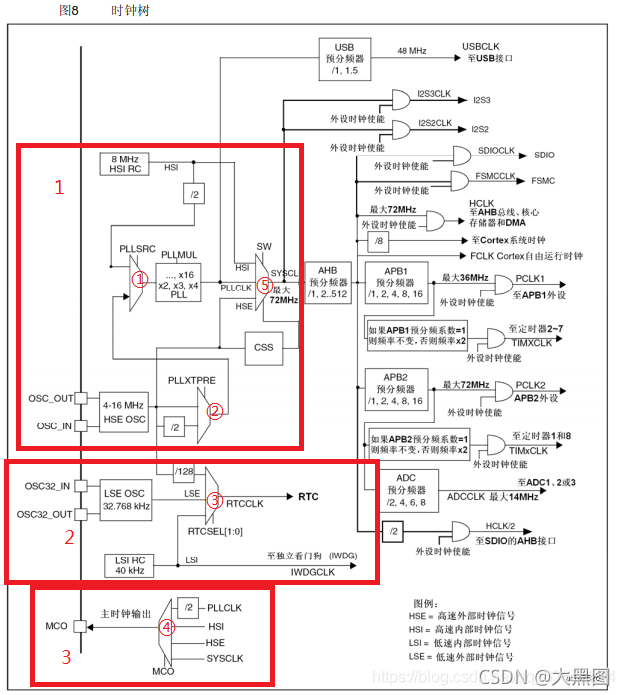

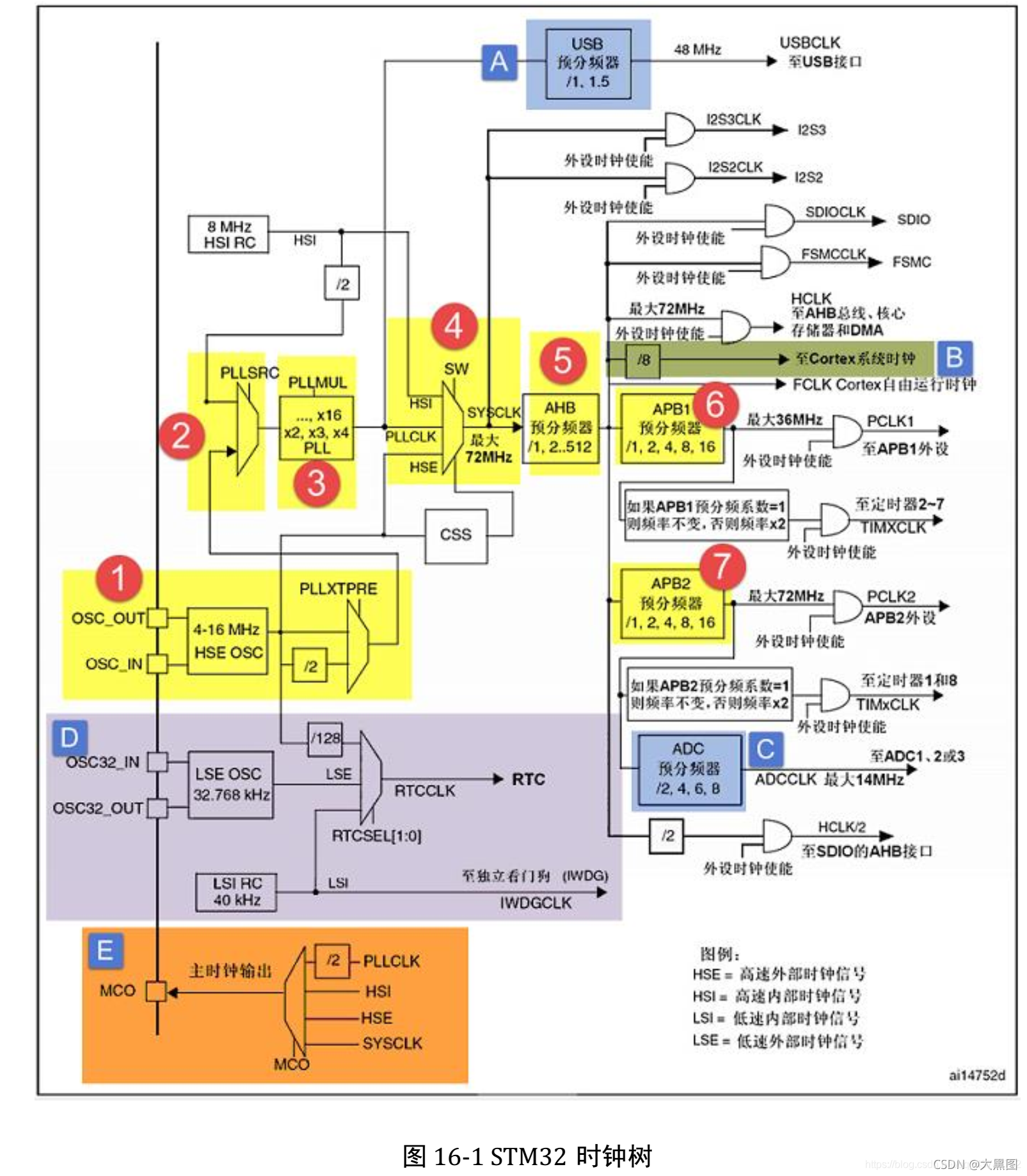

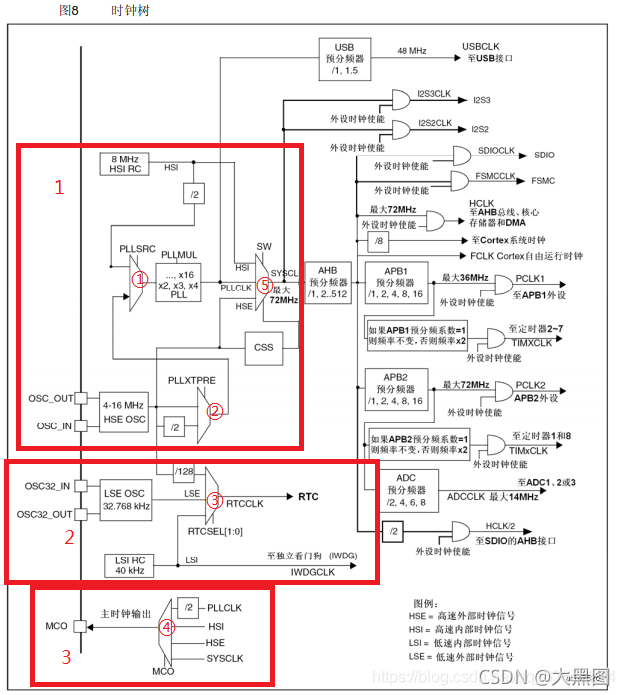

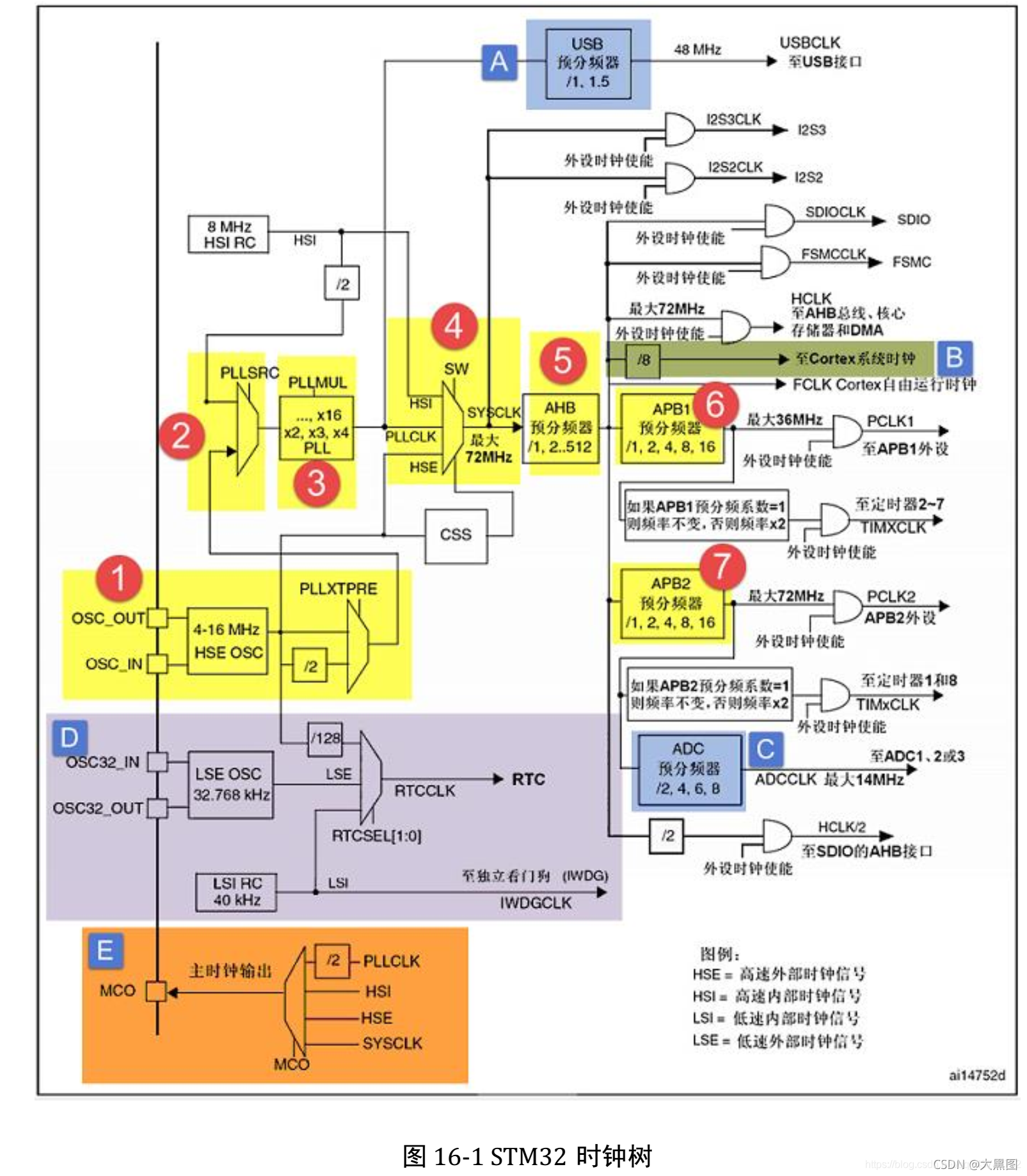

红框1中的OSC_OUT和OSC_IN接外部8M晶振(范围为4到16MHz)作为HSE(外部高速时钟),通过PLLXTPRE位可控制选择器②是输出HSE还是HSE/2,选择器①通过PLLSRC位控制,用来选择是HSI/2还是选择器②的输出作为倍频锁相环(PLLMUL控制倍频的倍数)的输入,我们一般都是(系统默认)配置为8Mhz的HSE作为倍频器的输入并选择9倍频产生72MHz的时钟PLLCLK作为系统时钟(SYSCLK),系统时钟经AHB预分频器(默认分频系数为1)得到HCLK,可作为部分外设的时钟,如SDIO,FSMC等,再经APB1,APB2预分频器可得到PCLK1、PCLK2。

PCLK1:APB1低速总线时钟,最高为36M。为APB1总线时钟的外设提供时钟。但又经过2倍频作为定时器2~7的时钟,所以定时器2到定时器7即使是在APB1下,也为72M的时钟。

PCLK2:APB2高速总线时钟,最高为72M。为APB2总线时钟的外设(包含定时器1和8)提供时钟。

PCLK2经ADC预分频器(/2,4,6,8)作为ADCCLK(最大为14M),我们常选择6分频(72/6=12M)

固件库配置时钟树步骤:(参考野火)

1.开启HSE,并等待HSE稳定;

2.设置AHB、APB1、APB2的预分频因子;

3.设置PLL的时钟来源和倍频因子;

4.开启PLL,并等待PLL稳定;

5.把PLLCLK切换为系统时钟SYSCLK;

6.读取时钟切换状态位,确保PLLCLK被选为系统时钟。

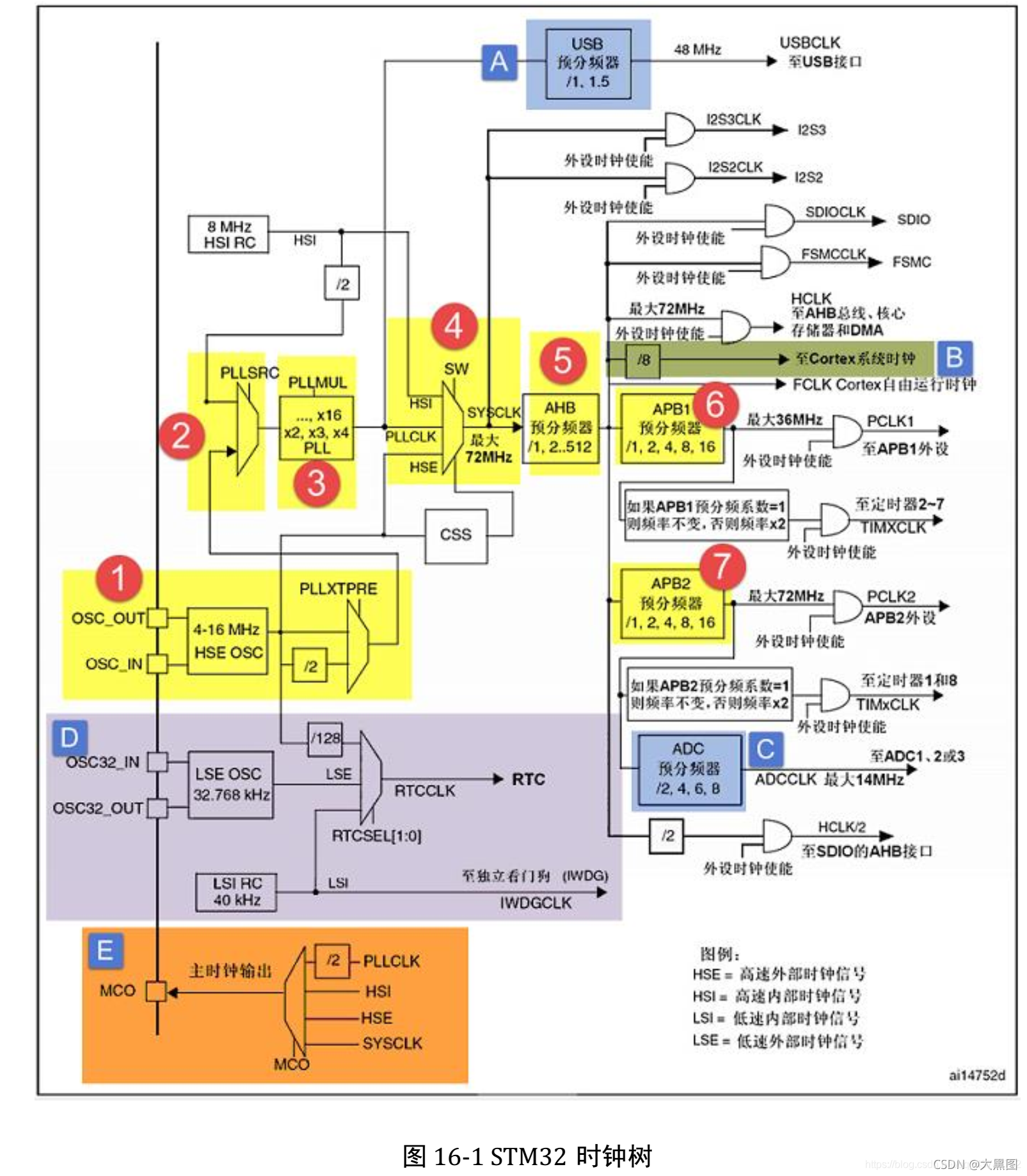

配置步骤参考下图中的1到7。

红框1中的OSC_OUT和OSC_IN接外部8M晶振(范围为4到16MHz)作为HSE(外部高速时钟),通过PLLXTPRE位可控制选择器②是输出HSE还是HSE/2,选择器①通过PLLSRC位控制,用来选择是HSI/2还是选择器②的输出作为倍频锁相环(PLLMUL控制倍频的倍数)的输入,我们一般都是(系统默认)配置为8Mhz的HSE作为倍频器的输入并选择9倍频产生72MHz的时钟PLLCLK作为系统时钟(SYSCLK),系统时钟经AHB预分频器(默认分频系数为1)得到HCLK,可作为部分外设的时钟,如SDIO,FSMC等,再经APB1,APB2预分频器可得到PCLK1、PCLK2。

PCLK1:APB1低速总线时钟,最高为36M。为APB1总线时钟的外设提供时钟。但又经过2倍频作为定时器2~7的时钟,所以定时器2到定时器7即使是在APB1下,也为72M的时钟。

PCLK2:APB2高速总线时钟,最高为72M。为APB2总线时钟的外设(包含定时器1和8)提供时钟。

PCLK2经ADC预分频器(/2,4,6,8)作为ADCCLK(最大为14M),我们常选择6分频(72/6=12M)

固件库配置时钟树步骤:(参考野火)

1.开启HSE,并等待HSE稳定;

2.设置AHB、APB1、APB2的预分频因子;

3.设置PLL的时钟来源和倍频因子;

4.开启PLL,并等待PLL稳定;

5.把PLLCLK切换为系统时钟SYSCLK;

6.读取时钟切换状态位,确保PLLCLK被选为系统时钟。

配置步骤参考下图中的1到7。

固件库配置时钟树参考代码

固件库配置时钟树参考代码

void HSE_SetSysClock(uint32_t pllmul)

2 {

3 __IO uint32_t StartUpCounter = 0, HSEStartUpStatus = 0;

4

5 // 把 RCC 外设初始化成复位状态

6 RCC_DeInit();

7

8 //使能 HSE,开启外部晶振,野火 STM32F103 系列开发板用的是 8M

9 RCC_HSEConfig(RCC_HSE_ON);

10

11 // 等待 HSE 启动稳定

12 HSEStartUpStatus = RCC_WaitForHSEStartUp();

13

14 // 只有 HSE 稳定之后则继续往下执行

15 if (HSEStartUpStatus == SUCCESS) {

16 //-----------------------------------------------------------------//

17 // 这两句是操作 FLASH 闪存用到的,如果不操作 FLASH,这两个注释掉也没影响

18 // 使能 FLASH 预存取缓冲区

19 FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

20

21 // SYSCLK 周期与闪存访问时间的比例设置,这里统一设置成 2

22 // 设置成 2 的时候, SYSCLK 低于 48M 也可以工作,如果设置成 0 或者 1 的时候,

23 // 如果配置的 SYSCLK 超出了范围的话,则会进入硬件错误,程序就死了

24 // 0: 0 < SYSCLK <= 24M

25 // 1: 24< SYSCLK <= 48M

26 // 2: 48< SYSCLK <= 72M

27 FLASH_SetLatency(FLASH_Latency_2);

28 //-----------------------------------------------------------------//

29

30 // AHB 预分频因子设置为 1 分频, HCLK = SYSCLK

31 RCC_HCLKConfig(RCC_SYSCLK_Div1);

32

33 // APB2 预分频因子设置为 1 分频, PCLK2 = HCLK

34 RCC_PCLK2Config(RCC_HCLK_Div1);

35

36 // APB1 预分频因子设置为 2 分频, PCLK1 = HCLK/2

37 RCC_PCLK1Config(RCC_HCLK_Div2);

38

39 //-----------------设置各种频率主要就是在这里设置-------------------//

40 // 设置 PLL 时钟来源为 HSE,设置 PLL 倍频因子

41 // PLLCLK = 8MHz * pllmul

42 RCC_PLLConfig(RCC_PLLSource_HSE_Div1, pllmul);

43 //-------------------------------------------------------------//零死角玩转 STM32

—基于野火 F103[MINI]开发板

44 //论坛: www.firebbs.cn 138 / 682 淘宝: https://fire-stm32.taobao.com

45 // 开启 PLL

46 RCC_PLLCmd(ENABLE);

47

48 // 等待 PLL 稳定

49 while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET) {

50 }

51

52 // 当 PLL 稳定之后,把 PLL 时钟切换为系统时钟 SYSCLK

53 RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

54

55 // 读取时钟切换状态位,确保 PLLCLK 被选为系统时钟

56 while (RCC_GetSYSCLKSource() != 0x08) {

57 }

58 } else {

59 // 如果 HSE 开启失败,那么程序就会来到这里,用户可在这里添加出错的代码处理

60 // 当 HSE 开启失败或者故障的时候,单片机会自动把 HSI 设置为系统时钟,

61 // HSI 是内部的高速时钟, 8MHZ

62 while (1) {

63 }

64 }

65 }

代码步骤 :

1.开启HSE,并等待HSE稳定;

2.设置AHB、APB1、APB2的预分频因子;

3.设置PLL的时钟来源和倍频因子;

4.开启PLL,并等待PLL稳定;

5.把PLLCLK切换为系统时钟SYSCLK;

6.读取时钟切换状态位,确保PLLCLK被选为系统时钟。

STM32时钟树

问题1:为什么需要时钟?

答:STM 32的时钟系统类似于人的心脏,需要为芯片提供时钟芯片才能正常工作,而STM32有很多的外设,如果像51单片机那样所有外设共用一个时钟系统的话,那么有些外设用不到那么高的频率,这样便会造成更高的功耗。在同一个电路,时钟越高功耗越大,抗干扰能力也越低,因此STM32采用不同的时钟来为不同的外设提供不同的时钟频率。

时钟树相关知识基础:

STM32有5个时钟源,分别是:1、HSE:高速外部时钟 2、HSI:高速内部时钟 3、LSE:低速外部时钟 4、LSI:低速外部时钟 5、PLL锁相环输出。

其中HSE的来源为外接晶振,可以选择晶振频率范围为4~16MHZ,一般选择8MHZ。当使用无源晶振时,晶振接STM32的OSC_IN和OSC_OUT引脚,并在晶振两端分别接两个22pF的电容。电路如下图所示。

HSI的时钟来源为内部RC振荡器,频率为8MHZ,精度较低并且容易受温度影响。

LSE的时钟来源为外接晶振,频率为32.768KHZ,用于RTC时钟。电路如下图所示。

HSI的时钟来源为内部RC振荡器,频率为8MHZ,精度较低并且容易受温度影响。

LSE的时钟来源为外接晶振,频率为32.768KHZ,用于RTC时钟。电路如下图所示。

LSI的时钟来源为内部RC振荡器,频率为40kHZ ,常用于独立看门狗时钟。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。 倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。我们常用8M的外部晶振的9倍频,即72MHz作为系统时钟(SYSCLK)。

LSI的时钟来源为内部RC振荡器,频率为40kHZ ,常用于独立看门狗时钟。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。 倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。我们常用8M的外部晶振的9倍频,即72MHz作为系统时钟(SYSCLK)。

红框1中的OSC_OUT和OSC_IN接外部8M晶振(范围为4到16MHz)作为HSE(外部高速时钟),通过PLLXTPRE位可控制选择器②是输出HSE还是HSE/2,选择器①通过PLLSRC位控制,用来选择是HSI/2还是选择器②的输出作为倍频锁相环(PLLMUL控制倍频的倍数)的输入,我们一般都是(系统默认)配置为8Mhz的HSE作为倍频器的输入并选择9倍频产生72MHz的时钟PLLCLK作为系统时钟(SYSCLK),系统时钟经AHB预分频器(默认分频系数为1)得到HCLK,可作为部分外设的时钟,如SDIO,FSMC等,再经APB1,APB2预分频器可得到PCLK1、PCLK2。

PCLK1:APB1低速总线时钟,最高为36M。为APB1总线时钟的外设提供时钟。但又经过2倍频作为定时器2~7的时钟,所以定时器2到定时器7即使是在APB1下,也为72M的时钟。

PCLK2:APB2高速总线时钟,最高为72M。为APB2总线时钟的外设(包含定时器1和8)提供时钟。

PCLK2经ADC预分频器(/2,4,6,8)作为ADCCLK(最大为14M),我们常选择6分频(72/6=12M)

固件库配置时钟树步骤:(参考野火)

1.开启HSE,并等待HSE稳定;

2.设置AHB、APB1、APB2的预分频因子;

3.设置PLL的时钟来源和倍频因子;

4.开启PLL,并等待PLL稳定;

5.把PLLCLK切换为系统时钟SYSCLK;

6.读取时钟切换状态位,确保PLLCLK被选为系统时钟。

配置步骤参考下图中的1到7。

红框1中的OSC_OUT和OSC_IN接外部8M晶振(范围为4到16MHz)作为HSE(外部高速时钟),通过PLLXTPRE位可控制选择器②是输出HSE还是HSE/2,选择器①通过PLLSRC位控制,用来选择是HSI/2还是选择器②的输出作为倍频锁相环(PLLMUL控制倍频的倍数)的输入,我们一般都是(系统默认)配置为8Mhz的HSE作为倍频器的输入并选择9倍频产生72MHz的时钟PLLCLK作为系统时钟(SYSCLK),系统时钟经AHB预分频器(默认分频系数为1)得到HCLK,可作为部分外设的时钟,如SDIO,FSMC等,再经APB1,APB2预分频器可得到PCLK1、PCLK2。

PCLK1:APB1低速总线时钟,最高为36M。为APB1总线时钟的外设提供时钟。但又经过2倍频作为定时器2~7的时钟,所以定时器2到定时器7即使是在APB1下,也为72M的时钟。

PCLK2:APB2高速总线时钟,最高为72M。为APB2总线时钟的外设(包含定时器1和8)提供时钟。

PCLK2经ADC预分频器(/2,4,6,8)作为ADCCLK(最大为14M),我们常选择6分频(72/6=12M)

固件库配置时钟树步骤:(参考野火)

1.开启HSE,并等待HSE稳定;

2.设置AHB、APB1、APB2的预分频因子;

3.设置PLL的时钟来源和倍频因子;

4.开启PLL,并等待PLL稳定;

5.把PLLCLK切换为系统时钟SYSCLK;

6.读取时钟切换状态位,确保PLLCLK被选为系统时钟。

配置步骤参考下图中的1到7。

固件库配置时钟树参考代码

固件库配置时钟树参考代码

void HSE_SetSysClock(uint32_t pllmul)

2 {

3 __IO uint32_t StartUpCounter = 0, HSEStartUpStatus = 0;

4

5 // 把 RCC 外设初始化成复位状态

6 RCC_DeInit();

7

8 //使能 HSE,开启外部晶振,野火 STM32F103 系列开发板用的是 8M

9 RCC_HSEConfig(RCC_HSE_ON);

10

11 // 等待 HSE 启动稳定

12 HSEStartUpStatus = RCC_WaitForHSEStartUp();

13

14 // 只有 HSE 稳定之后则继续往下执行

15 if (HSEStartUpStatus == SUCCESS) {

16 //-----------------------------------------------------------------//

17 // 这两句是操作 FLASH 闪存用到的,如果不操作 FLASH,这两个注释掉也没影响

18 // 使能 FLASH 预存取缓冲区

19 FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

20

21 // SYSCLK 周期与闪存访问时间的比例设置,这里统一设置成 2

22 // 设置成 2 的时候, SYSCLK 低于 48M 也可以工作,如果设置成 0 或者 1 的时候,

23 // 如果配置的 SYSCLK 超出了范围的话,则会进入硬件错误,程序就死了

24 // 0: 0 < SYSCLK <= 24M

25 // 1: 24< SYSCLK <= 48M

26 // 2: 48< SYSCLK <= 72M

27 FLASH_SetLatency(FLASH_Latency_2);

28 //-----------------------------------------------------------------//

29

30 // AHB 预分频因子设置为 1 分频, HCLK = SYSCLK

31 RCC_HCLKConfig(RCC_SYSCLK_Div1);

32

33 // APB2 预分频因子设置为 1 分频, PCLK2 = HCLK

34 RCC_PCLK2Config(RCC_HCLK_Div1);

35

36 // APB1 预分频因子设置为 2 分频, PCLK1 = HCLK/2

37 RCC_PCLK1Config(RCC_HCLK_Div2);

38

39 //-----------------设置各种频率主要就是在这里设置-------------------//

40 // 设置 PLL 时钟来源为 HSE,设置 PLL 倍频因子

41 // PLLCLK = 8MHz * pllmul

42 RCC_PLLConfig(RCC_PLLSource_HSE_Div1, pllmul);

43 //-------------------------------------------------------------//零死角玩转 STM32

—基于野火 F103[MINI]开发板

44 //论坛: www.firebbs.cn 138 / 682 淘宝: https://fire-stm32.taobao.com

45 // 开启 PLL

46 RCC_PLLCmd(ENABLE);

47

48 // 等待 PLL 稳定

49 while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET) {

50 }

51

52 // 当 PLL 稳定之后,把 PLL 时钟切换为系统时钟 SYSCLK

53 RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

54

55 // 读取时钟切换状态位,确保 PLLCLK 被选为系统时钟

56 while (RCC_GetSYSCLKSource() != 0x08) {

57 }

58 } else {

59 // 如果 HSE 开启失败,那么程序就会来到这里,用户可在这里添加出错的代码处理

60 // 当 HSE 开启失败或者故障的时候,单片机会自动把 HSI 设置为系统时钟,

61 // HSI 是内部的高速时钟, 8MHZ

62 while (1) {

63 }

64 }

65 }

代码步骤 :

1.开启HSE,并等待HSE稳定;

2.设置AHB、APB1、APB2的预分频因子;

3.设置PLL的时钟来源和倍频因子;

4.开启PLL,并等待PLL稳定;

5.把PLLCLK切换为系统时钟SYSCLK;

6.读取时钟切换状态位,确保PLLCLK被选为系统时钟。

举报

举报

举报

举报