数据选择器与加法器

15号试验台

一、 实验目的

1、 熟悉中规模集成电路数据选择器的工作原理和逻辑功能。

2、 了解数据选择器的应用。

3、 掌握组合逻辑电路的设计方法,理解半加器和全加器的逻辑功能。

4、 掌握中规模集成电路加法器的工作原理及其逻辑功能。

二、 实验原理

① 数据选择器

数据选择器又称多路选择器,是一个数据开关,它从N路源数据中选择一路送至输出端。

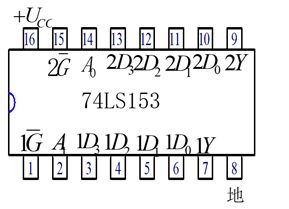

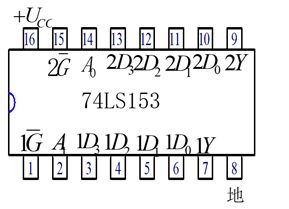

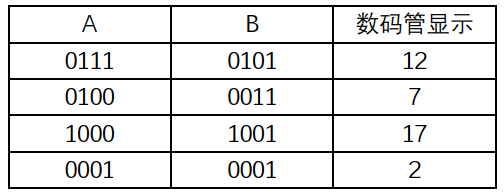

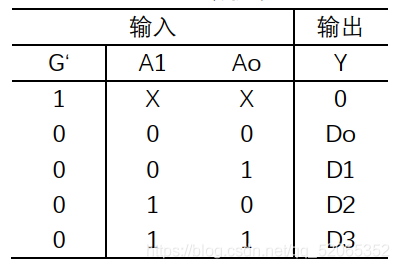

双4选1数据选择器74LS153

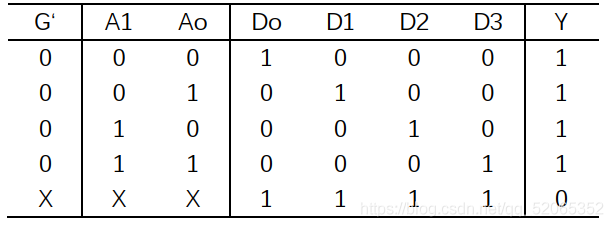

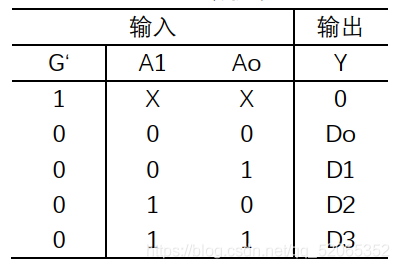

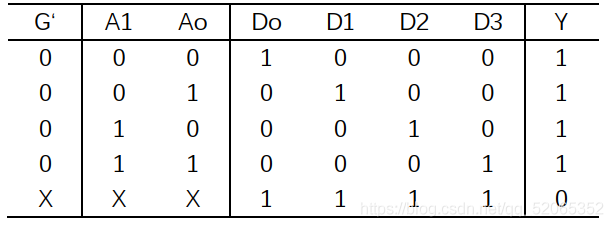

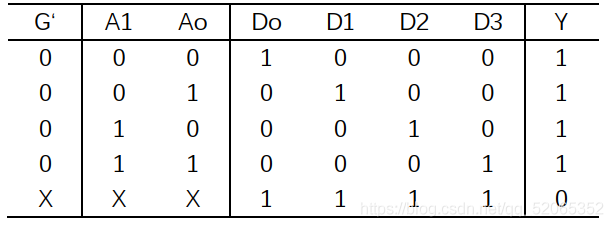

74LS153功能表:

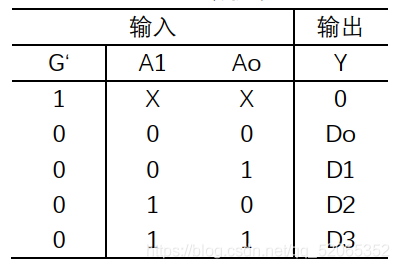

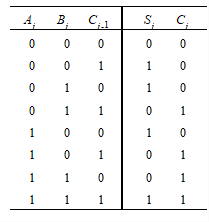

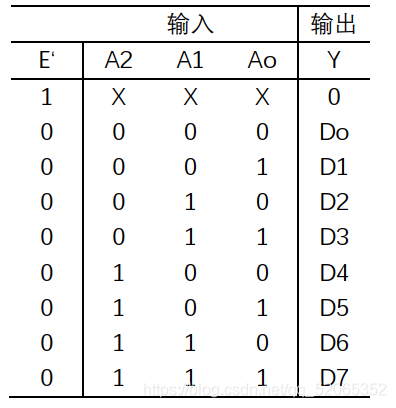

74151是八选一数据选择器,三个控制端A0、A1、A2,有8种组合,000、001、010、011、100、101、110、111。

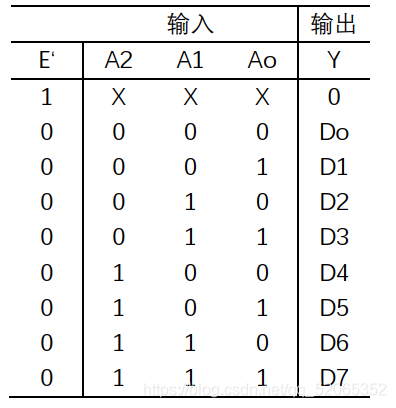

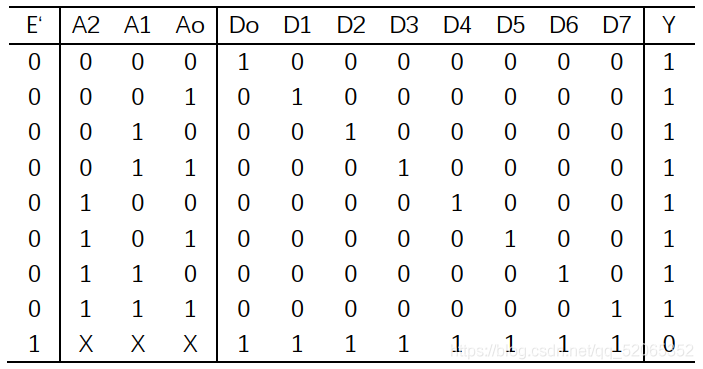

74LS151功能表

②加法器

在数字系统中,经常需要进行算术运算,逻辑操作及数字大小比较等操作,实现这些运算功能的电路是加法器。加法器是一种组合逻辑电路,主要功能是实现二进制数的算术加法运算。

I、半加器

● 半加器完成两个一位二进制数相加,若只考虑两个加数本身,而不考虑来自相邻低位的进位,称为半加,实现半加运算功能的电路称为半加器。

●由真值表可得出半加器的逻辑表达式:

II、全加器

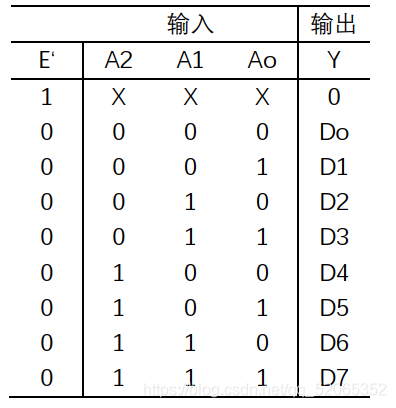

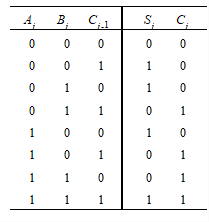

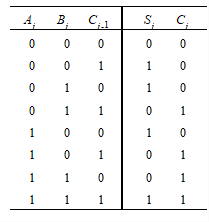

全加器真值表

●两个多位数相加是每一位都是带进位相加,所以必须用全加器。这时只要依次将低位的进位输出接到高位的输入,就可构成多位加法器了。

●全加器是一种由被加数、加数和来自低位的进位数三者相加的运算器。基本功能是实现二进制加法。

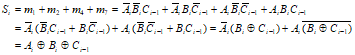

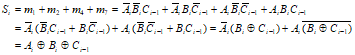

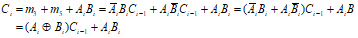

●逻辑表达式:

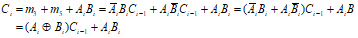

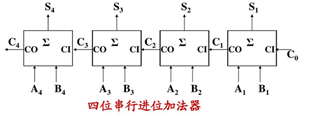

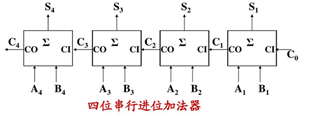

III、串行进位加法器(结构简单、运算速度慢)

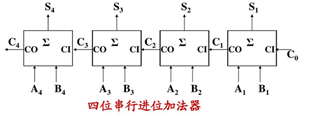

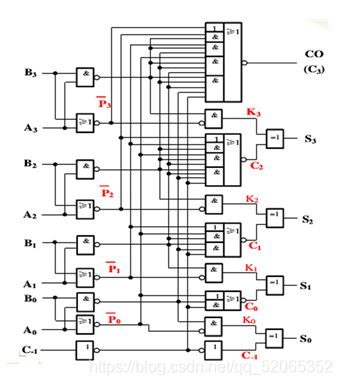

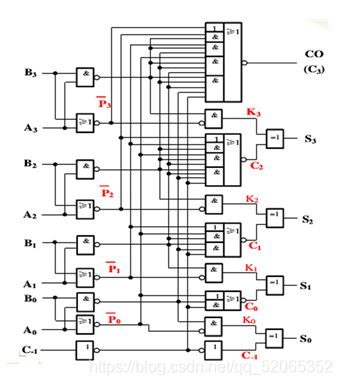

IV、并行加法器

●进位链

把n个加法器单元电路按一定方式互联起来,即构成n位的 并行加法器。其由两部分组成:

一 并行成分,指两个操作数的 所有位同时并行加入加法器运算;

二 链结构。

虽然操作数各位同时加入加法器进行运算,但并非所有位 佑数都同时产生,它存在进位的产生与传送问题,进位的产生与传送称为进位链,它的结构是影响加法器速度的关键。

●先行进位

先行进位也称并行进位,指加法器各位的进位是各自独立 且同时产生的,高一位的进位不依赖低位的进位产生与传送。

并行加法器任何一位的进位:

它可以分为两个部分,前者仅与这一位的两个操作数有关与低位的进位无关称它为本地进 位或进位生成,函数,记Gi; 后者不仅与操作数有关还与低位的进位有关称它为传递进位, 称Ai+Bi为传递函数Pi。因此可以写成:

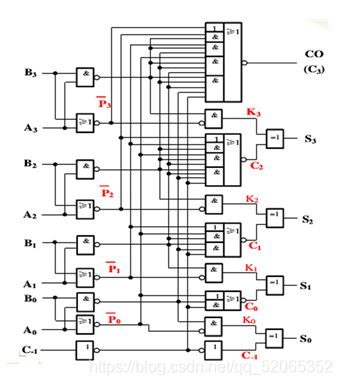

V、超前进位并行加法器

●超前进位电路构成的快速进位的4位全加器电路74LS283,可实现两个四位二进制的全加。

●加进位输入C0和进位输出C3主要用来扩大加法器字长,作为组间行波进位之用。由于它采用超前进位方式,所以进位传送速度快。

74LS283集成芯片引脚图

三、 实验内容

①数据选择器

1) 验证4选1数据选择器74LS153的逻辑功能并记录真值表。

根据74LS153芯片引脚图连接电路,记录所得数据,和理论真值表很好的符合。

74LS153真值表记录如下:

验证8选1数据选择器74LS151的逻辑功能并记录真值表。

根据74LS151的原理图连接电路,记录真值表,与理论对比,很好的符合。

74LS151真值表记录如下:

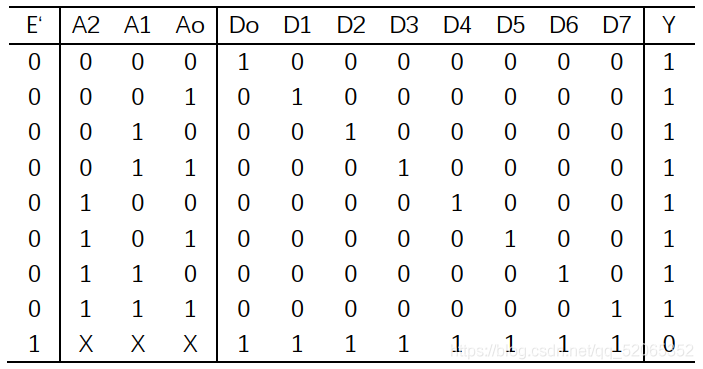

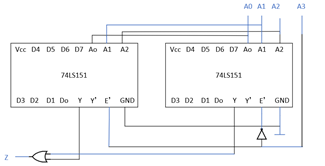

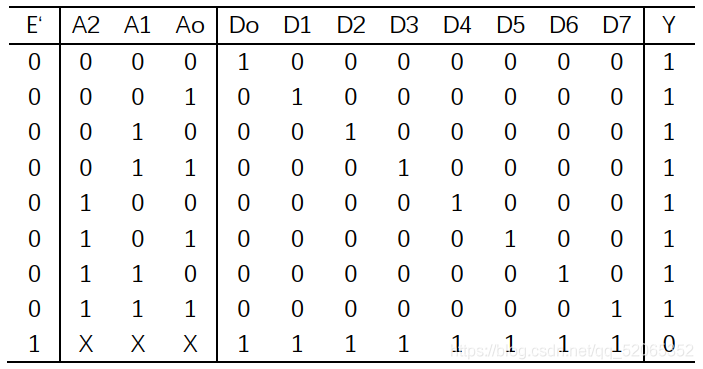

4)用两个8选1数据选择器74LS151扩展成16选1数据选择器,实现逻辑函数

∑m(6,7,8,11,13)。

首先,将两片151的三个输入端Ao、A1、A2连接在一起引出,作为16选1的四个输入端的其中三个。再将其中一个151的E‘与另一片E’经过一个反相器之后连接引出,作为16选1四个输入端剩下的那个A3。再将两个芯片的输出经过一个或门引出为Y。此时,十六选一数据选择器搭建完成。实验中为验证逻辑函数∑m(6,7,8,11,13),将对应的两芯片对应引脚连接输入。输出Y接小红灯。验证输入A0、A1、A2、A3,记录如下表:

扩展电路图:

②加法器

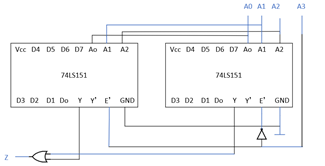

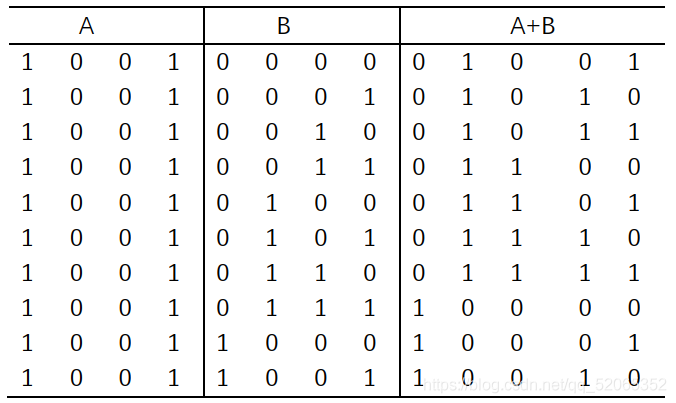

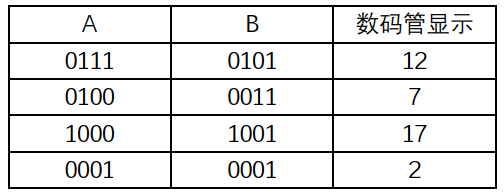

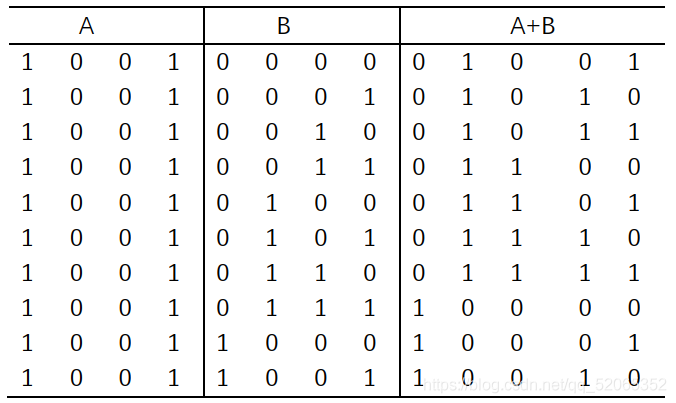

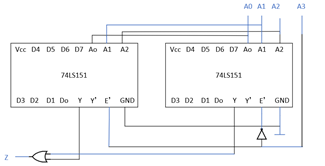

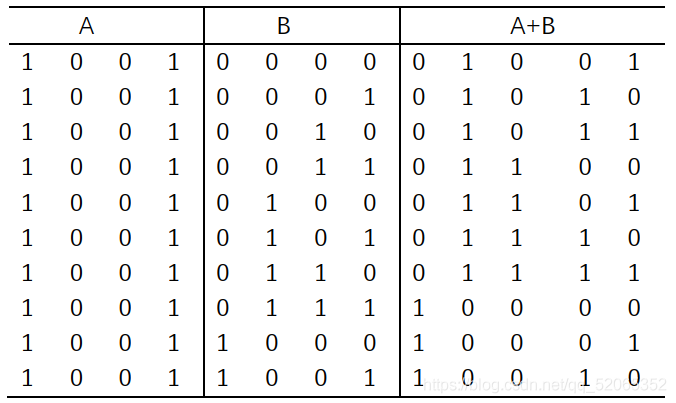

1) 用一片74LS283实现并行四位全加,将A置为1001,B置为0000~1001。

要求A置为1001,将其中两个引脚接+5V,另外两个接地。B输入接四个开关,依次验证B置为0000~1001的情况,记录。

记录结果如下:

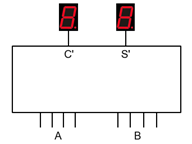

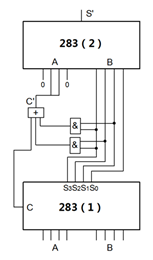

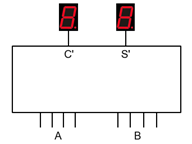

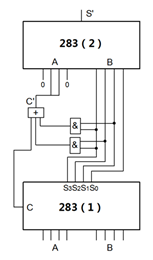

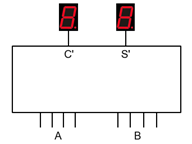

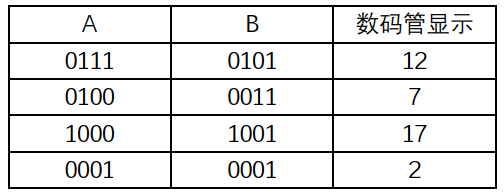

2) 用两片74LS283和必要的门电路实现两个8421BCD码求和运算,结果仍为8421BCD码。

输出:S’(个位:S3S2S1S0) C’(十位)

输出范围: 00~18 (S’:四位 C’ : 一位)

输入:A(A3A2A1A0)+ B(B3B2B1B0)

输入范围: A : 0~9 B : 0~9

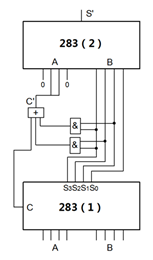

I、先用第一片283(1)实现A+B的全加,得到S。

II、题目要求个位S’和S的关系为:

S’=S(S《10);S’=S-1010 (S≥10)

S’=S(S《10);S’=S+0110(S≥10)

S’=S+0000(S《10);S’=S+0110(S≥10)

III、用第二片283将S进行修正,得到个位S’

第二片283的A:0000或0110

IV、第二片283的A3和A0直接接地,把A2和A1的

值标为C’

C’=0(S《10);C’=1(s≥10)

V、C’=S3·S2+S3·S1+C

实验记录:

四、思考题

●用两片 74LS283 和必要的门电路实现一个带借位输入和借位输出的 8421BCD 码减法器,要求电路输出为原码。

283原本是四位全加器,这里用于做减法器,很自然想到用反码代替被减数做加法运算。

A四位输入,B四位输入。做A-B。Ci为借位输入,即低位向A借位,由于是二进制运算,所以借位只会为0或1。Co为借位输出,即A-B向高位借位,也为0或1。283本身有一个进位输入,将其取反引出作为Ci输入,无借位输入时,B反码加1,有借位输入时B反码不加。B取反码输入,连接283前先通过反相器。第一片283进位输出取反为Co。若A《B,Co

为1,此时第一片输出结果为补码,需要用第二片283取补码。具体逻辑电路图如下:

第一片283输出,与Co做异或,因为若没有进位输出,说明减法结果为正数,不需要求补码。若结果为负数,此时Co为1,则第一片283输出取反输入第二片283,同时Co作为第二片Ci,因为取反加一为补码,第二片输出结果为A-B的差值绝对值。

五、实验总结与反思

I、使用门电路实现半加器与全加器时,首先列出半加器真值表或全加器真值表,然后由真值表得到逻辑表达式,再通过化简,画出逻辑电路图。

II、使用四位二进制全加器74LS283设计代码转换电路时,由于具有加法器功能,所以很方便进行转换。比如8421转换为余3码,余3码与8421码相差3,所以加三就可以得到余3码。相差部分,只要用283进行加法。

III、15号桌74LS04芯片1号引脚与2号引脚之间的非门已损坏,导致实验过程中耽误较长时间才检查出来。以后实验连线之后,若结果与理论不符,应使用逻辑笔反向检验,以尽快找到问题。发现芯片问题应在接下来实验内容中额外注意避开使用。

数据选择器与加法器

15号试验台

一、 实验目的

1、 熟悉中规模集成电路数据选择器的工作原理和逻辑功能。

2、 了解数据选择器的应用。

3、 掌握组合逻辑电路的设计方法,理解半加器和全加器的逻辑功能。

4、 掌握中规模集成电路加法器的工作原理及其逻辑功能。

二、 实验原理

① 数据选择器

数据选择器又称多路选择器,是一个数据开关,它从N路源数据中选择一路送至输出端。

双4选1数据选择器74LS153

74LS153功能表:

74151是八选一数据选择器,三个控制端A0、A1、A2,有8种组合,000、001、010、011、100、101、110、111。

74LS151功能表

②加法器

在数字系统中,经常需要进行算术运算,逻辑操作及数字大小比较等操作,实现这些运算功能的电路是加法器。加法器是一种组合逻辑电路,主要功能是实现二进制数的算术加法运算。

I、半加器

● 半加器完成两个一位二进制数相加,若只考虑两个加数本身,而不考虑来自相邻低位的进位,称为半加,实现半加运算功能的电路称为半加器。

●由真值表可得出半加器的逻辑表达式:

II、全加器

全加器真值表

●两个多位数相加是每一位都是带进位相加,所以必须用全加器。这时只要依次将低位的进位输出接到高位的输入,就可构成多位加法器了。

●全加器是一种由被加数、加数和来自低位的进位数三者相加的运算器。基本功能是实现二进制加法。

●逻辑表达式:

III、串行进位加法器(结构简单、运算速度慢)

IV、并行加法器

●进位链

把n个加法器单元电路按一定方式互联起来,即构成n位的 并行加法器。其由两部分组成:

一 并行成分,指两个操作数的 所有位同时并行加入加法器运算;

二 链结构。

虽然操作数各位同时加入加法器进行运算,但并非所有位 佑数都同时产生,它存在进位的产生与传送问题,进位的产生与传送称为进位链,它的结构是影响加法器速度的关键。

●先行进位

先行进位也称并行进位,指加法器各位的进位是各自独立 且同时产生的,高一位的进位不依赖低位的进位产生与传送。

并行加法器任何一位的进位:

它可以分为两个部分,前者仅与这一位的两个操作数有关与低位的进位无关称它为本地进 位或进位生成,函数,记Gi; 后者不仅与操作数有关还与低位的进位有关称它为传递进位, 称Ai+Bi为传递函数Pi。因此可以写成:

V、超前进位并行加法器

●超前进位电路构成的快速进位的4位全加器电路74LS283,可实现两个四位二进制的全加。

●加进位输入C0和进位输出C3主要用来扩大加法器字长,作为组间行波进位之用。由于它采用超前进位方式,所以进位传送速度快。

74LS283集成芯片引脚图

三、 实验内容

①数据选择器

1) 验证4选1数据选择器74LS153的逻辑功能并记录真值表。

根据74LS153芯片引脚图连接电路,记录所得数据,和理论真值表很好的符合。

74LS153真值表记录如下:

验证8选1数据选择器74LS151的逻辑功能并记录真值表。

根据74LS151的原理图连接电路,记录真值表,与理论对比,很好的符合。

74LS151真值表记录如下:

4)用两个8选1数据选择器74LS151扩展成16选1数据选择器,实现逻辑函数

∑m(6,7,8,11,13)。

首先,将两片151的三个输入端Ao、A1、A2连接在一起引出,作为16选1的四个输入端的其中三个。再将其中一个151的E‘与另一片E’经过一个反相器之后连接引出,作为16选1四个输入端剩下的那个A3。再将两个芯片的输出经过一个或门引出为Y。此时,十六选一数据选择器搭建完成。实验中为验证逻辑函数∑m(6,7,8,11,13),将对应的两芯片对应引脚连接输入。输出Y接小红灯。验证输入A0、A1、A2、A3,记录如下表:

扩展电路图:

②加法器

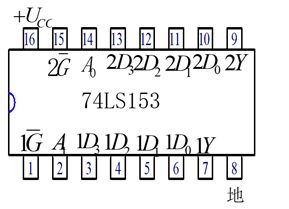

1) 用一片74LS283实现并行四位全加,将A置为1001,B置为0000~1001。

要求A置为1001,将其中两个引脚接+5V,另外两个接地。B输入接四个开关,依次验证B置为0000~1001的情况,记录。

记录结果如下:

2) 用两片74LS283和必要的门电路实现两个8421BCD码求和运算,结果仍为8421BCD码。

输出:S’(个位:S3S2S1S0) C’(十位)

输出范围: 00~18 (S’:四位 C’ : 一位)

输入:A(A3A2A1A0)+ B(B3B2B1B0)

输入范围: A : 0~9 B : 0~9

I、先用第一片283(1)实现A+B的全加,得到S。

II、题目要求个位S’和S的关系为:

S’=S(S《10);S’=S-1010 (S≥10)

S’=S(S《10);S’=S+0110(S≥10)

S’=S+0000(S《10);S’=S+0110(S≥10)

III、用第二片283将S进行修正,得到个位S’

第二片283的A:0000或0110

IV、第二片283的A3和A0直接接地,把A2和A1的

值标为C’

C’=0(S《10);C’=1(s≥10)

V、C’=S3·S2+S3·S1+C

实验记录:

四、思考题

●用两片 74LS283 和必要的门电路实现一个带借位输入和借位输出的 8421BCD 码减法器,要求电路输出为原码。

283原本是四位全加器,这里用于做减法器,很自然想到用反码代替被减数做加法运算。

A四位输入,B四位输入。做A-B。Ci为借位输入,即低位向A借位,由于是二进制运算,所以借位只会为0或1。Co为借位输出,即A-B向高位借位,也为0或1。283本身有一个进位输入,将其取反引出作为Ci输入,无借位输入时,B反码加1,有借位输入时B反码不加。B取反码输入,连接283前先通过反相器。第一片283进位输出取反为Co。若A《B,Co

为1,此时第一片输出结果为补码,需要用第二片283取补码。具体逻辑电路图如下:

第一片283输出,与Co做异或,因为若没有进位输出,说明减法结果为正数,不需要求补码。若结果为负数,此时Co为1,则第一片283输出取反输入第二片283,同时Co作为第二片Ci,因为取反加一为补码,第二片输出结果为A-B的差值绝对值。

五、实验总结与反思

I、使用门电路实现半加器与全加器时,首先列出半加器真值表或全加器真值表,然后由真值表得到逻辑表达式,再通过化简,画出逻辑电路图。

II、使用四位二进制全加器74LS283设计代码转换电路时,由于具有加法器功能,所以很方便进行转换。比如8421转换为余3码,余3码与8421码相差3,所以加三就可以得到余3码。相差部分,只要用283进行加法。

III、15号桌74LS04芯片1号引脚与2号引脚之间的非门已损坏,导致实验过程中耽误较长时间才检查出来。以后实验连线之后,若结果与理论不符,应使用逻辑笔反向检验,以尽快找到问题。发现芯片问题应在接下来实验内容中额外注意避开使用。

举报

举报

举报

举报