区域1:我们称为SMI接口,用于配置外部PHY芯片。

区域2:是数据交换接口,也就是上面我们说的MII接口和RMII接口。

利用这些接口可以有多种不同的网络电路设计方案,这里我来总结下。

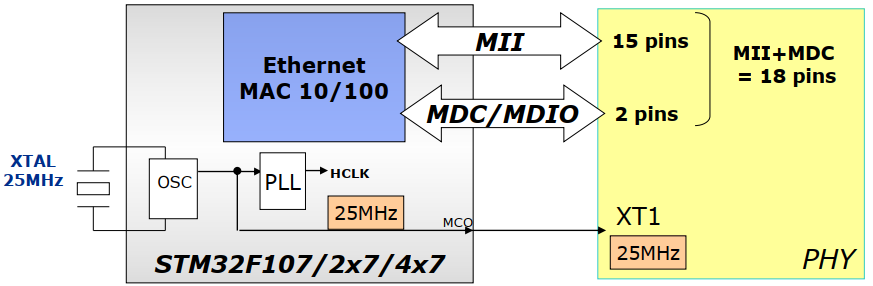

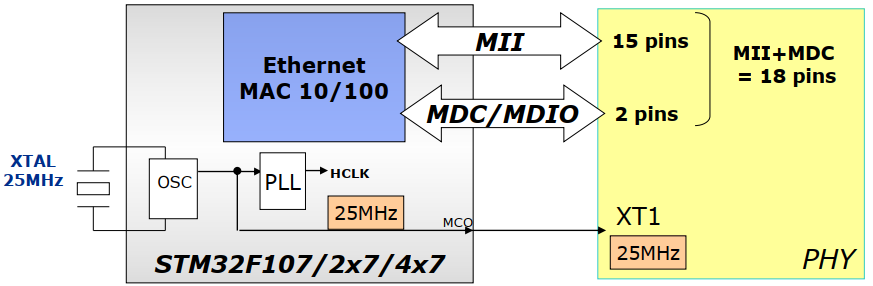

01、MII接口方案

MII接口在文章《STM32网络之MII和RMII》已经详细介绍过了,从中得知,需要一个25MHz的时钟。

对于MII接口,最常用的方案是,STM32外接25MHz的晶振。

内部的PLL配置HCLK,提供给内核和外设等。

外部PHY连接提供了25MHz的MCO脚。

此方案适合STM32F107/2x7/4x7。

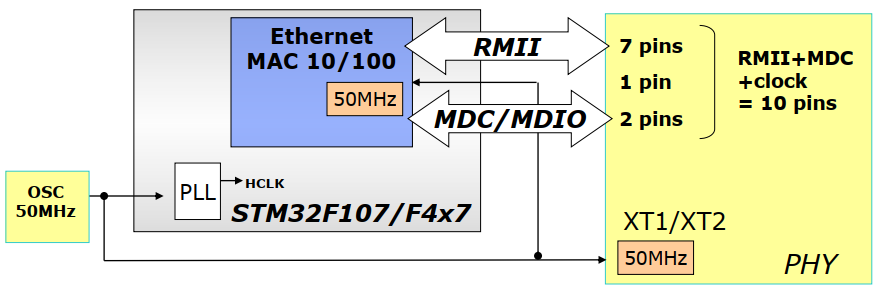

02、RMII接口方案

RMII接口在文章《STM32网络之MII和RMII》已经详细介绍过了,从中得知,需要一个50MHz的时钟。

2.1、外部晶振(2个晶振)

这个方案需要外接连里两个晶振。

外接25MHz晶振,内部的PLL配置HCLK,提供给内核和外设等。

外接50MHz晶振,输出50MHz时钟,提供给MAC控制器和外部PHY。

此方案适合STM32F107/2x7/4x7。

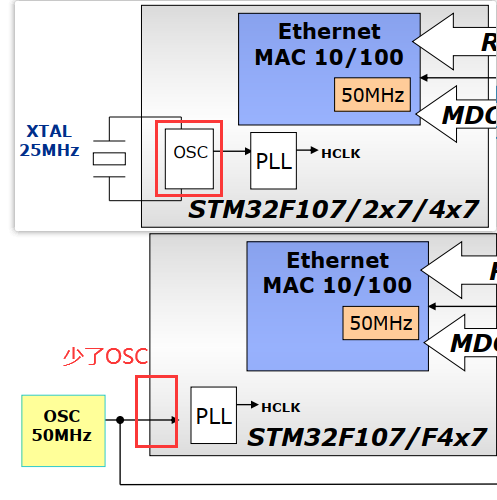

2.2、外部晶振(1个晶振)

这种方案外部只需要接1个50M晶振。一个晶振同时给STM32和外部PHY提供时钟,这样可以省成本。

重点:STM32F2X7不能使用这种方案,只适用于STM32F107/4x7。

大家注意上图的区别

这是因为,将HSE的OSC部分滤除掉,通过HSE的bypass,已经将50MHz的时钟通过OSCIN输入到PLL,再通过PLL产生提供内核和外设的时钟。

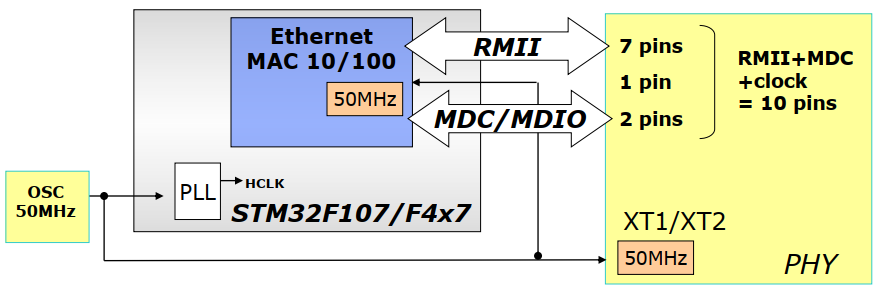

2.3、需要强力PHY

这个方案也使用一个25MHz的晶振,但是需要一个功能强大的PHY芯片,这颗PHY可以将输入的25MHz的时钟内部倍频到50MHz时钟,然后输出给STM32的MAC控制模块。

外接25MHz晶振,内部的PLL配置HCLK,提供给内核和外设等。

STM32通过MCO引脚提供25MHz时钟给外部PHY。

外部PHY内部生成50MHz的时钟提供给STM32的MAC控制模块。

此方案适合STM32F107/2x7/4x7。

个人不建议这种方案,不利于后期更换物料。

区域1:我们称为SMI接口,用于配置外部PHY芯片。

区域2:是数据交换接口,也就是上面我们说的MII接口和RMII接口。

利用这些接口可以有多种不同的网络电路设计方案,这里我来总结下。

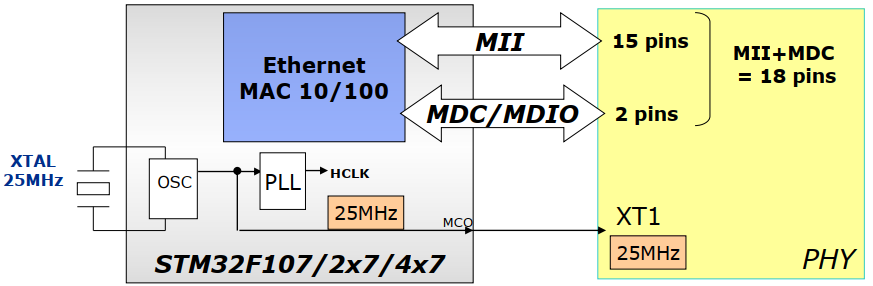

01、MII接口方案

MII接口在文章《STM32网络之MII和RMII》已经详细介绍过了,从中得知,需要一个25MHz的时钟。

对于MII接口,最常用的方案是,STM32外接25MHz的晶振。

内部的PLL配置HCLK,提供给内核和外设等。

外部PHY连接提供了25MHz的MCO脚。

此方案适合STM32F107/2x7/4x7。

02、RMII接口方案

RMII接口在文章《STM32网络之MII和RMII》已经详细介绍过了,从中得知,需要一个50MHz的时钟。

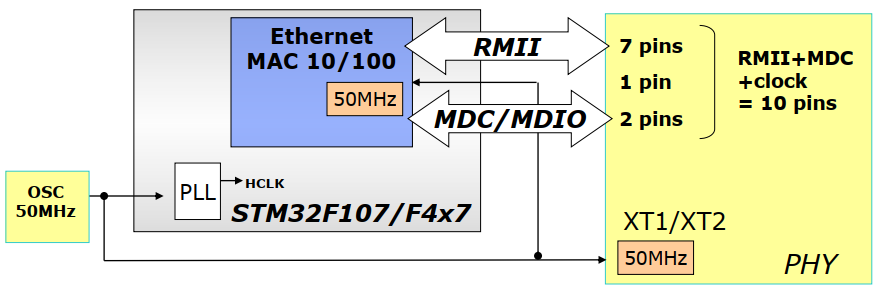

2.1、外部晶振(2个晶振)

这个方案需要外接连里两个晶振。

外接25MHz晶振,内部的PLL配置HCLK,提供给内核和外设等。

外接50MHz晶振,输出50MHz时钟,提供给MAC控制器和外部PHY。

此方案适合STM32F107/2x7/4x7。

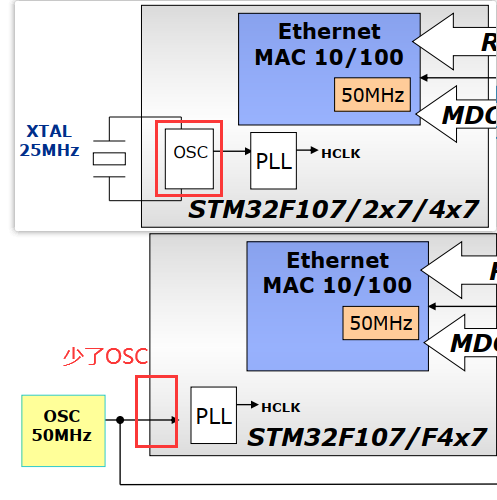

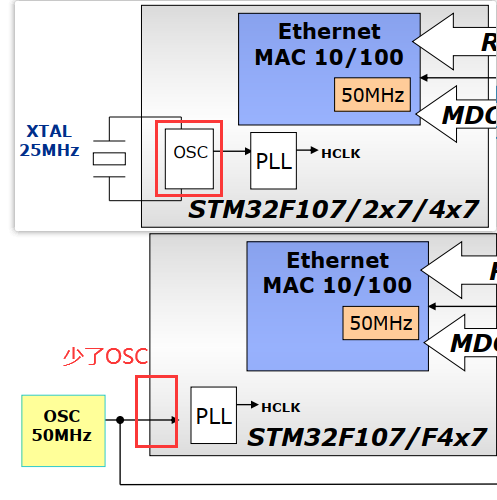

2.2、外部晶振(1个晶振)

这种方案外部只需要接1个50M晶振。一个晶振同时给STM32和外部PHY提供时钟,这样可以省成本。

重点:STM32F2X7不能使用这种方案,只适用于STM32F107/4x7。

大家注意上图的区别

这是因为,将HSE的OSC部分滤除掉,通过HSE的bypass,已经将50MHz的时钟通过OSCIN输入到PLL,再通过PLL产生提供内核和外设的时钟。

2.3、需要强力PHY

这个方案也使用一个25MHz的晶振,但是需要一个功能强大的PHY芯片,这颗PHY可以将输入的25MHz的时钟内部倍频到50MHz时钟,然后输出给STM32的MAC控制模块。

外接25MHz晶振,内部的PLL配置HCLK,提供给内核和外设等。

STM32通过MCO引脚提供25MHz时钟给外部PHY。

外部PHY内部生成50MHz的时钟提供给STM32的MAC控制模块。

此方案适合STM32F107/2x7/4x7。

个人不建议这种方案,不利于后期更换物料。

举报

举报

举报

举报