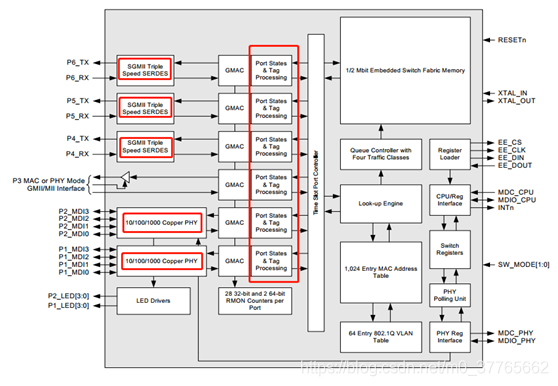

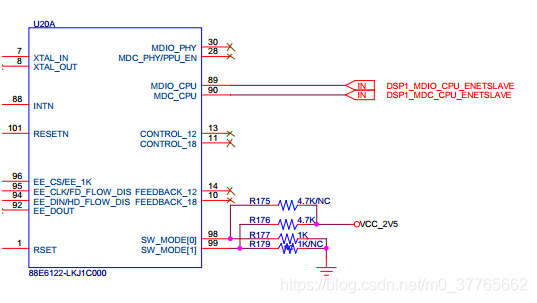

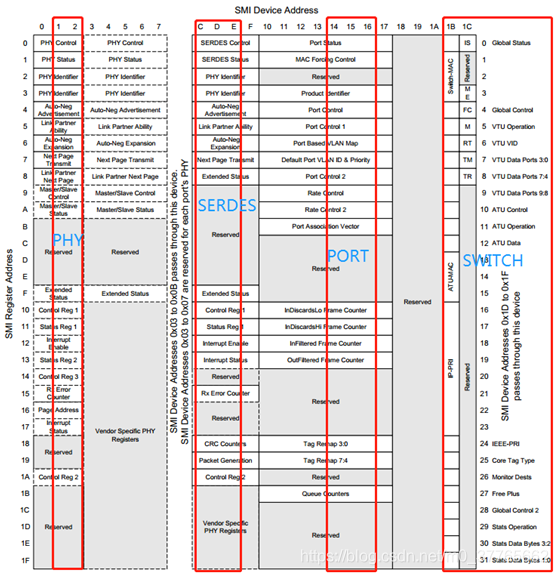

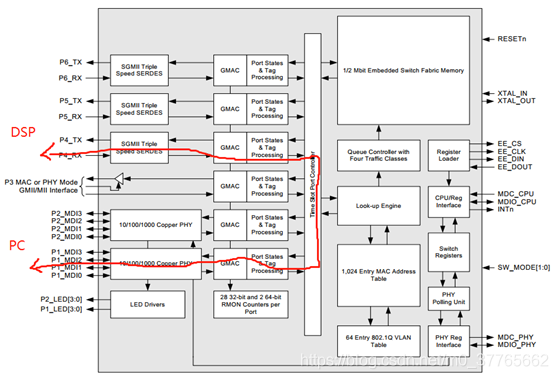

| Switch全局配置 |

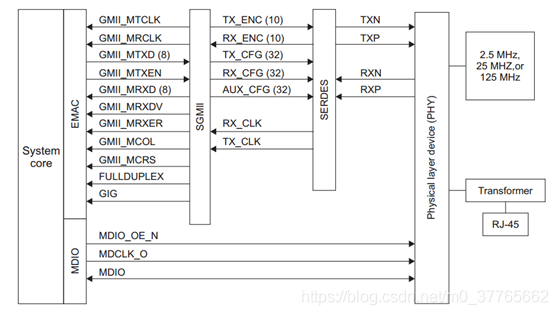

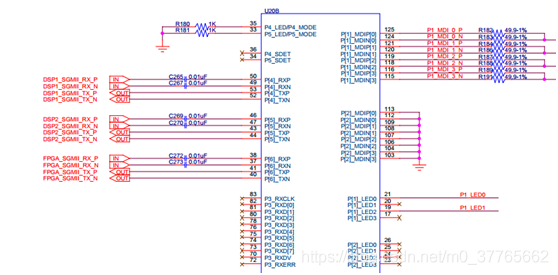

| SERDES配置 |

| PORT配置 |

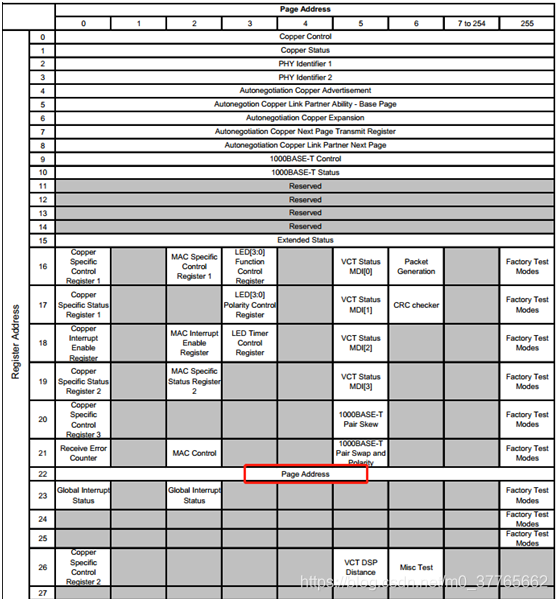

| PHY配置 |

| PART | SMI地址 |

| PHY 1-PHY 2 | 0x1--0x2 |

| SERDES 1-- SERDES 3 | 0xC--0xE |

| PORT 1 -- PORT 6 | 0x11 -- 0x16 |

| GLOBAL | 0x1B |

| Register | value | Description |

| PHY Copper Status | 0x796D | Link is up condition not detected Auto-Negotiation process complete |

| SERDES Status Register-Fiber | 0x14D | link is up PHY able to perform Auto-Negotiation Auto-Negotiation process not complete |

| Port Status Register | 0xE86 | Disabled(Port 3) or AutoNeg PHY Port(duplex and speed determined by the PPU) 1000Mbps Full-Duplex Link is up |

| Switch Global Status Register | 0xA800 | Switch Ready Switch Mode is 10 PPU Disabled after Initialization |

举报

举报

更多回帖