第九章 不同抽象级别的Verilog HDL模型

Verilog模型可以是实际电路不同级别的抽象。这些抽象的级别和它们对应的模型类型共有以下五种:

1) 系统级(system)

2) 算法级(algorithmic)

3) RTL级(RegisterTransferLevel):

4) 门级(gate-level):

5) 开关级(switch-level)

一个复杂电路的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。这些模块可以分别用不同抽象级别的Verilog HDL描述,在一个模块中也可以有多种级别的描述。利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计。

门级结构描述

and 与门

nand 与非门

nor 或非门

or 或门

xor 异或门

xnor 异或非门

buf 缓冲器

not 非门

nand #10 nd1(a,data,clock,clear);

表示在模块中引用了一个名为nd1的与非门(nand),输入为data、clock和clear,输出为a,输出与输入的延时为10个单位时间。

1.如何用Verilog HDL语言描述D型主从触发器模块?

门级结构描述D触发器

当在其他模块中引用这个模块时,有两种方法(顺序法、端口名对应法):

顺序法1) flop flop_d( d1, clk, clrb, q, qn);

端口名2) flop flop_d (.clock(clk),.q(q),.clear(clrb),.qb(qn),.data(d1));

它们都表示实例f1op_d 引用已编模块 flop。只是如果采取顺序法,实例的端口信号必须按照被引用模块的端口信号传入;采用端口名法,实例的端口信号和被引用模块的端口信号必需一一列出。

2.如何引用上面的模块flop,构成一个四位寄存器?

由已经设计成的模块来构成更高一层的模块

3.如何对于上面的四位寄存器进行验证?

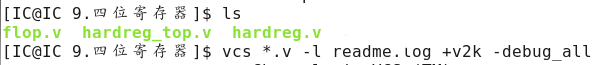

4.既然有了所有的代码,就进入linux开始VCS编译仿真

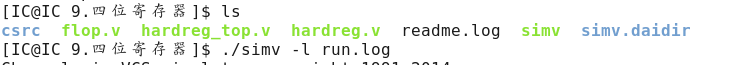

编译

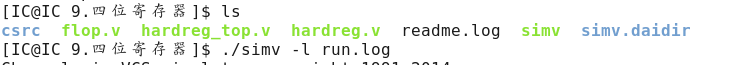

运行上面的命令,产生的效果如下(多了四个文件):

仿真

运行上面的命令,产生的效果如下(是不是多了两个文件):

运行。/simv -gui打开DVE图形化界面

好吧,我暂且认为是自己的testbench中没有加$vcdpluson()造成的。

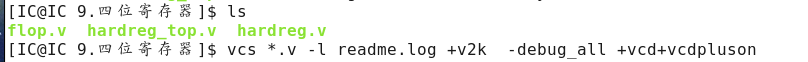

5.重新盘一下第四步为什么没有波形文件

1、编译

要想有波形文件,必须在testbench中加入$vcdpluson类似的的语句,最简单的格式如下:

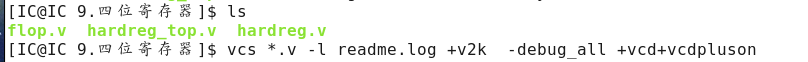

initial begin $vcdpluson;end 编译的时候,必须加上“+vcd+vcdpluson”开关,在仿真时才能产生波形文件,使用如下命令编译:

vcs *.v -l readme.log +v2k -debug_all +vcd+vcdpluson vcs *.v 就是编译的主要命令

-l readme.log 就是把编译过程记录在文件readme.log中,以备后面查看

+v2k 好像是遵守verilog 2005 标准编译吧

-debug_all 就是打开所有的debug开关,还有-debug_pp、-debug

+vcd+vcdpluson 在仿真时才能产生波形文件

2.仿真

命令如下:

。/simv -l run.log 。/simv 就可以生成波形文件vcdpluson.vpd

-l run.log 把仿真的过程记录在文件run.log中,以备后面查看

3.看波形

dve –vpd vcdpluson.vpd 结果又报错了,尽管打开了dve,但是打不开波形文件

修改文件名,继续!结果不知道为什么是这样!就这样吧

写在最后

我现在真的不知道该怎么学习验证了。昨天问学长,他怎么学的verilog,他说就简单看了一下verilog语法,也没练习。我该怎么做呀!有点难搞,炸裂,裂开。

第九章 不同抽象级别的Verilog HDL模型

Verilog模型可以是实际电路不同级别的抽象。这些抽象的级别和它们对应的模型类型共有以下五种:

1) 系统级(system)

2) 算法级(algorithmic)

3) RTL级(RegisterTransferLevel):

4) 门级(gate-level):

5) 开关级(switch-level)

一个复杂电路的完整Verilog HDL模型是由若干个Verilog HDL模块构成的,每一个模块又可以由若干个子模块构成。这些模块可以分别用不同抽象级别的Verilog HDL描述,在一个模块中也可以有多种级别的描述。利用Verilog HDL语言结构所提供的这种功能就可以构造一个模块间的清晰层次结构来描述极其复杂的大型设计。

门级结构描述

and 与门

nand 与非门

nor 或非门

or 或门

xor 异或门

xnor 异或非门

buf 缓冲器

not 非门

nand #10 nd1(a,data,clock,clear);

表示在模块中引用了一个名为nd1的与非门(nand),输入为data、clock和clear,输出为a,输出与输入的延时为10个单位时间。

1.如何用Verilog HDL语言描述D型主从触发器模块?

门级结构描述D触发器

当在其他模块中引用这个模块时,有两种方法(顺序法、端口名对应法):

顺序法1) flop flop_d( d1, clk, clrb, q, qn);

端口名2) flop flop_d (.clock(clk),.q(q),.clear(clrb),.qb(qn),.data(d1));

它们都表示实例f1op_d 引用已编模块 flop。只是如果采取顺序法,实例的端口信号必须按照被引用模块的端口信号传入;采用端口名法,实例的端口信号和被引用模块的端口信号必需一一列出。

2.如何引用上面的模块flop,构成一个四位寄存器?

由已经设计成的模块来构成更高一层的模块

3.如何对于上面的四位寄存器进行验证?

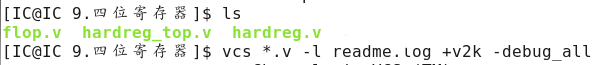

4.既然有了所有的代码,就进入linux开始VCS编译仿真

编译

运行上面的命令,产生的效果如下(多了四个文件):

仿真

运行上面的命令,产生的效果如下(是不是多了两个文件):

运行。/simv -gui打开DVE图形化界面

好吧,我暂且认为是自己的testbench中没有加$vcdpluson()造成的。

5.重新盘一下第四步为什么没有波形文件

1、编译

要想有波形文件,必须在testbench中加入$vcdpluson类似的的语句,最简单的格式如下:

initial begin $vcdpluson;end 编译的时候,必须加上“+vcd+vcdpluson”开关,在仿真时才能产生波形文件,使用如下命令编译:

vcs *.v -l readme.log +v2k -debug_all +vcd+vcdpluson vcs *.v 就是编译的主要命令

-l readme.log 就是把编译过程记录在文件readme.log中,以备后面查看

+v2k 好像是遵守verilog 2005 标准编译吧

-debug_all 就是打开所有的debug开关,还有-debug_pp、-debug

+vcd+vcdpluson 在仿真时才能产生波形文件

2.仿真

命令如下:

。/simv -l run.log 。/simv 就可以生成波形文件vcdpluson.vpd

-l run.log 把仿真的过程记录在文件run.log中,以备后面查看

3.看波形

dve –vpd vcdpluson.vpd 结果又报错了,尽管打开了dve,但是打不开波形文件

修改文件名,继续!结果不知道为什么是这样!就这样吧

写在最后

我现在真的不知道该怎么学习验证了。昨天问学长,他怎么学的verilog,他说就简单看了一下verilog语法,也没练习。我该怎么做呀!有点难搞,炸裂,裂开。

举报

举报

举报

举报