输入电压范围(Input Voltage Range)

定义:

保证运算放大器正常工作的最大输入电压范围。也称为共模输入电压范围。

优劣评定:

一般运放的输入电压范围比电源电压范围窄 1V 到几 V,比如± 15V 供电,输入电压范围在-12V~13V。较好的运放输入电压范围和电源电压范围相同,甚至超出范围 0.1V。比如±15V 供电,输入范围在-15.1V 到 15.0V,这会使得放大器设计具有更大的输入动态范围,提高电路的适应性。

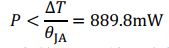

当运放最大输入电压范围与电源范围比较接近时,比如相差 0.1V 甚至相等、超过,都可以叫“输入轨至轨”,表示为 Rail-to-rail input,或 RRI。

理解:

运放的两个输入端,任何一个的输入电压超过此范围,都将引起运放的失效。注意,超出此范围并不代表运放会被烧毁,但绝对参数中出现的此值是坚决不能超过的。

之所以叫共模输入电压范围,是因为运放正常工作时,两个输入端之间的差压是很小的,某个输入端的电压与两个输入端电压的平均值(共模)是基本相同的(负反馈得结果,虚短)

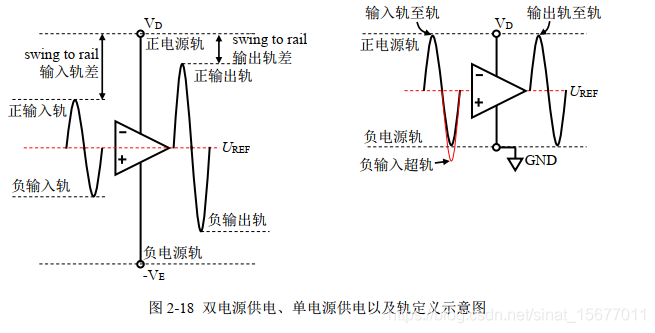

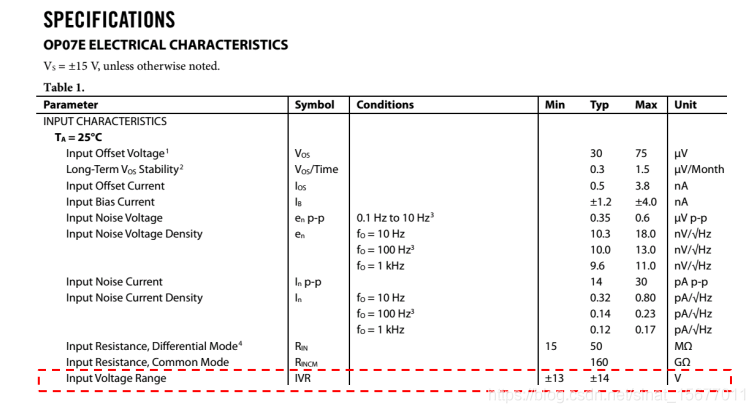

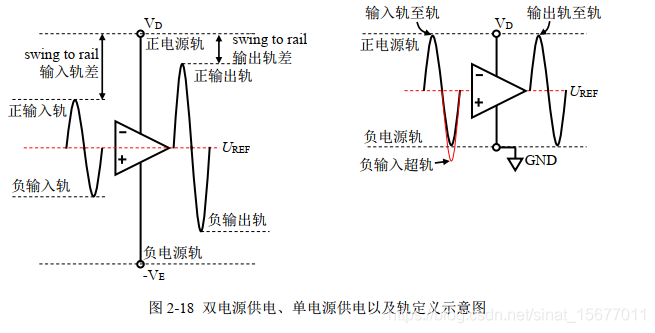

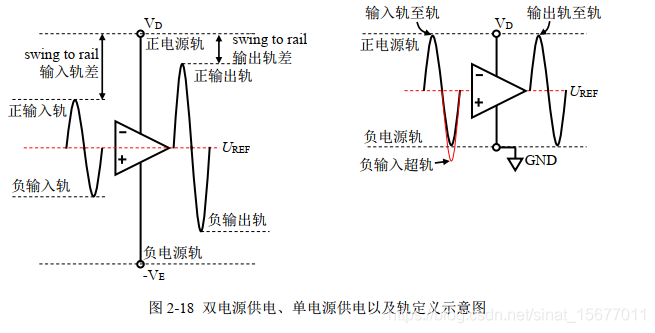

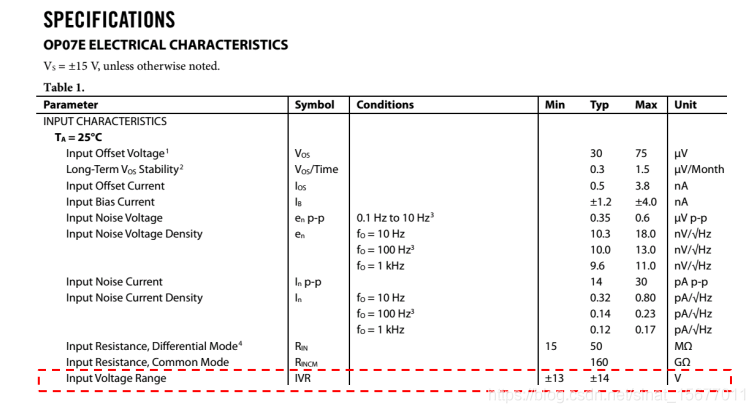

图 2-18 给出了输入电压范围和输出电压范围的示意。下方的 OP07 数据手册中,可以看出它的供电电压范围在±15V 时,其输入电压范围只有±14V。

输出电压范围(VOH/VOL 或者 Swing from rail)

定义:

在给定电源电压和负载情况下,输出能够达到的最大电压范围。或者给出正向最大电压 VOH 以及负向最小电压 VOL——相对于给定的电源电压和负载;或者给出与电源轨(rail)的差距。

优劣范围:

一般运放的输出电压范围要比电源电压范围略窄 1V 到几 V。较好的运放输出电压范围可以与电源电压范围非常接近,比如几十 mV 的差异,这被称为“输出至轨电压”。这在低电压供电场合非常有用。当厂家觉得这个运放的输出范围已经接近于电源电压范围时,就自称“输出轨至轨”,表示为 Rail-to-rail output,或 RRO。

理解:

在没有额外的储能元件情况下,运放的输出电压不可能超过电源电压范围,随着负载的加重,输出最大值与电源电压的差异会越大。这需要看数据手册中的附图。

输出电压范围,或者输出至轨电压有如下特点:

1) 正至轨电压与负至轨电压的绝对值可能不一致,但一般情况下数量级相同;

2) 至轨电压与负载密切相关,负载越重(阻抗小) 至轨电压越大;(负载电阻越小,负载电流越大,输出电阻上产生得压降越大,所以输出电压,也就是负载两端得电压越小)。

3) 至轨电压与信号频率相关,频率越高,至轨电压越大,甚至会突然大幅度下降;

4) 至轨电压在 20mV 以内,属于非常优秀。

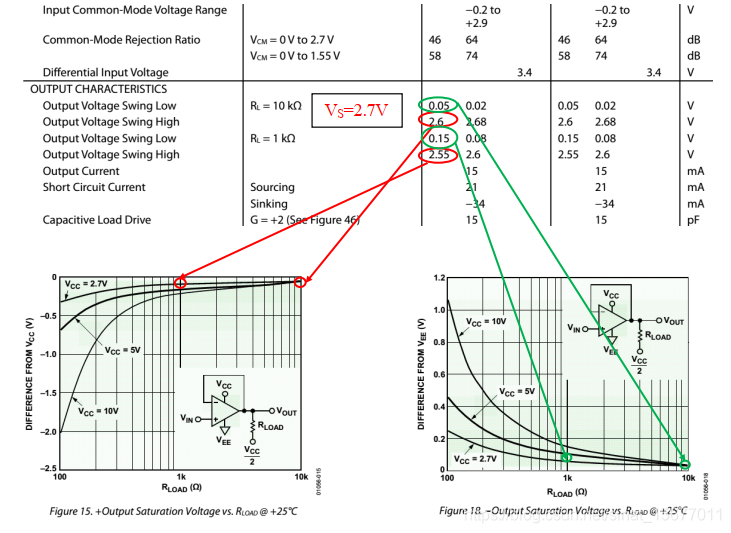

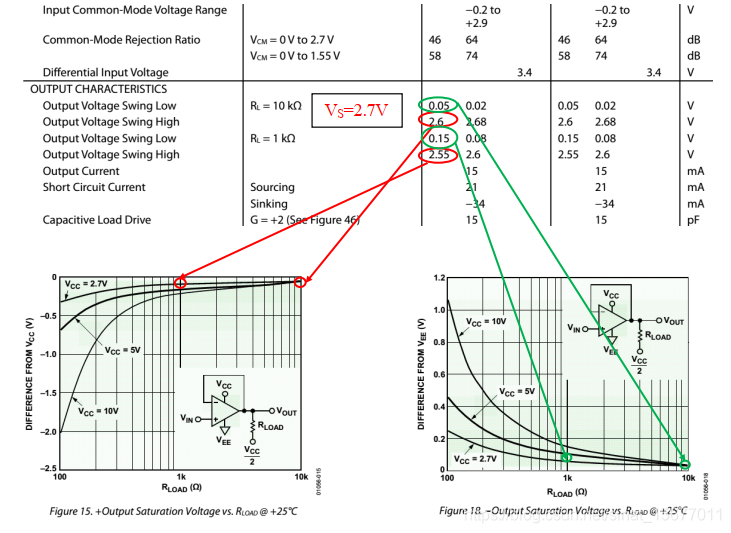

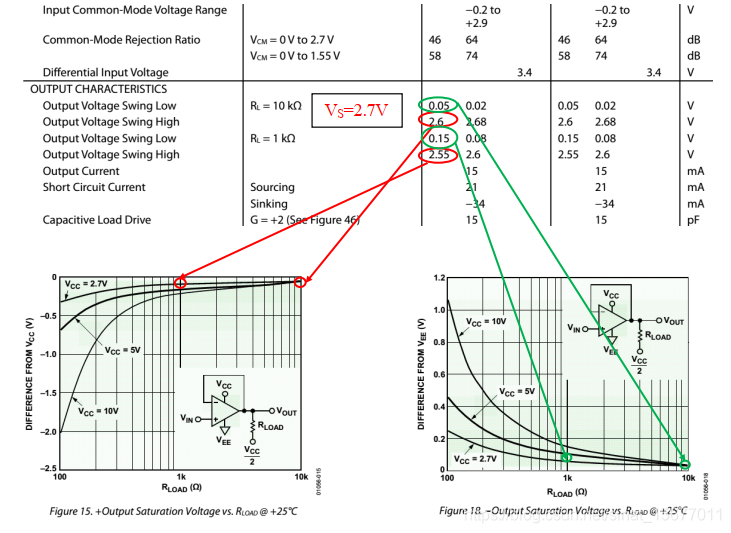

下图摘自可 2.7V 供电的 80MHz, RRIO(输入输出均轨至轨)放大器 AD8031。 其输入范围超出了电源(0~ 2.7V),为-0.2V~2.9V,输出非常接近电源,为 0.02V 到 2.68V,仅有20mV 的至轨电压。

共模抑制比(Common-mode rejection ratio, CMRR)

定义:

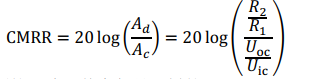

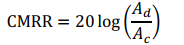

差模电压增益与共模电压增益的比值,用 dB 表示。

优劣范围:

一般运放都有 60dB 以上的 CMRR,高级的可达 140dB 以上

理解:

运算放大器在单端输入使用时,不存在这个概念。只有把运放接成类似于减法器形式,使得运放电路具备两个可变的输入端时,此指标才会发挥作用。

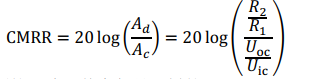

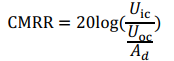

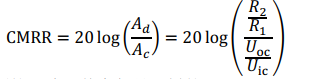

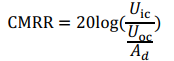

图 2-19 电路中,差模增益 Ad=R2 ⁄R1,如果给电路的两个输入端施加相同的输入电压Uic,在输出端理论上应为 0 输出,实际会测量到由 Uic 引起的输出 Uoc, 则共模抑制比为:

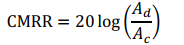

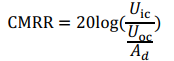

生产厂家更习惯于下面的写法,其实都是一样的。

其实就是现将输出电压按照差模增益折算到入端,再让输入电压除以它——共模输入被抑制了多少倍。

影响电路共模抑制比的因素有两个,

第一是运放本身的共模抑制比,

第二是对称电路中各个电阻的一致性。

其实更多情况下,实现这类电路的高共模抑制比,关键在于外部电阻的一致性。

此时,分立元件实现的电路,很难达到较高的 CMRR,运放生产厂家提供的差动放大器就显现出了优势。

开环电压增益(Open-loop gain, AVO)

定义:

运放本身具备的输出电压与两个输入端差压的比值,用 dB 表示。

优劣范围:

一般在 60dB~160dB 之间。越大的,说明其放大能力越强。

理解:

开环电压增益是指放大器在闭环工作时,实际输出除以运放正负输入端之间的压差,类似于运放开环工作——其实运放是不能开环工作的。

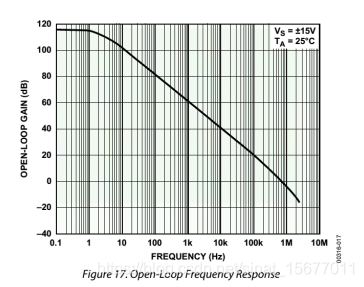

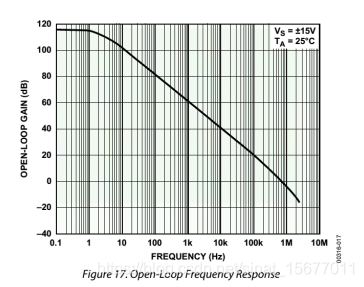

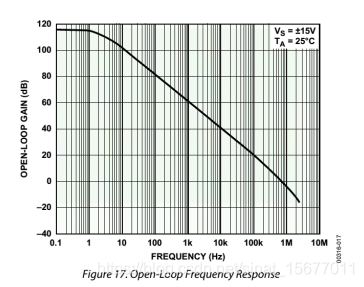

AVO 随频率升高而降低,通常从运放内部的第一个极点开始,其增益就以-20dB/10 倍频的速率开始下降,第二个极点开始加速下降。 如图为 OP07 开环增益与信号频率之间的关系。

一般情况下,说某个运放的开环电压增益达到 100dB,是指其低频最高增益。多数情况下,很少有人关心这个指标,而去关心它的下降规律,即后续讲述的单位增益带宽,或者增益带宽积。

在特殊应用中,比如高精密测量、低失真度测量中需要注意此指标。在某个频率处实际的开环电压增益,将决定放大器的实际放大倍数与设计放大倍数的误差,也将决定放大器对自身失真的抑制,还将影响输出电阻等。

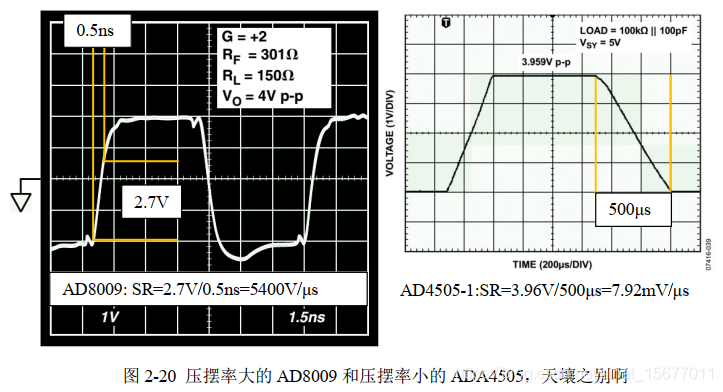

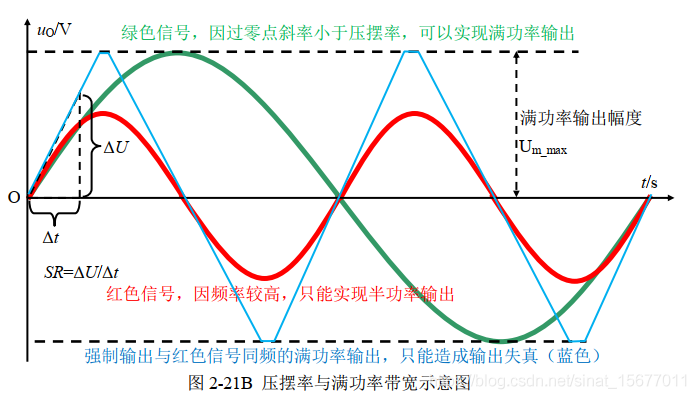

压摆率(Slew rate, SR)

定义:

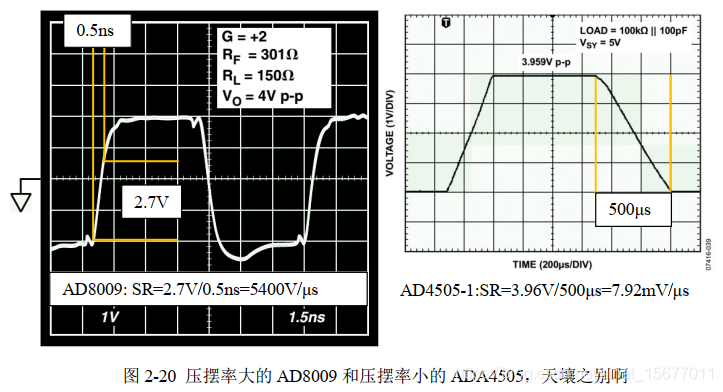

闭环放大器输出电压变化的最快速率。用 V/μs 表示。

优劣范围:

从 2mV/μs 到 9000V/μs 不等。

理解:

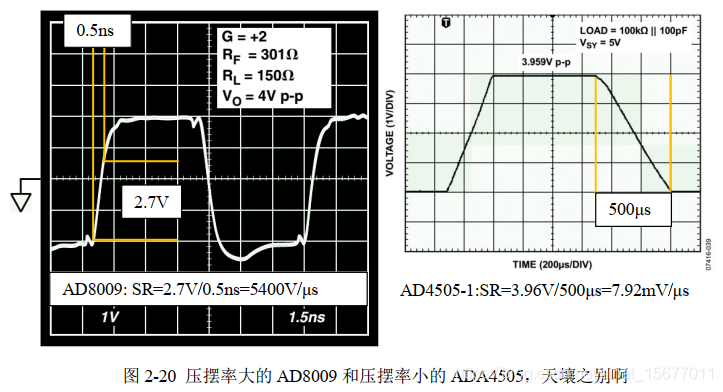

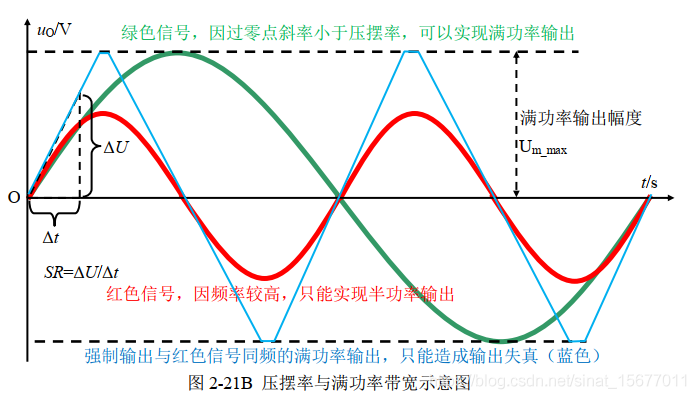

此值显示运放正常工作时,输出端所能提供的最大变化速率,当输出信号欲实现比这个速率还快的变化时,运放就不能提供了,导致输出波形变形——原本是正弦波就变成了三角波。

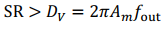

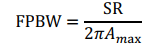

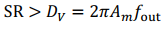

对一个正弦波来说,其最大变化速率发生在过零点处, 且与输出信号幅度、频率有关。设输出正弦波幅度为 Am,频率为 fout,过零点变化速率为 DV,则

要想输出完美的正弦波,则正弦波过零点变化速率必须小于运放的压摆率。 即

带宽指标

与带宽相关的指标主要有四项:

单位增益带宽(Unity Gain-bandwidth, UGBW) —f1

定义:

运放开环增益/频率图中,开环增益下降到 1 时的频率。

理解:

当输入信号频率高于此值时,运放的开环增益会小于 1,即此时放大器不再具备放大能力。这是衡量运放带宽的一个主要指标。

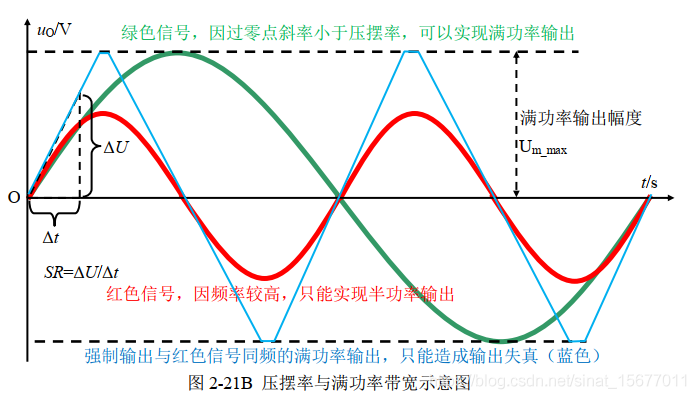

增益带宽积(Gain Bandwidth Product, GBP 或者 GBW) —f2

定义:

运放开环增益/频率图中,指定频率处,开环增益与该指定频率的乘积。

理解:

如果运放开环增益始终满足-20dB/10 倍频,也就是频率提高 10 倍,开环增益变为 0.1 倍,那么它们的乘积将是一个常数,也就等于前述的“单位增益带宽”,或者“ 1Hz处的增益”。

在一个相对较窄的频率区域内,增益带宽积可以保持不变,基本满足-20dB/10 倍频的关系,我们暂称这个区域为增益线性变化区。

-3dB 带宽—f3

定义:

运放闭环使用时,某个指定闭环增益(一般为 1 或者 2、 10 等)下,增益变为低频增益的 0.707 倍时的频率。 分为小信号(输出 200mV 以下)大信号(输出 2V)两种。

理解:

它直接指出了使用该运放可以做到的-3dB 带宽。因为前述的两个指标,单位增益带宽和增益带宽积,其实都是对运放开环增益性能的一种描述,来自开环增益/频率图。而这个指标是对运放接成某种增益的放大电路实施实测得到的。

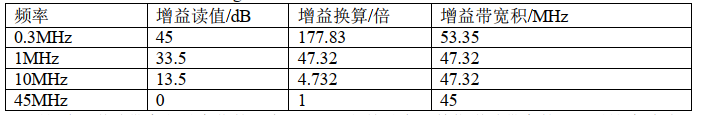

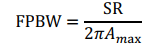

满功率带宽(Full Power Bandwidth) —f0

定义:

将运放接成指定增益闭环电路(一般为 1 倍),连接指定负载,输入加载正弦波,输出为指标规定的最大输出幅度,此状态下,不断增大输入信号频率,直到输出出现因压摆率限制产生的失真(变形)为止,此频率即为满功率带宽。

理解:

比-3dB 带宽更为苛刻的一个限制频率。它指出在此频率之内,不但输出幅度不会降低,且能实现满幅度的大信号带载输出。 满功率带宽与器件压摆率密切相关:

其中, Aax为运放能够输出的最大值(即满功率值)

大小关系

一般情况下, f1《f2,且差不多,因此很少有数据手册同时给出这两个表格型指标。 f3 可能大些,也可能小些,取决于开环特性中的相频特性,但与前两者不会差很大。满功率带宽一般远小于前三者。

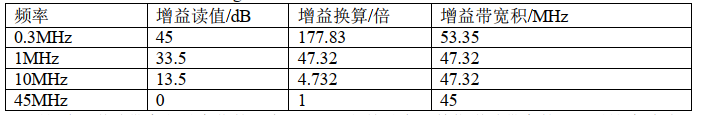

举例说明。 AD8031 的开环增益图如图 Figure 29,右侧纵轴是增益 GAIN/dB,注意

0dB 发生在频率约为 45MHz 的地方,说明单位增益带宽为 45MHz。

再看增益带宽积。我从 Figure 29 读出的数据如下:

这说明增益带宽积是变化的,在 45MHz 之前是大于单位增益带宽的。 但是这个结论没有普适性,只是个体呈现。

而 Figure26 是 AD8031 组成一个 1 倍增益放大电路后的幅频特性, 0dB 发生在 75MHz处, -3dB 发生在大约 90MHz~100MHz 之间。这说明它的-3dB 带宽为 90MHz 左右,大于单位增益带宽。

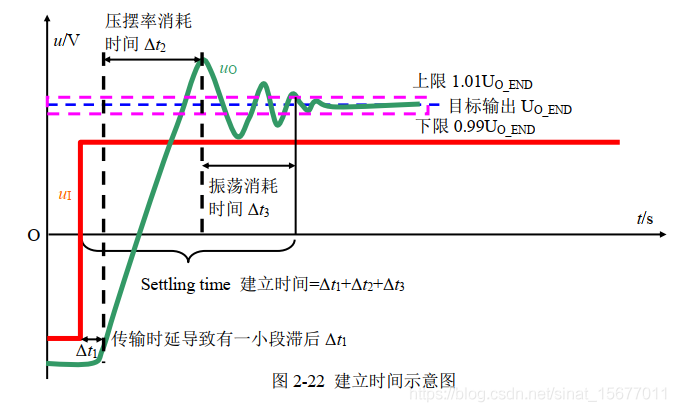

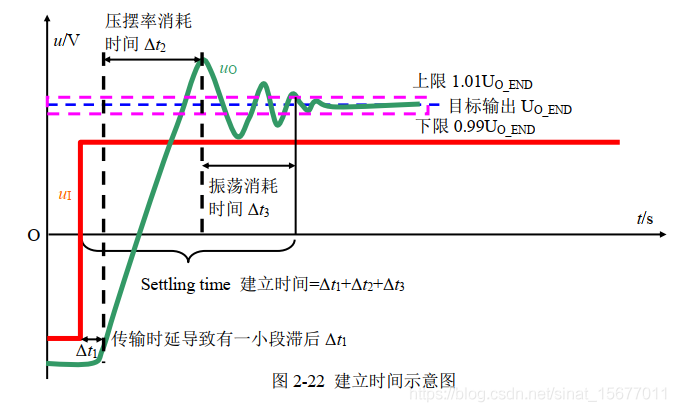

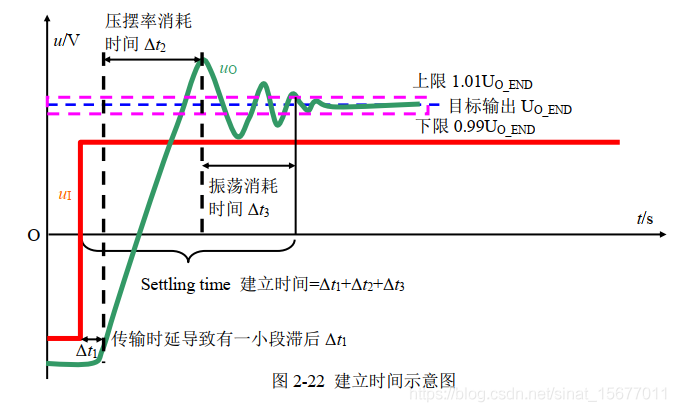

建立时间(Settling Time)

定义:

运放接成指定增益(一般为 1),从输入阶跃信号开始,到输出完全进入指定误

差范围所需要的时间。 所谓的指定误差范围,一般有 1%, 0.1%几种。

优劣范围:

几个 ns 到几个 ms。

理解:

建立时间由三部分组成,

第一是运放的延迟,

第二是压摆率带来的爬坡时间,

第三是稳定时间。

很显然,这个指标与 SR 密切相关,一般来说, SR 越大的,建立时间更小。

对运放组成的 ADC 驱动电路,建立时间是一个重要指标。

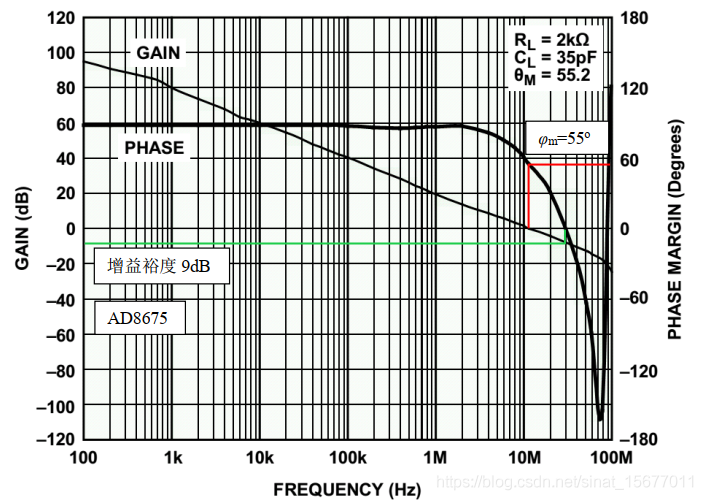

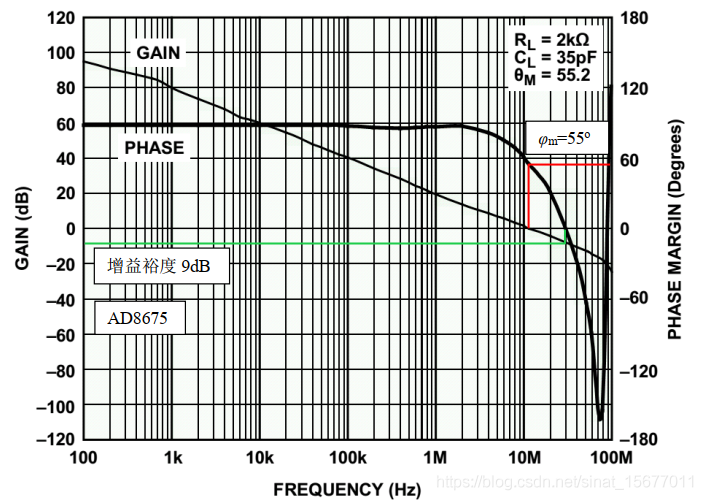

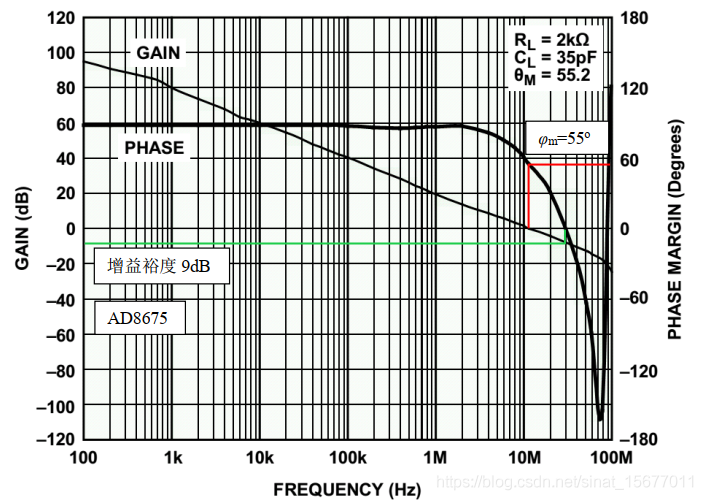

相位裕度(Phase margin)和增益裕度

相位裕度定义:

在运放开环增益和开环相移图中,当运放的开环增益下降到 1 时,开环相移值减去-180°得到的数值。

增益裕度定义:

在运放开环增益和开环相移图中,当运放的开环相移下降到-180°时,增益 dB 值取负,或者是增益值的倒数。

理解:相位裕度和增益裕度越大,说明放大器越容易稳定。

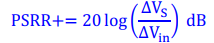

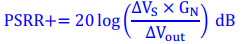

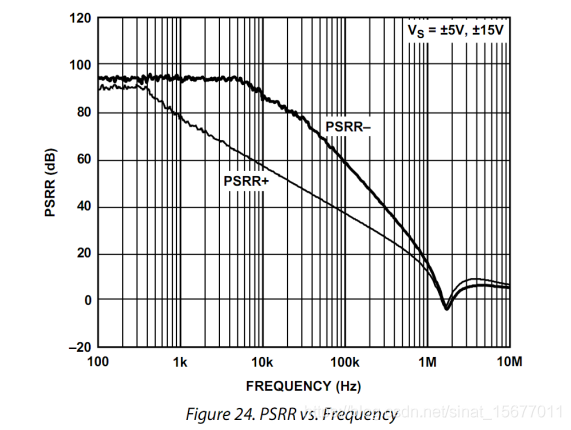

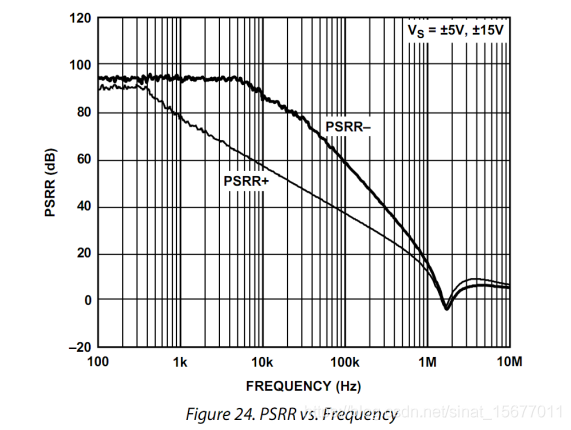

电源电压抑制比(PSRR-Power Supply RejectionRatio)

理论上,当电源电压发生改变时,运放构成的放大电路输出不应该变化。但是实际却会变化——放大电路的噪声增益 GN 越大, 由此带来的输出的变化量也越大。为了产生一个与电路增益无关的指标,电源电压抑制比定义如下:

定义:

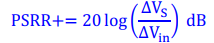

双电源供电电路中,保持负电源电压不变,输入不变,而让正电源产生变化幅度为 ΔVS,频率为 f 的波动。那么在输出端会产生变化幅度为 ΔVout,频率为 f 的波动。这等效于电源稳定不变情况下,在入端施加了一个变化幅度为 ΔVin,频率为 f 的波动。则

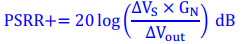

考虑到电路本身的噪声增益 GN,则

同样的方法,保持正电源电压不变,仅改变负电源电压,会得到 PSRR-

有些运放在描述 PSRR 时,不区分单独改变某个电源电压,而仅给出 PSRR,这是指两个电源电压同时改变。注意,两个电源的改变方向是相反的——即保持正负电源的绝对值相等。

理解:

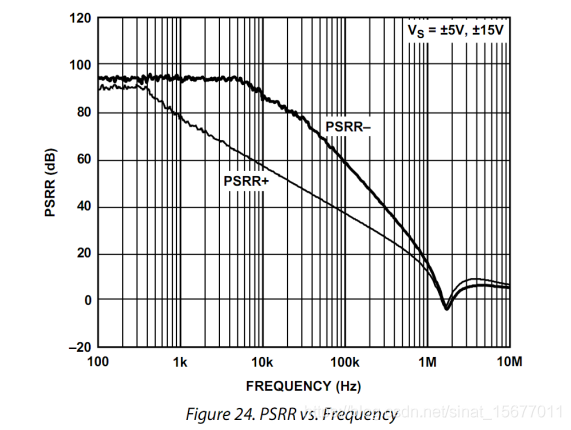

电源电压抑制比,**其含义是运放对电源上纹波或者噪声的抵抗能力。**首先,正负电源具有不一定相同的 PSRR,其次,随着电源电压变化频率的提升,运放对这个变化的抵抗能力会下降。 一般情况下,电源变化频率接近其带宽时,运放会失去对电源变化的抵抗——即单位增益情况下电源变化多少,输出就变化多少。

下图为 ADA4000-1 的 PSRR 图。

频率越高,运放对电源纹波或者噪声的抵抗能力越弱,这导致运放电路的输出端会出现电源上的不干净因素。旁路电容的作用就是滤除电源上的噪声或者波动,特别在高频处,更需要滤除。

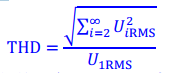

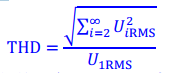

全谐波失真加噪声 THD+Noise

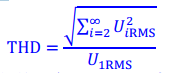

全谐波失真 (Total Harmonic Distortion-THD)本身是衡量一个时域波形与标准正弦波的差异程度的量,其原始定义为:时域波形中包含基波分量有效值 U1RMS,以及各次谐波分量 U2RMS、 U3RMS、 U4RMS……等,则

即全部谐波有效值(各次谐波有效值的平方和开根号)与基波有效值的比值。一般用%表示,也可以用 dB 表示,即上述计算值取对数乘以 20。

对一个标准正弦波来说,它的 THD 等于 0,就是说它除了基波之外,没有任何谐波。但是,迄今为止还没有任何一个设备,可以产生一个 THD 等于 0 的标准正弦波,一般的信号源产生的正弦波,都具有 1%~0.01%的全谐波失真度,或者-40dB ~-80dB 的 THD。

此指标也被用于衡量一个放大器的保真程度——输出是否产生了相对于输入的失真,方法是: 让放大器组成指定增益的放大电路,在输入端施加一个标准正弦波(尽量很小的失真度,这取决于测量要求,选用不同等级的设备),测量输出波形的失真度,即为放大器的失真度。

放大器的失真度越小,越适合于放大保真度要求很高的信号,比如高档音频设备,其放大器微弱的失真都会被那些魔鬼般的耳朵听出来,此时低失真度的放大器就有了用武之地。

在实际测试中,一般都采用数字采样、数字分析方法实施失真度测量。用一个失真度很小的信号源加载到被测放大电路的输入端,用失真度很小的 AD 转换器对输出信号实施高精度采集,然后用数学分析(傅里叶变换)的方法,计算获得输出波形中的基波有效值,以及各次谐波有效值,用上述标准公式计算即可。理论上谐波次数为无穷大次,但实

际操作中一般取有限次谐波,比如 2 次到 7 次谐波——更高次的谐波对总的失真度贡献不大。

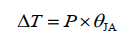

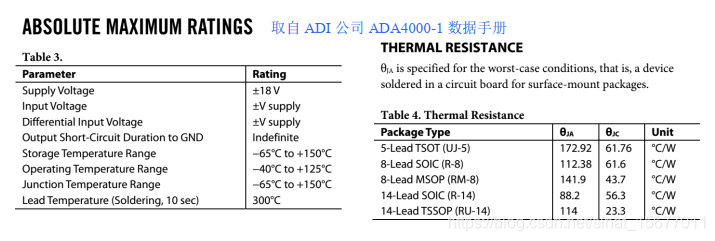

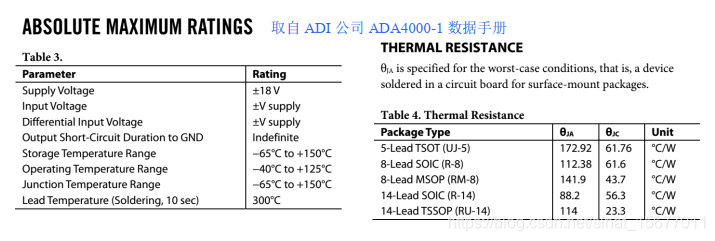

热阻(Thermal resistance, θJA)和温度范围

热阻标准定义:

是导热体阻止热量散失程度的描述,以 1W 发热源在导热路径两端形成的温度差表示,单位为℃/W。有以下常用的两种:

θJA,是指芯片热源结(Junction)与芯片周围环境(Ambient)(一般为空气)的热阻。

θJC,是指芯片热源结(Junction)与芯片管壳(Case)的热阻。

理解:

对芯片来说,导热路径的两端分别为自身发热体与环境空气。热阻 θJA 越大,说明散热越困难,其温差也就越大。

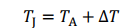

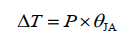

比如一个热阻 θJA=150℃ /W 的芯片,说明其如果存在 1W 的热功率释放(为电源提供给芯片的功率-芯片输出的功率),则会在芯片内核和环境空气中形成一个 150℃的温差。当确定热功率释放为 P,则

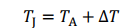

其中Δ T 是芯片工作时,自身结温与环境温度的温差。 如果此时环境温度为 TA,则芯片结温 TJ 为:

很显然,同样功耗情况下,具有不同热阻的芯片,热阻越大的,结温会越高。当结温超过了最高容许结温(一般就是芯片中声明的存储温度,比如 150℃),芯片就可能发热损坏。

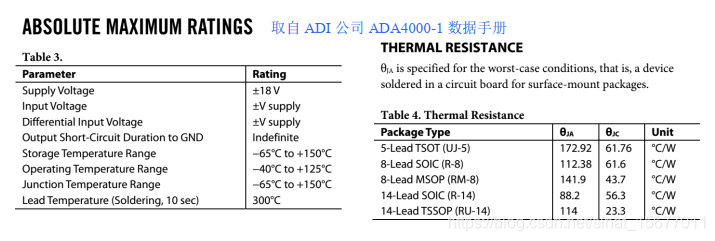

应用热阻指标可以帮助设计者估算芯片可否安全工作。如下图查到 ADA4000-1 关于热阻的描述,

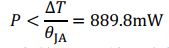

可知 SOIC8 封装热阻为 112.38℃ /W,结温不得超过 150℃ 。 假设设计者使用SOIC8 封装,则在-10~50℃环境下(一般气温范围), 为保证结温不超过 150℃, ΔT 需小于 100℃。因此,设计电路时,需要注意 ADA4000-1 的发热功耗不得超过

而发热功耗与输出功率相关,一般情况下,输出功率越大,会带来芯片本身发热功耗的增加。当然,对 ADA4000-1 来说,产生如此大的发热功耗是不可能的,对于高频运放则很正常。 可以看出, 选择热阻更小的 14 脚封装的 SOIC(也就是 SO-14), 具有 88.2℃ /W 的热阻, 则可以有效改善。

理论上说,你看看芯片的大小(就能估计出热阻),摸摸芯片的温度,通过色环读出负载电阻的大小,就可以粗略估计出输出电压幅度,看似很神奇,其实也很简单。

输入电压范围(Input Voltage Range)

定义:

保证运算放大器正常工作的最大输入电压范围。也称为共模输入电压范围。

优劣评定:

一般运放的输入电压范围比电源电压范围窄 1V 到几 V,比如± 15V 供电,输入电压范围在-12V~13V。较好的运放输入电压范围和电源电压范围相同,甚至超出范围 0.1V。比如±15V 供电,输入范围在-15.1V 到 15.0V,这会使得放大器设计具有更大的输入动态范围,提高电路的适应性。

当运放最大输入电压范围与电源范围比较接近时,比如相差 0.1V 甚至相等、超过,都可以叫“输入轨至轨”,表示为 Rail-to-rail input,或 RRI。

理解:

运放的两个输入端,任何一个的输入电压超过此范围,都将引起运放的失效。注意,超出此范围并不代表运放会被烧毁,但绝对参数中出现的此值是坚决不能超过的。

之所以叫共模输入电压范围,是因为运放正常工作时,两个输入端之间的差压是很小的,某个输入端的电压与两个输入端电压的平均值(共模)是基本相同的(负反馈得结果,虚短)

图 2-18 给出了输入电压范围和输出电压范围的示意。下方的 OP07 数据手册中,可以看出它的供电电压范围在±15V 时,其输入电压范围只有±14V。

输出电压范围(VOH/VOL 或者 Swing from rail)

定义:

在给定电源电压和负载情况下,输出能够达到的最大电压范围。或者给出正向最大电压 VOH 以及负向最小电压 VOL——相对于给定的电源电压和负载;或者给出与电源轨(rail)的差距。

优劣范围:

一般运放的输出电压范围要比电源电压范围略窄 1V 到几 V。较好的运放输出电压范围可以与电源电压范围非常接近,比如几十 mV 的差异,这被称为“输出至轨电压”。这在低电压供电场合非常有用。当厂家觉得这个运放的输出范围已经接近于电源电压范围时,就自称“输出轨至轨”,表示为 Rail-to-rail output,或 RRO。

理解:

在没有额外的储能元件情况下,运放的输出电压不可能超过电源电压范围,随着负载的加重,输出最大值与电源电压的差异会越大。这需要看数据手册中的附图。

输出电压范围,或者输出至轨电压有如下特点:

1) 正至轨电压与负至轨电压的绝对值可能不一致,但一般情况下数量级相同;

2) 至轨电压与负载密切相关,负载越重(阻抗小) 至轨电压越大;(负载电阻越小,负载电流越大,输出电阻上产生得压降越大,所以输出电压,也就是负载两端得电压越小)。

3) 至轨电压与信号频率相关,频率越高,至轨电压越大,甚至会突然大幅度下降;

4) 至轨电压在 20mV 以内,属于非常优秀。

下图摘自可 2.7V 供电的 80MHz, RRIO(输入输出均轨至轨)放大器 AD8031。 其输入范围超出了电源(0~ 2.7V),为-0.2V~2.9V,输出非常接近电源,为 0.02V 到 2.68V,仅有20mV 的至轨电压。

共模抑制比(Common-mode rejection ratio, CMRR)

定义:

差模电压增益与共模电压增益的比值,用 dB 表示。

优劣范围:

一般运放都有 60dB 以上的 CMRR,高级的可达 140dB 以上

理解:

运算放大器在单端输入使用时,不存在这个概念。只有把运放接成类似于减法器形式,使得运放电路具备两个可变的输入端时,此指标才会发挥作用。

图 2-19 电路中,差模增益 Ad=R2 ⁄R1,如果给电路的两个输入端施加相同的输入电压Uic,在输出端理论上应为 0 输出,实际会测量到由 Uic 引起的输出 Uoc, 则共模抑制比为:

生产厂家更习惯于下面的写法,其实都是一样的。

其实就是现将输出电压按照差模增益折算到入端,再让输入电压除以它——共模输入被抑制了多少倍。

影响电路共模抑制比的因素有两个,

第一是运放本身的共模抑制比,

第二是对称电路中各个电阻的一致性。

其实更多情况下,实现这类电路的高共模抑制比,关键在于外部电阻的一致性。

此时,分立元件实现的电路,很难达到较高的 CMRR,运放生产厂家提供的差动放大器就显现出了优势。

开环电压增益(Open-loop gain, AVO)

定义:

运放本身具备的输出电压与两个输入端差压的比值,用 dB 表示。

优劣范围:

一般在 60dB~160dB 之间。越大的,说明其放大能力越强。

理解:

开环电压增益是指放大器在闭环工作时,实际输出除以运放正负输入端之间的压差,类似于运放开环工作——其实运放是不能开环工作的。

AVO 随频率升高而降低,通常从运放内部的第一个极点开始,其增益就以-20dB/10 倍频的速率开始下降,第二个极点开始加速下降。 如图为 OP07 开环增益与信号频率之间的关系。

一般情况下,说某个运放的开环电压增益达到 100dB,是指其低频最高增益。多数情况下,很少有人关心这个指标,而去关心它的下降规律,即后续讲述的单位增益带宽,或者增益带宽积。

在特殊应用中,比如高精密测量、低失真度测量中需要注意此指标。在某个频率处实际的开环电压增益,将决定放大器的实际放大倍数与设计放大倍数的误差,也将决定放大器对自身失真的抑制,还将影响输出电阻等。

压摆率(Slew rate, SR)

定义:

闭环放大器输出电压变化的最快速率。用 V/μs 表示。

优劣范围:

从 2mV/μs 到 9000V/μs 不等。

理解:

此值显示运放正常工作时,输出端所能提供的最大变化速率,当输出信号欲实现比这个速率还快的变化时,运放就不能提供了,导致输出波形变形——原本是正弦波就变成了三角波。

对一个正弦波来说,其最大变化速率发生在过零点处, 且与输出信号幅度、频率有关。设输出正弦波幅度为 Am,频率为 fout,过零点变化速率为 DV,则

要想输出完美的正弦波,则正弦波过零点变化速率必须小于运放的压摆率。 即

带宽指标

与带宽相关的指标主要有四项:

单位增益带宽(Unity Gain-bandwidth, UGBW) —f1

定义:

运放开环增益/频率图中,开环增益下降到 1 时的频率。

理解:

当输入信号频率高于此值时,运放的开环增益会小于 1,即此时放大器不再具备放大能力。这是衡量运放带宽的一个主要指标。

增益带宽积(Gain Bandwidth Product, GBP 或者 GBW) —f2

定义:

运放开环增益/频率图中,指定频率处,开环增益与该指定频率的乘积。

理解:

如果运放开环增益始终满足-20dB/10 倍频,也就是频率提高 10 倍,开环增益变为 0.1 倍,那么它们的乘积将是一个常数,也就等于前述的“单位增益带宽”,或者“ 1Hz处的增益”。

在一个相对较窄的频率区域内,增益带宽积可以保持不变,基本满足-20dB/10 倍频的关系,我们暂称这个区域为增益线性变化区。

-3dB 带宽—f3

定义:

运放闭环使用时,某个指定闭环增益(一般为 1 或者 2、 10 等)下,增益变为低频增益的 0.707 倍时的频率。 分为小信号(输出 200mV 以下)大信号(输出 2V)两种。

理解:

它直接指出了使用该运放可以做到的-3dB 带宽。因为前述的两个指标,单位增益带宽和增益带宽积,其实都是对运放开环增益性能的一种描述,来自开环增益/频率图。而这个指标是对运放接成某种增益的放大电路实施实测得到的。

满功率带宽(Full Power Bandwidth) —f0

定义:

将运放接成指定增益闭环电路(一般为 1 倍),连接指定负载,输入加载正弦波,输出为指标规定的最大输出幅度,此状态下,不断增大输入信号频率,直到输出出现因压摆率限制产生的失真(变形)为止,此频率即为满功率带宽。

理解:

比-3dB 带宽更为苛刻的一个限制频率。它指出在此频率之内,不但输出幅度不会降低,且能实现满幅度的大信号带载输出。 满功率带宽与器件压摆率密切相关:

其中, Aax为运放能够输出的最大值(即满功率值)

大小关系

一般情况下, f1《f2,且差不多,因此很少有数据手册同时给出这两个表格型指标。 f3 可能大些,也可能小些,取决于开环特性中的相频特性,但与前两者不会差很大。满功率带宽一般远小于前三者。

举例说明。 AD8031 的开环增益图如图 Figure 29,右侧纵轴是增益 GAIN/dB,注意

0dB 发生在频率约为 45MHz 的地方,说明单位增益带宽为 45MHz。

再看增益带宽积。我从 Figure 29 读出的数据如下:

这说明增益带宽积是变化的,在 45MHz 之前是大于单位增益带宽的。 但是这个结论没有普适性,只是个体呈现。

而 Figure26 是 AD8031 组成一个 1 倍增益放大电路后的幅频特性, 0dB 发生在 75MHz处, -3dB 发生在大约 90MHz~100MHz 之间。这说明它的-3dB 带宽为 90MHz 左右,大于单位增益带宽。

建立时间(Settling Time)

定义:

运放接成指定增益(一般为 1),从输入阶跃信号开始,到输出完全进入指定误

差范围所需要的时间。 所谓的指定误差范围,一般有 1%, 0.1%几种。

优劣范围:

几个 ns 到几个 ms。

理解:

建立时间由三部分组成,

第一是运放的延迟,

第二是压摆率带来的爬坡时间,

第三是稳定时间。

很显然,这个指标与 SR 密切相关,一般来说, SR 越大的,建立时间更小。

对运放组成的 ADC 驱动电路,建立时间是一个重要指标。

相位裕度(Phase margin)和增益裕度

相位裕度定义:

在运放开环增益和开环相移图中,当运放的开环增益下降到 1 时,开环相移值减去-180°得到的数值。

增益裕度定义:

在运放开环增益和开环相移图中,当运放的开环相移下降到-180°时,增益 dB 值取负,或者是增益值的倒数。

理解:相位裕度和增益裕度越大,说明放大器越容易稳定。

电源电压抑制比(PSRR-Power Supply RejectionRatio)

理论上,当电源电压发生改变时,运放构成的放大电路输出不应该变化。但是实际却会变化——放大电路的噪声增益 GN 越大, 由此带来的输出的变化量也越大。为了产生一个与电路增益无关的指标,电源电压抑制比定义如下:

定义:

双电源供电电路中,保持负电源电压不变,输入不变,而让正电源产生变化幅度为 ΔVS,频率为 f 的波动。那么在输出端会产生变化幅度为 ΔVout,频率为 f 的波动。这等效于电源稳定不变情况下,在入端施加了一个变化幅度为 ΔVin,频率为 f 的波动。则

考虑到电路本身的噪声增益 GN,则

同样的方法,保持正电源电压不变,仅改变负电源电压,会得到 PSRR-

有些运放在描述 PSRR 时,不区分单独改变某个电源电压,而仅给出 PSRR,这是指两个电源电压同时改变。注意,两个电源的改变方向是相反的——即保持正负电源的绝对值相等。

理解:

电源电压抑制比,**其含义是运放对电源上纹波或者噪声的抵抗能力。**首先,正负电源具有不一定相同的 PSRR,其次,随着电源电压变化频率的提升,运放对这个变化的抵抗能力会下降。 一般情况下,电源变化频率接近其带宽时,运放会失去对电源变化的抵抗——即单位增益情况下电源变化多少,输出就变化多少。

下图为 ADA4000-1 的 PSRR 图。

频率越高,运放对电源纹波或者噪声的抵抗能力越弱,这导致运放电路的输出端会出现电源上的不干净因素。旁路电容的作用就是滤除电源上的噪声或者波动,特别在高频处,更需要滤除。

全谐波失真加噪声 THD+Noise

全谐波失真 (Total Harmonic Distortion-THD)本身是衡量一个时域波形与标准正弦波的差异程度的量,其原始定义为:时域波形中包含基波分量有效值 U1RMS,以及各次谐波分量 U2RMS、 U3RMS、 U4RMS……等,则

即全部谐波有效值(各次谐波有效值的平方和开根号)与基波有效值的比值。一般用%表示,也可以用 dB 表示,即上述计算值取对数乘以 20。

对一个标准正弦波来说,它的 THD 等于 0,就是说它除了基波之外,没有任何谐波。但是,迄今为止还没有任何一个设备,可以产生一个 THD 等于 0 的标准正弦波,一般的信号源产生的正弦波,都具有 1%~0.01%的全谐波失真度,或者-40dB ~-80dB 的 THD。

此指标也被用于衡量一个放大器的保真程度——输出是否产生了相对于输入的失真,方法是: 让放大器组成指定增益的放大电路,在输入端施加一个标准正弦波(尽量很小的失真度,这取决于测量要求,选用不同等级的设备),测量输出波形的失真度,即为放大器的失真度。

放大器的失真度越小,越适合于放大保真度要求很高的信号,比如高档音频设备,其放大器微弱的失真都会被那些魔鬼般的耳朵听出来,此时低失真度的放大器就有了用武之地。

在实际测试中,一般都采用数字采样、数字分析方法实施失真度测量。用一个失真度很小的信号源加载到被测放大电路的输入端,用失真度很小的 AD 转换器对输出信号实施高精度采集,然后用数学分析(傅里叶变换)的方法,计算获得输出波形中的基波有效值,以及各次谐波有效值,用上述标准公式计算即可。理论上谐波次数为无穷大次,但实

际操作中一般取有限次谐波,比如 2 次到 7 次谐波——更高次的谐波对总的失真度贡献不大。

热阻(Thermal resistance, θJA)和温度范围

热阻标准定义:

是导热体阻止热量散失程度的描述,以 1W 发热源在导热路径两端形成的温度差表示,单位为℃/W。有以下常用的两种:

θJA,是指芯片热源结(Junction)与芯片周围环境(Ambient)(一般为空气)的热阻。

θJC,是指芯片热源结(Junction)与芯片管壳(Case)的热阻。

理解:

对芯片来说,导热路径的两端分别为自身发热体与环境空气。热阻 θJA 越大,说明散热越困难,其温差也就越大。

比如一个热阻 θJA=150℃ /W 的芯片,说明其如果存在 1W 的热功率释放(为电源提供给芯片的功率-芯片输出的功率),则会在芯片内核和环境空气中形成一个 150℃的温差。当确定热功率释放为 P,则

其中Δ T 是芯片工作时,自身结温与环境温度的温差。 如果此时环境温度为 TA,则芯片结温 TJ 为:

很显然,同样功耗情况下,具有不同热阻的芯片,热阻越大的,结温会越高。当结温超过了最高容许结温(一般就是芯片中声明的存储温度,比如 150℃),芯片就可能发热损坏。

应用热阻指标可以帮助设计者估算芯片可否安全工作。如下图查到 ADA4000-1 关于热阻的描述,

可知 SOIC8 封装热阻为 112.38℃ /W,结温不得超过 150℃ 。 假设设计者使用SOIC8 封装,则在-10~50℃环境下(一般气温范围), 为保证结温不超过 150℃, ΔT 需小于 100℃。因此,设计电路时,需要注意 ADA4000-1 的发热功耗不得超过

而发热功耗与输出功率相关,一般情况下,输出功率越大,会带来芯片本身发热功耗的增加。当然,对 ADA4000-1 来说,产生如此大的发热功耗是不可能的,对于高频运放则很正常。 可以看出, 选择热阻更小的 14 脚封装的 SOIC(也就是 SO-14), 具有 88.2℃ /W 的热阻, 则可以有效改善。

理论上说,你看看芯片的大小(就能估计出热阻),摸摸芯片的温度,通过色环读出负载电阻的大小,就可以粗略估计出输出电压幅度,看似很神奇,其实也很简单。

举报

举报

举报

举报