Quartus II 18.x Modelsim

仿真设置

本节内容介绍在如何在QuartusII 应用环境下设置modelsim仿真选项,并进行波形仿真。下面以四位乘法器为例介绍。

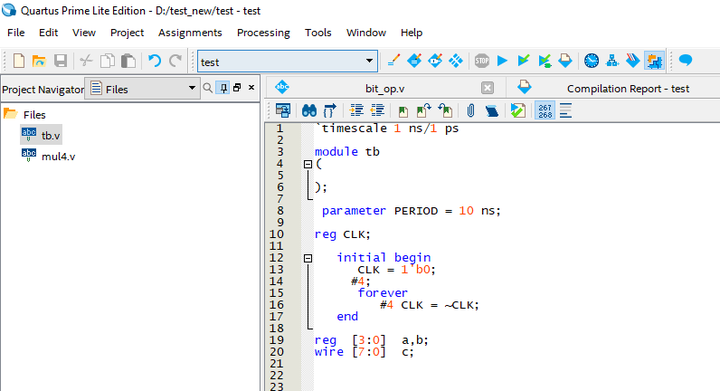

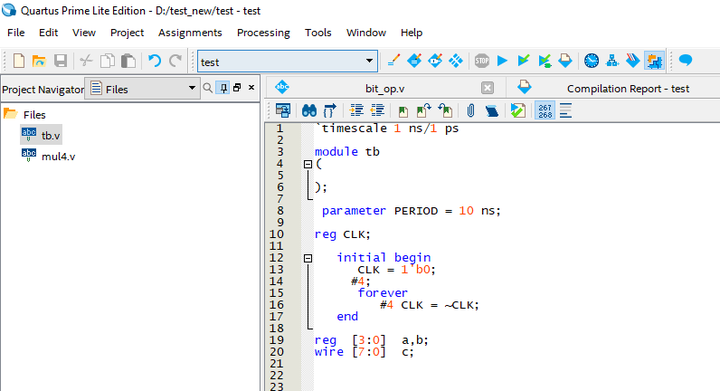

在QuartusII 18.x 的界面下建立两个文件,一个是设计文件mul4.v实现4×4的乘法器;另一个是testbench 文件tb.v,提供激励。

mul4.v文件如下:

module mul4

(

input [3:0] a,

input [3:0] b,

output [7:0] c

);

assign c = a * b;

endmodule

tb.v 文件如下:

`

timescale 1 ns/1 ps

module tb

(

);

parameter PERIOD = 10 ;

reg CLK;

initial

begin

CLK = 1'b0;

#4;

forever

#4 CLK = ~CLK;

end

reg [3:0] a,b;

wire [7:0] c;

initial

begin

a = 4'b0000;

b = 4'b0000;

end

always @(posedge CLK)

begin

a <= a + 1;

if(a == 15)

b <= b + 1;

end

mul4 mul4_dut

(

.a (a),

.b (b),

.c (c)

);

endmodule

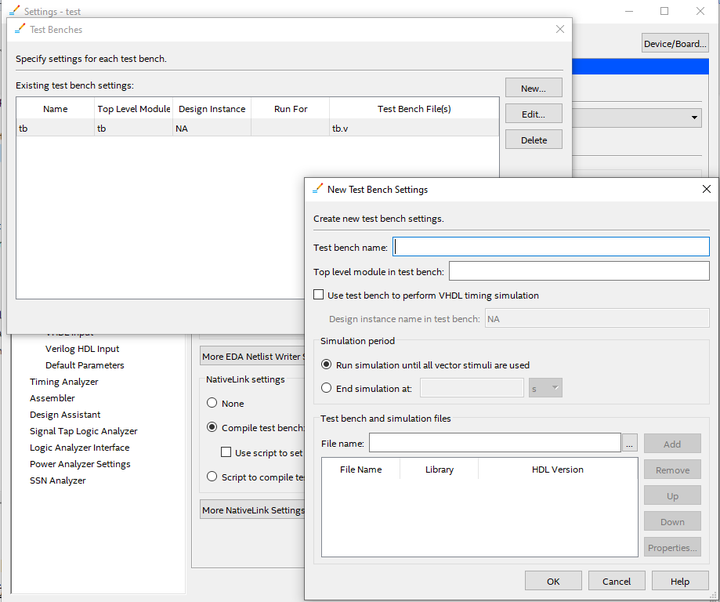

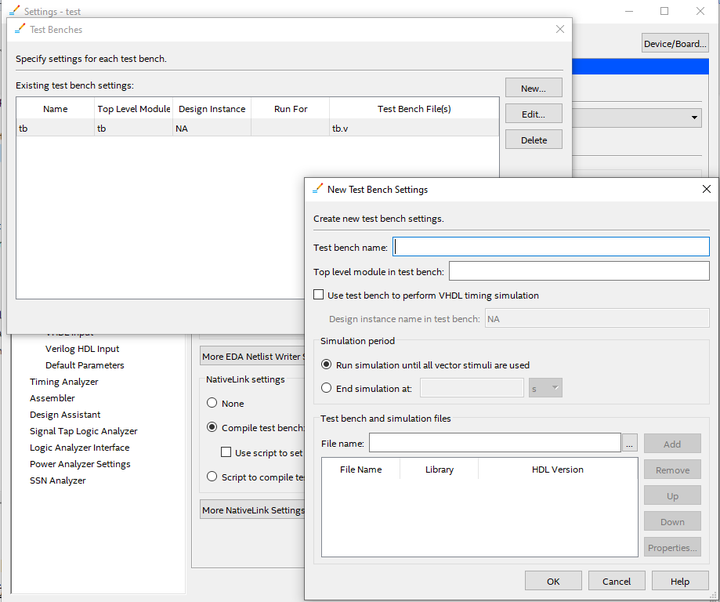

图 1

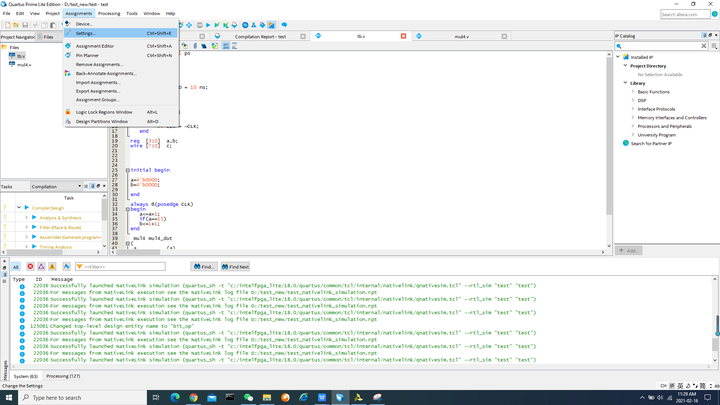

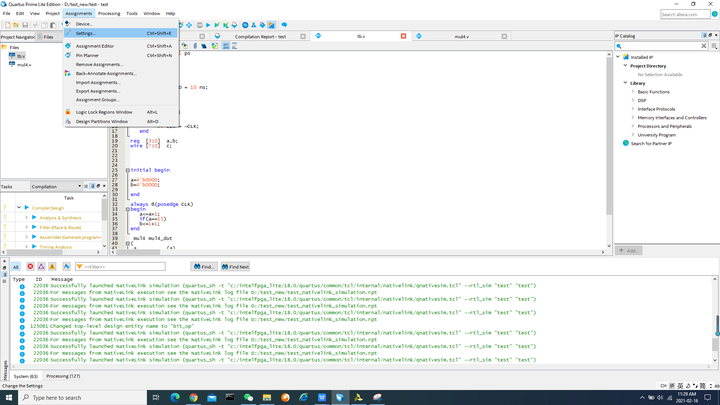

- 在菜单Assignment 下选中Settings…,如下图:

图2

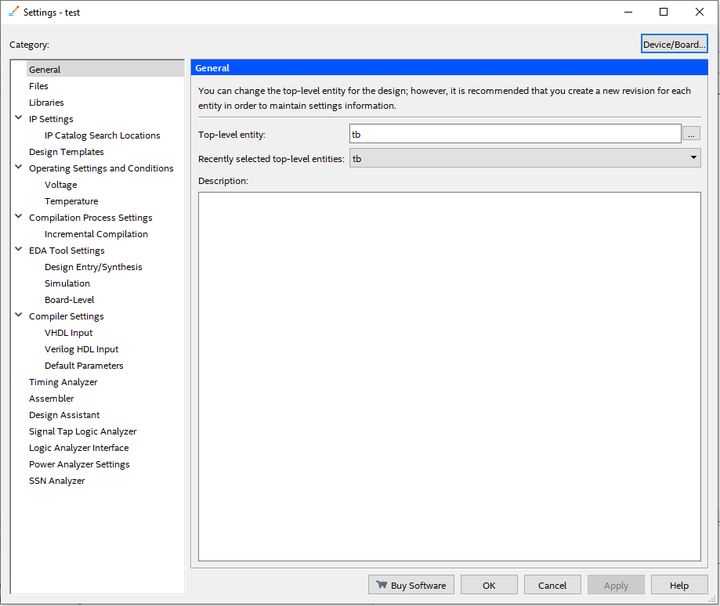

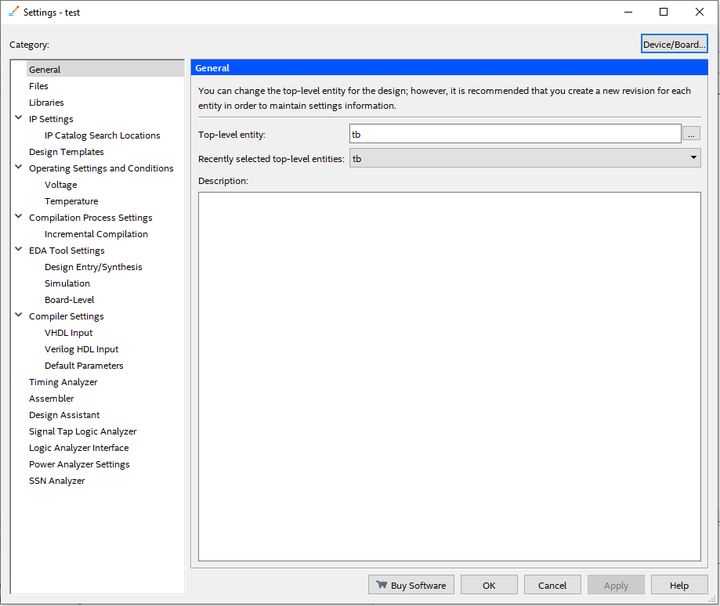

- 打开Settings 对话框

- 在General对话框设置Top-level entity 为tb(testbench 文件)

图3

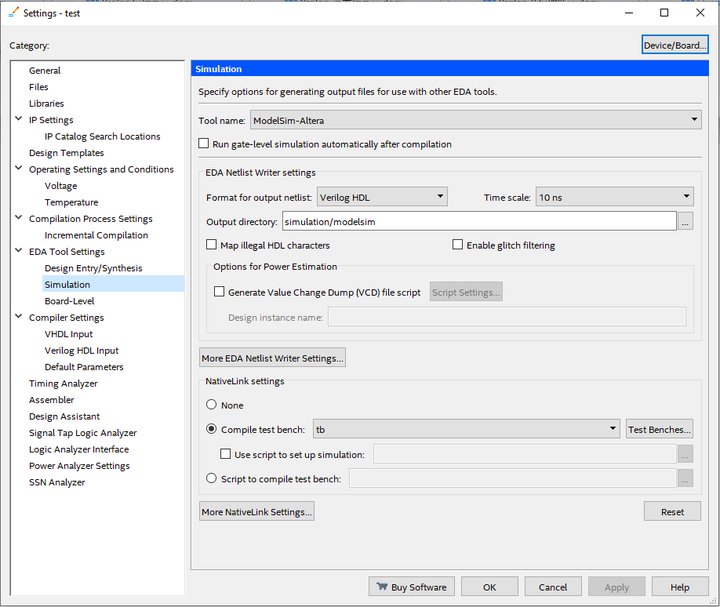

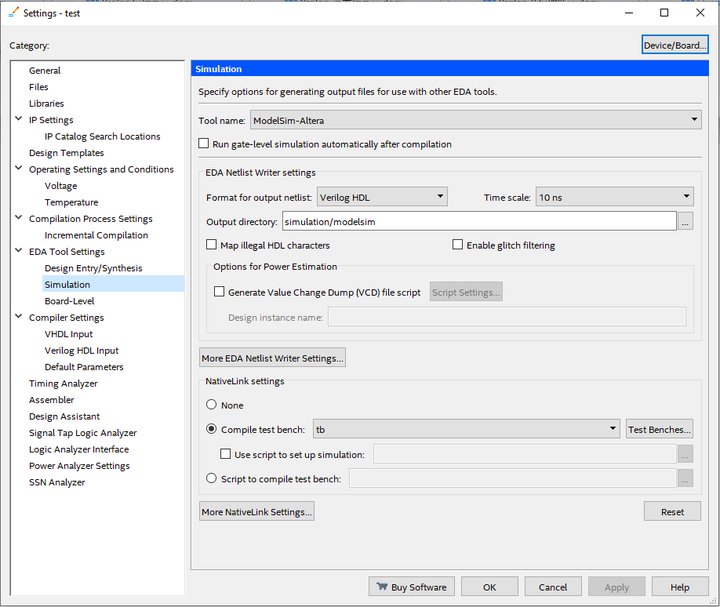

- 在EDA Tools setting 选中 Simulation,如图5

图5

在对话框中 Tool name –>Modelsim-Altera,其它按照图中内容选择。特别是最下方的选项,NativeLink settings… 里设置好 Compile test bench: 如图5,

如果你设计的testbench 文件名不是tb,需要点击test Benches ,选择对应的testbench 文件。如图6,

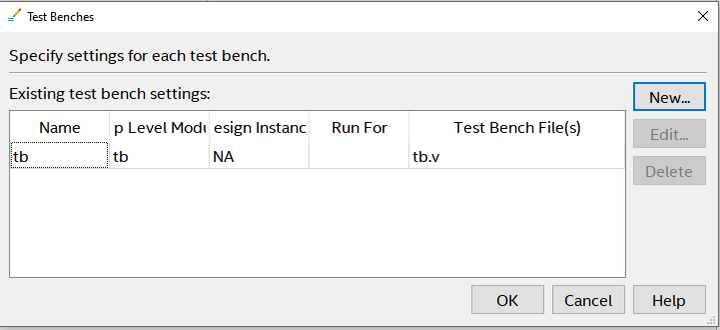

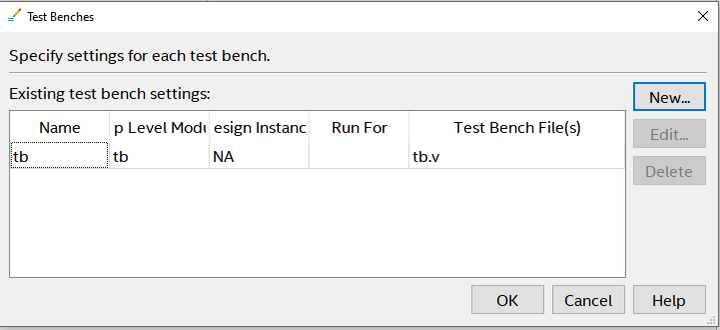

图6

在图6中 Test bench and simulation files部分,点击…部分,进行testbench设定并选取需要的test bench 文件。如:图7

图7

在图7 中,默认的是使用已设定好的testbench,如图中Existing test bench settings: 中Name–>tb, top Level Model name –>tb, test Bench File(s)–>tb.v.

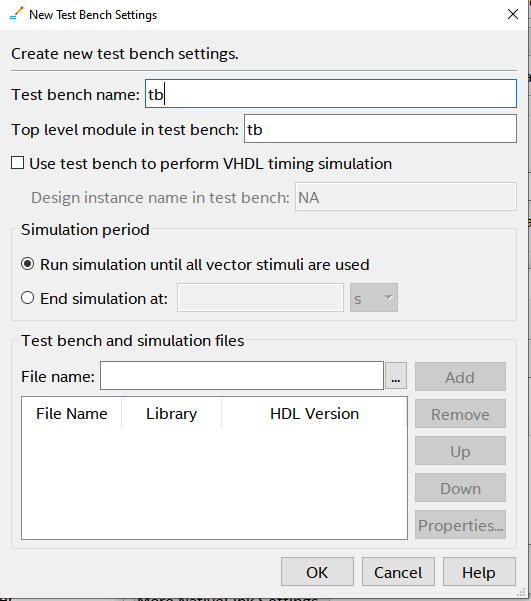

如果首次使用,要点击New…按钮,进行新testbench设定,如图8:

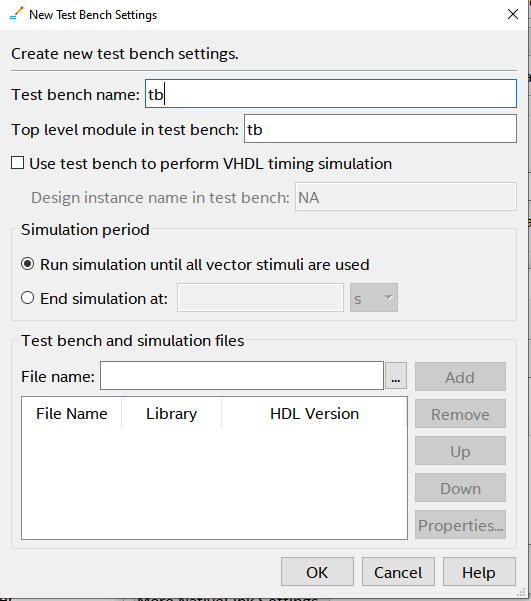

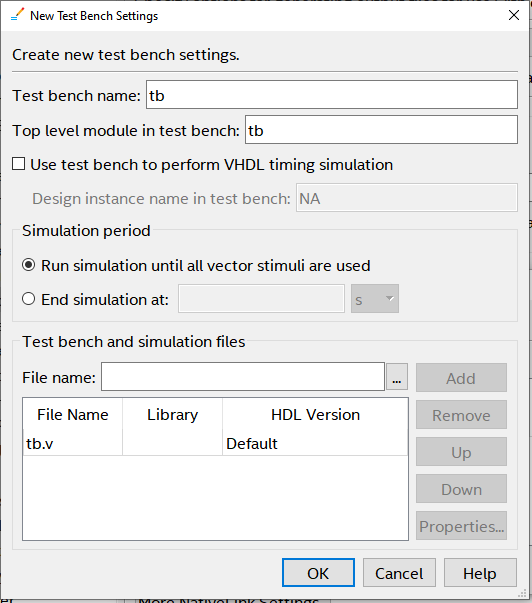

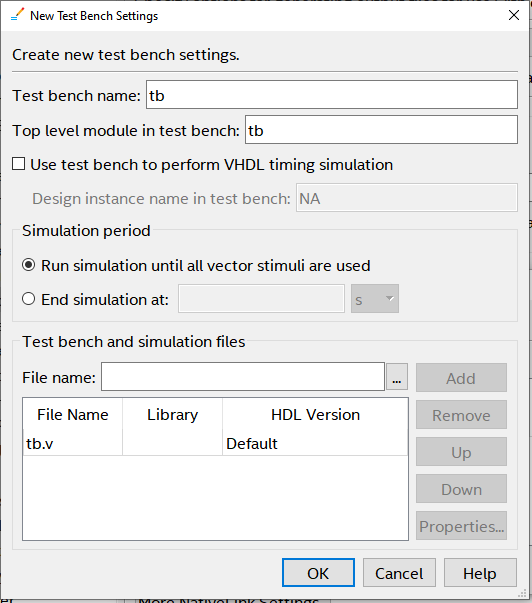

图8

在图8中,testbench name–>tb, top Level Model in testbench file–>tb, 注意:这里的名称一定要与下一个步骤的文件名一致。如图9

在Simulation Period 的选项中,如果在testbench中的激励是有限项选择Run simulation utile all Vector stimuli are used,如本例在initial给的仿真只有有限项,如果是无限项如时钟驱动的仿真。

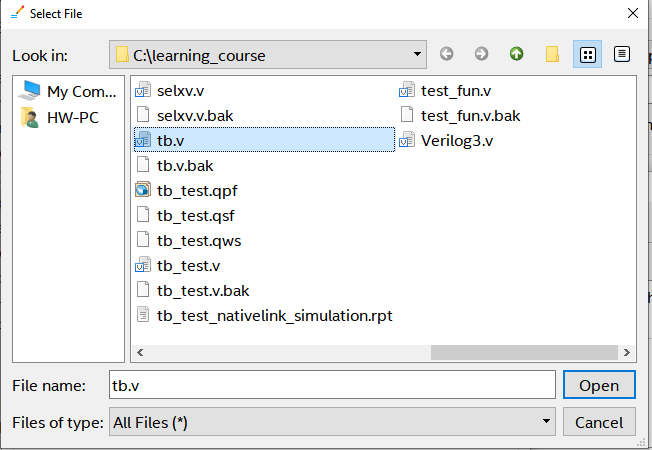

在test bench and simulation files 中点击…选文件,跳出对话框如图9.

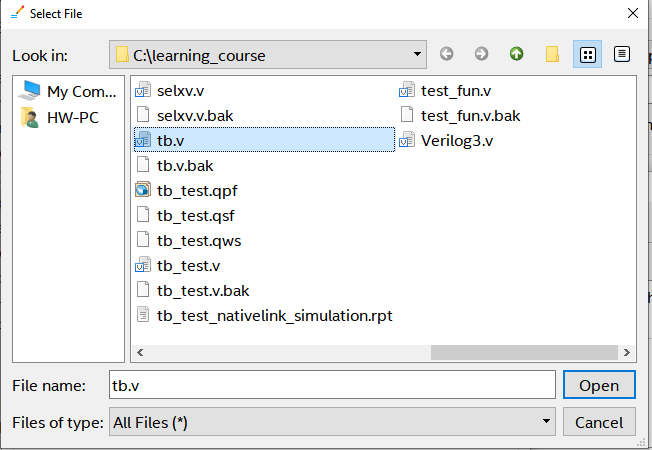

图9

在图9中选择好对应的文件,如tb.v,这个文件将会被modelsim编译,形成激励条件。然后在图8中点击ADD按钮,加入库中如图10.

图10

图10中的文件名tb要和上面的test bench name以及top Level module in test bench 名字一致,本例中都是tb.

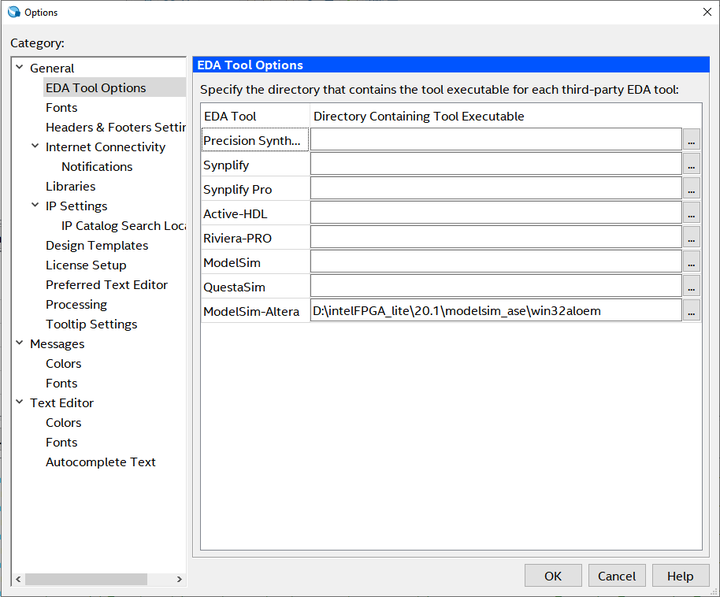

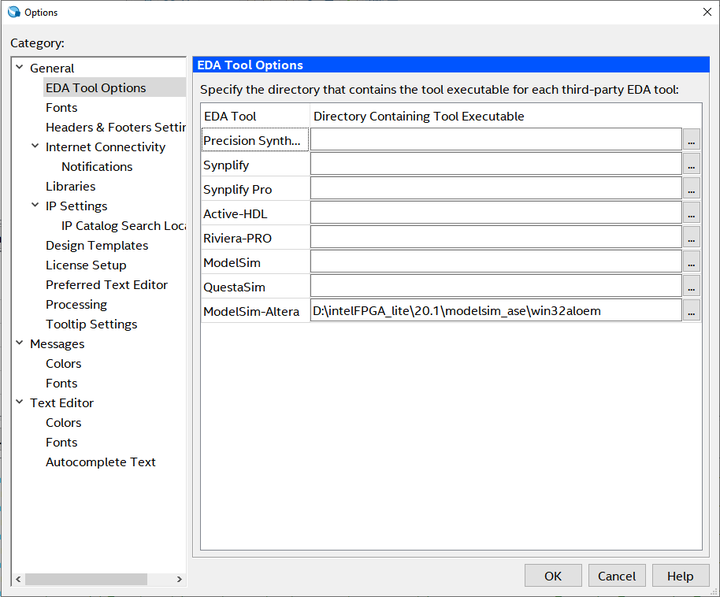

检查编译工具目录,点击菜单Tools->Options, General-> EDA Tool Options 如图11,

图11

- 在Project Navigator 里选取mul4.v, 鼠标右键单击,Set as top level entity。单击工具栏图标Start Analysis and Elaboration, 如果有语法错误,则修改,直到没有错误为止。

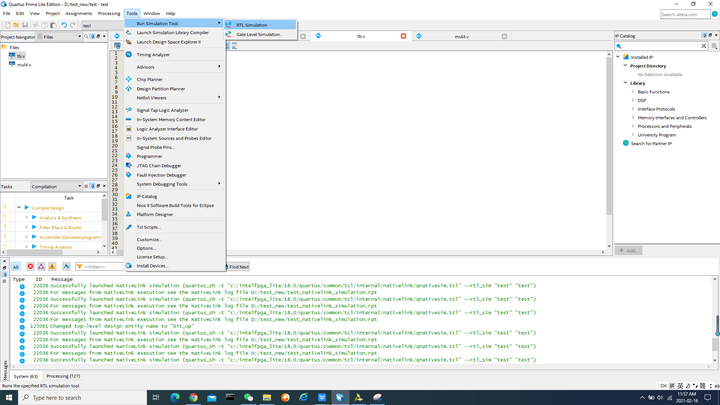

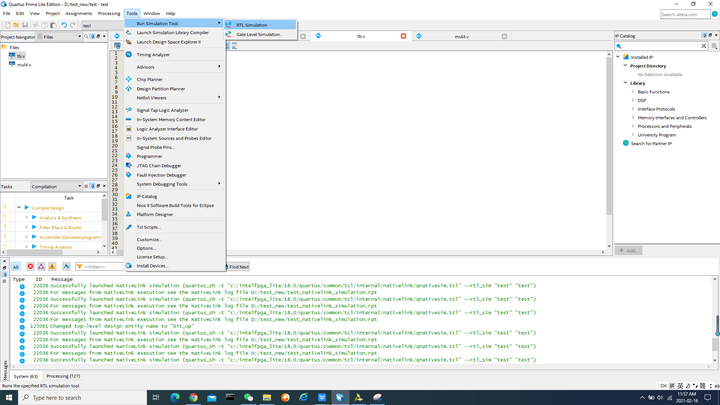

- 以上步骤设定好后,如图12,在主菜单Tools下,点击Run Simulation Tool ->RTL Simulation

图 12

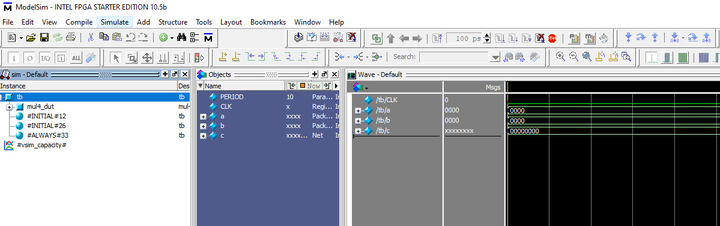

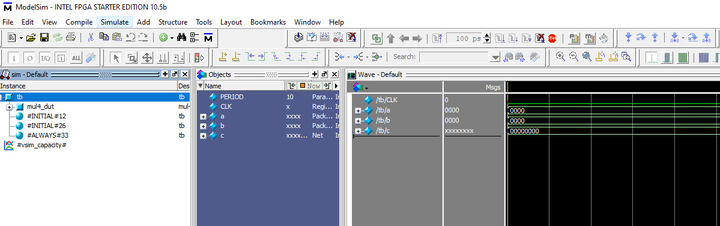

如果tb.v没有错误,打开的界面应如下图13所示,点击红框内STOP按钮,

图 13

(3)选中波形区域,如图13,点击zoom in, Zoom out, 观察仿真波形。

Module sim的详细使用,请见modelsim仿真初步。