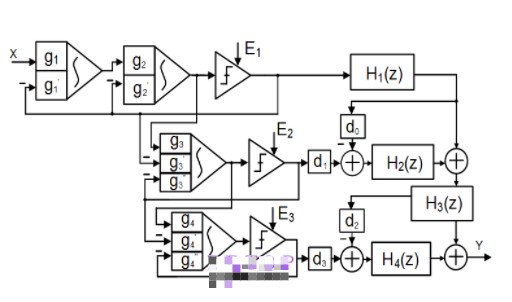

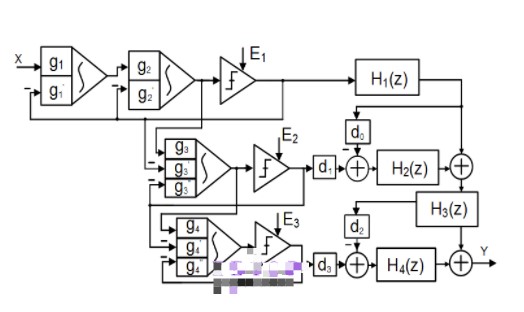

先谢过路过的各位大神!做了一个离散时间的4阶1位Sigma-delta ADC,就是传统结构:

设计时是按照采样频率80MHz设计的,前后仿均通过,但流片后测试时发现时钟频率确提不上去,只能测到20MHz采样时钟,20MHz采样频率的测试结果如下:

40MHz时就已经没有正常功能了噪底特别高:

80MHz当然就更不行了,想请问一下大家觉得这个可能是什么原因造成的,

PCB数字模拟

电源地都是分开的已经很注意了,现在就是找不到原因不知可能是

电路没做好还是PCB还有什么地方没考虑到,还望各位能不吝赐教,感谢感谢

举报

举报

举报

举报

举报

举报

举报

举报