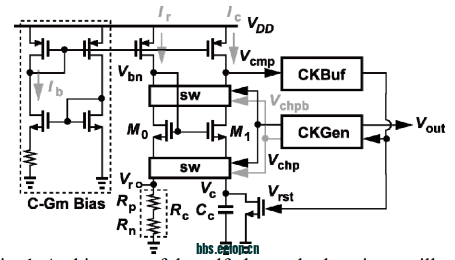

上图是论文上的截图,是我们流片的振荡器结构。

电源电压3V。

正常工作电流约100nA,频率为2kHz。现在遇到概率性漏电的问题,约有2%左右的芯片,电流变成500nA,频率变成0.2kHz。

通过实测和拟合

仿真,基本判定Vr被抬高,原来Vr小于0.2V,拟合仿真发现Vr被抬高到2.2V以上,猜测有寄生路径将电流灌入到Vr的电阻串支路中。

但是通过FIB将Vr接地,电流恢复到100nA,正常了,频率也接近仿真值。

在

layout上找寄生路径,假设了很多种可能,但还是没有找到与实验现象相符的寄生路径。

想请教大家对这种概率性漏电的路径有什么好的想法或建议,谢谢。

举报

举报

举报

举报

举报

举报