选用TMS320DM642作为系统CPU,并采用最新视频编码标准H.264压缩算法,实现基于CDMA网络传输的无线视频监控和视频数据存储系统。

文中详细地描述了系统组成、结构和功能,对系统各个组成模块进行了详细分析和设计,主要包括视音频输入、CDMA传输串口、DE及USB通信等模块,并针对DM642高速CPU,分析了系统设计中应注意的问题。

无线视频监控系统是公安、交通、水利等行业的重要装备,目前无线视频传输设备主要采用微波方式,其致命弱点是传输距离短,有障碍物时传输距离大为减少,多年来一直没有得到很好的解决。

随着运营商在国内大部分地区推出GRPS和CDMA1x公共无线数据网络,通过公共无线数据网络传输视频已成为当今研究和应用的热点,它能彻底解决微波方式的短距离问题。由于公共无线数据网络的带宽比较窄且不稳定,采用编码效率不高的视频压缩算法(如H.263、MPEG-4等),传输效果不理想,无法满足大多数监控场合的要求。

H.264是JVT制定的最新视频压缩标准,比H.263和MPEG-4在同质量时码流可低50%,同时支持无线网络传输,但其运算复杂度也是H.263和MPEG-4的3-5倍,因此一般的CPU系统无法满足要求。TMS320DM642是TI最新推出的高性能数字媒体处理器,指令最高可达4800MIPS,可以满足实时H.264编码算法的要求。本文设计了基于TMS320DM642的嵌入式系统,采用H.264视频编码算法,成功的开发了基于CDMA传输的无线视频监控系统。

1 无线视频监控系统构成

1.1 无线视频监控系统设计需求

本系统要求采用嵌入式视频发送终端,对采集视频图像进行实时压缩并通过CDMA网络发送,接收端采用PC机对接收视频数据进行解码并显示。对于嵌入式视频发送终端有如下需求:

①一路PAL/NTSC标准模拟视频输入,一路模拟音频输入;

②采用CDMA接入方式将视频数据通过网络发送;

③采用CF卡或硬盘对视频进行本地存储;

④发送图像和保存图像的尺寸和帧率等参数可调;

⑤可通过无线网络进行远程控制,并且要求低功耗。

1.2 系统的总体设计

由于CDMA无线网络带宽窄、带宽波动大,因此系统中采用H.264作为视频压缩算法。同时本地存储与CDMA发送视频在图像尺寸和帧率上不同,需要采用两个编码结构分别进行编码。

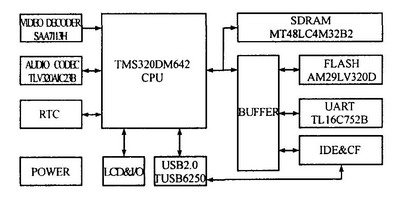

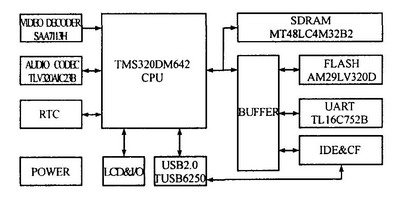

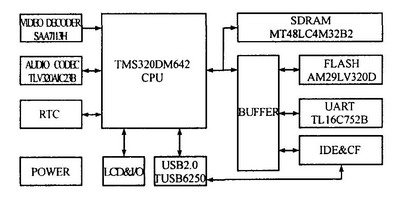

图1显示了本系统的总体结构框图,系统主要包括DM642CPU、视频输入、音频输入/输出、硬盘接口、串口和USB通信(USB2.0)等主要功能模块,此外还包括实时时钟(RTC)、显示和I/O接口(LCD&I/O)、SDRAM、FLASH和电源(POWER)模块。下面将详细地对各个功能模块进行一一分析和设计。

图1视频发送终端系统框图

2 无线视频监控系统硬件设计

2.1TMS320DM642简介

TMS320DM642是TI推出的针对多媒体处理领域应用的高性能数字媒体处理器。该处理器是专门为视频与影像市场量身定制的,特别适用于VOIP视频、视频点播(VOD)、多信道数字视频摄录像应用以及高品质视频编码与解码解决方案。

DM642处理器内部集成了TMS320C64X的DSP内核,在600MHz运行速度下,指令可达4800MIPS,由于其强大的运算能力,可以实现实时的H.264编解码算法。

DM642内部集成了外部内存接口(EMIF)控制单元,通过20根地址线和64位数据总线可直接与外部的SDRAM、FLASH进行连接。本系统中由于采用100MHz的SDRAM,考虑到信号完整性,SDRAM直接与DM642连接,而FLASH通过总线加以驱动后加以连接。

2.2 视频输入模块

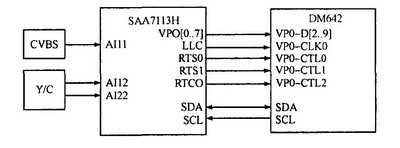

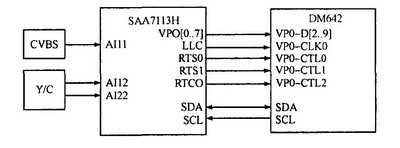

DM642具有三个视频端口,支持多种分辨率和标准,如CCIR601、ITU-BT.656、BT.1120等,每个端口为20bit位宽,可以被灵活的配置为一个20/16bit或两个10/8bit通道。同时,每个端口都可配置为视频输入或视频输出。本系统中采用VP0与SAA7113H相连进行视频输入采集。

SAA7113H为9bit视频解码器,其内部有由视频源选择、反混叠滤波器和ADC组成的两通道模拟预处理电路、增益控制、时钟发生电路(CGC)、多标准数字解码器、亮度饱和度控制电路等组成。

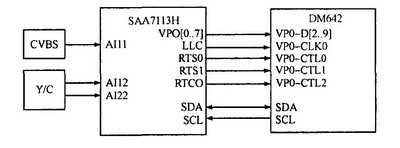

它支持PAL、NATSC等多种视频输入格式,输出支持标准的ITU.656YUV4∶2∶28bit格式,通过I2C总线进行控制,只需一个24.576MHz外部晶振,采用3.3V电源、具有小于0.5W的功耗。SAA7113H与DM642接口见图2。

图2SAA7113H与DM642接口

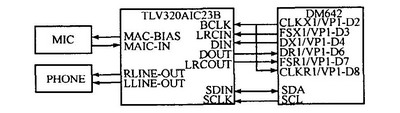

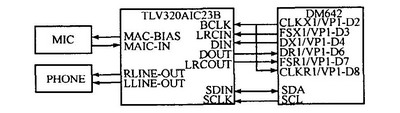

2.3 音频输入输出(CODEC)模块

DM642具有多通道音频串行端口(McASP)和两个多通道有缓存的串口(McBSPs),但它们是与视频端口复用的,本系统中采用VP1中的McBSPs1作为与音频Codec连接的接口。

TLV320AIC23B是TI推出的一款高性能的立体声音频Codec芯片,内置耳机输出放大器,支持MIC和LINEIN两种输入方式(二选一),且对输入和输出都具有可编程增益调节。

AIC23B的模数转换(ADCs)和数模转换(DACs)部件高度集成在芯片内部,采用了先进的Sigma-delta过采样技术,可以在8k到96k的频率范围内提供16bit、20bit、24bit和32bit的采样,ADC和DAC的输出信噪比分别可以达到90dB和100dB。

AIC23B还具有很低的能耗,回放模式下功率仅为23mW。

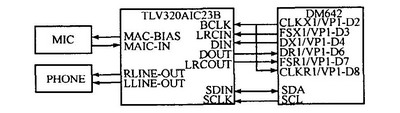

AIC23B与DM642接口见图3。

图3AIC23B与DM642接口

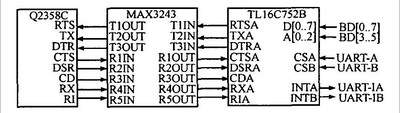

2.4 CDMA无线传输串口模块

本系统中采用Q2358C串行接口模块作为CDMA接入设备,它支持语音通信、支持中英文短信、双音多频功能(DTMF)等功能。波特率从300到115,200bit/s,支持上网最高速率153kb/s,采用AT指令集通过RS-232串口进行通信。DM642没有异步通用串行接口,需采用扩展异步通信芯片来实现串行通信。

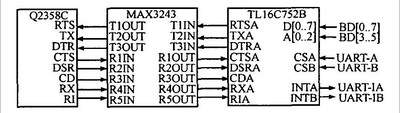

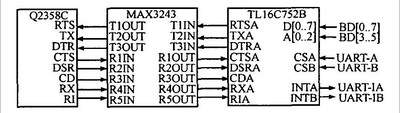

TL16C752B是UART收发器,最高波特率可以达到3Mb/s(使用48MHz时钟源时),其内部具有64byte发送/接收FIFO,接收FIFO的启动和停止可通过软件编程实现,支持多种波特率、多种串行数据格式。DM642与其连接采用EMIF控制,地址线A0~A2、数据线D0~D7、读写控制信号IOR/IOW与经过驱动的总线相连,而选通信号CSA/CSB由GAL产生。TL16C752B与Q2358C模块之间通过MAX3243进行电平转换连接。图4给出一路串行接口连接方式。

图4系统串口通信接口

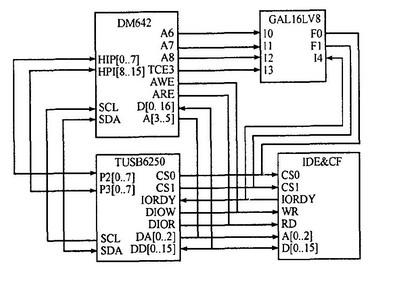

2.5 DE及USB通信模块

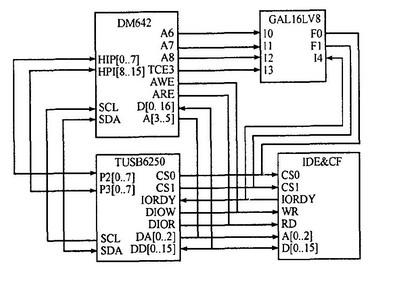

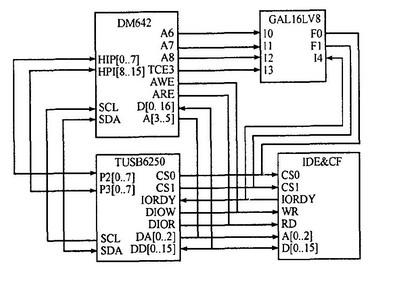

本系统中对采集视频要进行本地数据存储,采用CF卡或IDE硬盘来保存数据,在通过USB2.0将保存于CF卡或DE硬盘中的数据在需要时读出。DM642与DE接口通过GAL16LV8产生的信号进行控制。

TUSB6250采用内嵌8051内核的USB2.0到ATA/ATAPI桥接器,其完全兼容USB2.0标准,支持八个可配置终端(四路输入和四路输出)。内部集成USB存储设备传输协议,与ATA/ATAPI设备无缝连接。

内部集成的60MHz8051微处理器指令速度可达30MIPS,40kbyteRAM可灵活的配置为数据或代码RAM,13个通用I/O口能进行各种通信和控制使用,并有I2C接口。在本系统中通过I2C和HPI总线实现DSP和TUSB6250之间的通信。DE及USB部分接口见图5。

图5DM642与IDE及USB部分接口

2.6 电源及其它模块

DM642采用双电源供电,内核电源采用为1.4V消耗电流为890mA;I/O电源采用3.3V消耗电流为210mA。由于内核电源电压低同时消耗电流较大,如果采用LDO电源效率较低,消耗功率将加大,所以在本系统中采用两个开关电源芯片TPS54310分别产生3.3V和1.4V电源,电源效率可达90%以上。

DM642提供了16个通用I/O,通过这些I/O实现键盘输入、控制开关量输入与输出。DM642的视频端口VP3配置为输出直接与LCD连接。另外,系统中采用DS1338作为实时时钟,提供实时时间信息。

3 系统设计中的注意事项

3.1 原理图设计

DM642内部运行频率是通过外部时钟输入经内部PLL倍频后得到,PLL倍频可通过CLKMODE1和CLKMODE2管脚来选择x1、x6或x12,因此这两个管脚外部一定要接相应的电阻可调,以便DM642可在不同速度下运行。

DM642有多种BOOT启动模式可选,如果选择EMIFA的FLASH作为启动时,FLASH的片选必须接到TCE1上。DM642可选字节顺序的大/小模式、外设的PCI、HPI、EMAC模式的选择是通过复位时LENDIAN、PCI_EN、PCI_EEAI、HD5、MAC_EN管脚的电平决定,一定要考虑其在复位时电平值做成可调的。

对于仿真器的EMU[1∶0]保证已经上拉,TRST下拉。另外,在AARDY管脚不使用时要保证其为高电平,NMI管脚不使用时要接地,在选择HPI模式时要保证HPI控制信号电平正确,同时对其他不使用的输入管脚进行正确处理。

3.2 PCB设计

DM642作为高性能数字媒体处理器不仅内部具有很高的运行频率600MHz、720MHz和1GHz,而且与外部的SDRAM的总线速度也达到100MHz或133MHz,如果外部的SDRAM由于布线原因达不到设计的希望速度,会降低系统的性能。

对于100MHz以上的信号总线,存在信号完整性问题。要保证信号的完整采用如下方法,对于SDRAM的时钟线尽量要短,到两个SDRAM的长度尽量相等;FLASH等其他外设不要直接与数据和地址总线连接,而应通过缓冲芯片(如SN74LVT16245B)连接;高速总线上要串入小阻值电阻,阻值大小可通过仿真得到,同时对线路更加要求进行阻抗限制。

DM642内部有PLL,对于PLL外部所接器件要尽可能靠近芯片,而且必须放在线路板的一面上。对于JTAG的连线长度不能超过6in,如果超过6in长要加驱动。本系统中既有模拟部分又有数字部分,要注意模拟电源和数字电源的设计,尽量减少数字信号对模拟信号的干扰,否则对采集的视频信号会有雪花、条纹,音频信号产生噪音等。对视频、音频芯片尽量采用单独的电源芯片供电,模拟地和数字地要单点或采用磁珠相连。

4 结束语

依据以上硬件设计完成基于DM642的嵌入式无线视频监控系统,该系统以高速DSP为核心,辅以相应的外围电路,实现实时H.264视频编解码。目前,该系统已经顺利通过调试,连续运行稳定,为公安、交通、水利等行业的无线视频监控提供切实可行的方案,具有非常高的应用价值。

选用TMS320DM642作为系统CPU,并采用最新视频编码标准H.264压缩算法,实现基于CDMA网络传输的无线视频监控和视频数据存储系统。

文中详细地描述了系统组成、结构和功能,对系统各个组成模块进行了详细分析和设计,主要包括视音频输入、CDMA传输串口、DE及USB通信等模块,并针对DM642高速CPU,分析了系统设计中应注意的问题。

无线视频监控系统是公安、交通、水利等行业的重要装备,目前无线视频传输设备主要采用微波方式,其致命弱点是传输距离短,有障碍物时传输距离大为减少,多年来一直没有得到很好的解决。

随着运营商在国内大部分地区推出GRPS和CDMA1x公共无线数据网络,通过公共无线数据网络传输视频已成为当今研究和应用的热点,它能彻底解决微波方式的短距离问题。由于公共无线数据网络的带宽比较窄且不稳定,采用编码效率不高的视频压缩算法(如H.263、MPEG-4等),传输效果不理想,无法满足大多数监控场合的要求。

H.264是JVT制定的最新视频压缩标准,比H.263和MPEG-4在同质量时码流可低50%,同时支持无线网络传输,但其运算复杂度也是H.263和MPEG-4的3-5倍,因此一般的CPU系统无法满足要求。TMS320DM642是TI最新推出的高性能数字媒体处理器,指令最高可达4800MIPS,可以满足实时H.264编码算法的要求。本文设计了基于TMS320DM642的嵌入式系统,采用H.264视频编码算法,成功的开发了基于CDMA传输的无线视频监控系统。

1 无线视频监控系统构成

1.1 无线视频监控系统设计需求

本系统要求采用嵌入式视频发送终端,对采集视频图像进行实时压缩并通过CDMA网络发送,接收端采用PC机对接收视频数据进行解码并显示。对于嵌入式视频发送终端有如下需求:

①一路PAL/NTSC标准模拟视频输入,一路模拟音频输入;

②采用CDMA接入方式将视频数据通过网络发送;

③采用CF卡或硬盘对视频进行本地存储;

④发送图像和保存图像的尺寸和帧率等参数可调;

⑤可通过无线网络进行远程控制,并且要求低功耗。

1.2 系统的总体设计

由于CDMA无线网络带宽窄、带宽波动大,因此系统中采用H.264作为视频压缩算法。同时本地存储与CDMA发送视频在图像尺寸和帧率上不同,需要采用两个编码结构分别进行编码。

图1显示了本系统的总体结构框图,系统主要包括DM642CPU、视频输入、音频输入/输出、硬盘接口、串口和USB通信(USB2.0)等主要功能模块,此外还包括实时时钟(RTC)、显示和I/O接口(LCD&I/O)、SDRAM、FLASH和电源(POWER)模块。下面将详细地对各个功能模块进行一一分析和设计。

图1视频发送终端系统框图

2 无线视频监控系统硬件设计

2.1TMS320DM642简介

TMS320DM642是TI推出的针对多媒体处理领域应用的高性能数字媒体处理器。该处理器是专门为视频与影像市场量身定制的,特别适用于VOIP视频、视频点播(VOD)、多信道数字视频摄录像应用以及高品质视频编码与解码解决方案。

DM642处理器内部集成了TMS320C64X的DSP内核,在600MHz运行速度下,指令可达4800MIPS,由于其强大的运算能力,可以实现实时的H.264编解码算法。

DM642内部集成了外部内存接口(EMIF)控制单元,通过20根地址线和64位数据总线可直接与外部的SDRAM、FLASH进行连接。本系统中由于采用100MHz的SDRAM,考虑到信号完整性,SDRAM直接与DM642连接,而FLASH通过总线加以驱动后加以连接。

2.2 视频输入模块

DM642具有三个视频端口,支持多种分辨率和标准,如CCIR601、ITU-BT.656、BT.1120等,每个端口为20bit位宽,可以被灵活的配置为一个20/16bit或两个10/8bit通道。同时,每个端口都可配置为视频输入或视频输出。本系统中采用VP0与SAA7113H相连进行视频输入采集。

SAA7113H为9bit视频解码器,其内部有由视频源选择、反混叠滤波器和ADC组成的两通道模拟预处理电路、增益控制、时钟发生电路(CGC)、多标准数字解码器、亮度饱和度控制电路等组成。

它支持PAL、NATSC等多种视频输入格式,输出支持标准的ITU.656YUV4∶2∶28bit格式,通过I2C总线进行控制,只需一个24.576MHz外部晶振,采用3.3V电源、具有小于0.5W的功耗。SAA7113H与DM642接口见图2。

图2SAA7113H与DM642接口

2.3 音频输入输出(CODEC)模块

DM642具有多通道音频串行端口(McASP)和两个多通道有缓存的串口(McBSPs),但它们是与视频端口复用的,本系统中采用VP1中的McBSPs1作为与音频Codec连接的接口。

TLV320AIC23B是TI推出的一款高性能的立体声音频Codec芯片,内置耳机输出放大器,支持MIC和LINEIN两种输入方式(二选一),且对输入和输出都具有可编程增益调节。

AIC23B的模数转换(ADCs)和数模转换(DACs)部件高度集成在芯片内部,采用了先进的Sigma-delta过采样技术,可以在8k到96k的频率范围内提供16bit、20bit、24bit和32bit的采样,ADC和DAC的输出信噪比分别可以达到90dB和100dB。

AIC23B还具有很低的能耗,回放模式下功率仅为23mW。

AIC23B与DM642接口见图3。

图3AIC23B与DM642接口

2.4 CDMA无线传输串口模块

本系统中采用Q2358C串行接口模块作为CDMA接入设备,它支持语音通信、支持中英文短信、双音多频功能(DTMF)等功能。波特率从300到115,200bit/s,支持上网最高速率153kb/s,采用AT指令集通过RS-232串口进行通信。DM642没有异步通用串行接口,需采用扩展异步通信芯片来实现串行通信。

TL16C752B是UART收发器,最高波特率可以达到3Mb/s(使用48MHz时钟源时),其内部具有64byte发送/接收FIFO,接收FIFO的启动和停止可通过软件编程实现,支持多种波特率、多种串行数据格式。DM642与其连接采用EMIF控制,地址线A0~A2、数据线D0~D7、读写控制信号IOR/IOW与经过驱动的总线相连,而选通信号CSA/CSB由GAL产生。TL16C752B与Q2358C模块之间通过MAX3243进行电平转换连接。图4给出一路串行接口连接方式。

图4系统串口通信接口

2.5 DE及USB通信模块

本系统中对采集视频要进行本地数据存储,采用CF卡或IDE硬盘来保存数据,在通过USB2.0将保存于CF卡或DE硬盘中的数据在需要时读出。DM642与DE接口通过GAL16LV8产生的信号进行控制。

TUSB6250采用内嵌8051内核的USB2.0到ATA/ATAPI桥接器,其完全兼容USB2.0标准,支持八个可配置终端(四路输入和四路输出)。内部集成USB存储设备传输协议,与ATA/ATAPI设备无缝连接。

内部集成的60MHz8051微处理器指令速度可达30MIPS,40kbyteRAM可灵活的配置为数据或代码RAM,13个通用I/O口能进行各种通信和控制使用,并有I2C接口。在本系统中通过I2C和HPI总线实现DSP和TUSB6250之间的通信。DE及USB部分接口见图5。

图5DM642与IDE及USB部分接口

2.6 电源及其它模块

DM642采用双电源供电,内核电源采用为1.4V消耗电流为890mA;I/O电源采用3.3V消耗电流为210mA。由于内核电源电压低同时消耗电流较大,如果采用LDO电源效率较低,消耗功率将加大,所以在本系统中采用两个开关电源芯片TPS54310分别产生3.3V和1.4V电源,电源效率可达90%以上。

DM642提供了16个通用I/O,通过这些I/O实现键盘输入、控制开关量输入与输出。DM642的视频端口VP3配置为输出直接与LCD连接。另外,系统中采用DS1338作为实时时钟,提供实时时间信息。

3 系统设计中的注意事项

3.1 原理图设计

DM642内部运行频率是通过外部时钟输入经内部PLL倍频后得到,PLL倍频可通过CLKMODE1和CLKMODE2管脚来选择x1、x6或x12,因此这两个管脚外部一定要接相应的电阻可调,以便DM642可在不同速度下运行。

DM642有多种BOOT启动模式可选,如果选择EMIFA的FLASH作为启动时,FLASH的片选必须接到TCE1上。DM642可选字节顺序的大/小模式、外设的PCI、HPI、EMAC模式的选择是通过复位时LENDIAN、PCI_EN、PCI_EEAI、HD5、MAC_EN管脚的电平决定,一定要考虑其在复位时电平值做成可调的。

对于仿真器的EMU[1∶0]保证已经上拉,TRST下拉。另外,在AARDY管脚不使用时要保证其为高电平,NMI管脚不使用时要接地,在选择HPI模式时要保证HPI控制信号电平正确,同时对其他不使用的输入管脚进行正确处理。

3.2 PCB设计

DM642作为高性能数字媒体处理器不仅内部具有很高的运行频率600MHz、720MHz和1GHz,而且与外部的SDRAM的总线速度也达到100MHz或133MHz,如果外部的SDRAM由于布线原因达不到设计的希望速度,会降低系统的性能。

对于100MHz以上的信号总线,存在信号完整性问题。要保证信号的完整采用如下方法,对于SDRAM的时钟线尽量要短,到两个SDRAM的长度尽量相等;FLASH等其他外设不要直接与数据和地址总线连接,而应通过缓冲芯片(如SN74LVT16245B)连接;高速总线上要串入小阻值电阻,阻值大小可通过仿真得到,同时对线路更加要求进行阻抗限制。

DM642内部有PLL,对于PLL外部所接器件要尽可能靠近芯片,而且必须放在线路板的一面上。对于JTAG的连线长度不能超过6in,如果超过6in长要加驱动。本系统中既有模拟部分又有数字部分,要注意模拟电源和数字电源的设计,尽量减少数字信号对模拟信号的干扰,否则对采集的视频信号会有雪花、条纹,音频信号产生噪音等。对视频、音频芯片尽量采用单独的电源芯片供电,模拟地和数字地要单点或采用磁珠相连。

4 结束语

依据以上硬件设计完成基于DM642的嵌入式无线视频监控系统,该系统以高速DSP为核心,辅以相应的外围电路,实现实时H.264视频编解码。目前,该系统已经顺利通过调试,连续运行稳定,为公安、交通、水利等行业的无线视频监控提供切实可行的方案,具有非常高的应用价值。

举报

举报

举报

举报