就技术层面而言,LCD TV是属于高整合电子产品。它涵盖了算法、软件、硬件、芯片、无线射频等领域,而且有许多专利是属于国外公司或机构所拥有。目前国内很缺乏熟悉这块领域的系统整合人才。目前即使在先进国家,由于LCD TV或HDTV仍然属于最新的产品,熟悉这块领域的技术人才,其实也不多。与之相近的,应该是数位机顶盒(Digital STB),不过,前者的技术复杂度又远远超过后者,因为LCD TV或HDTV除了包含了网络通信的功能以外,还包括OSD(On Screen Display)和“缩放控制器(Scalar)”、屏幕驱动等功能。所以,即使设计过STB的人,也不敢随便说LCD TV或HDTV的技术很简单。

LCD TV的硬件架构

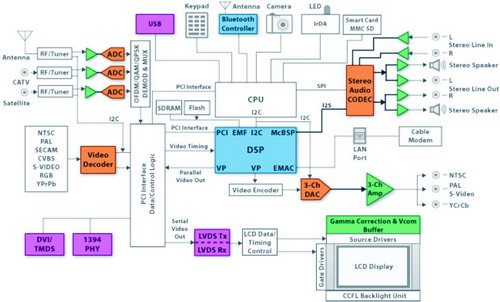

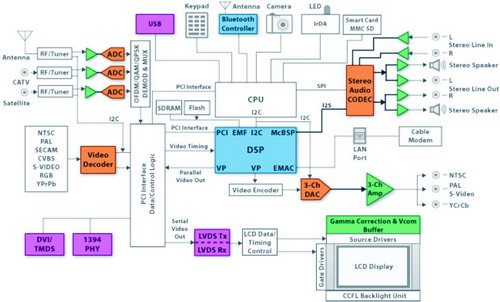

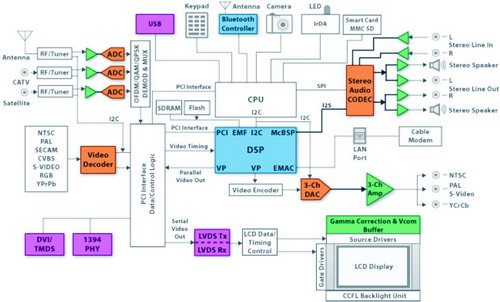

图1 LCD TV的硬件架构

图1是LCD TV的硬件架构示意图。其中,比较重要的音视频部件有:中央处理器、视频解码器(Video Decoder)、射频调谐器(RF tuner)、信道解调器(Channel Demodulator/Decoder)、音频编解码器(Audio Codec)。此外,还可能包含一般常见的I/O接口与装置,例如:USB、1394、蓝牙、WLAN、IrDA、MMC/SD/CF、以太网络、数字相机、DSL或缆线调制解调器(Cable Modem)、PDA等。

视频解码器

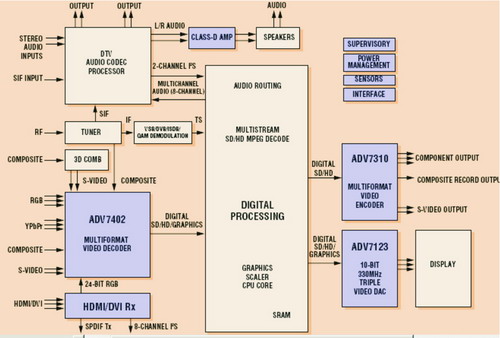

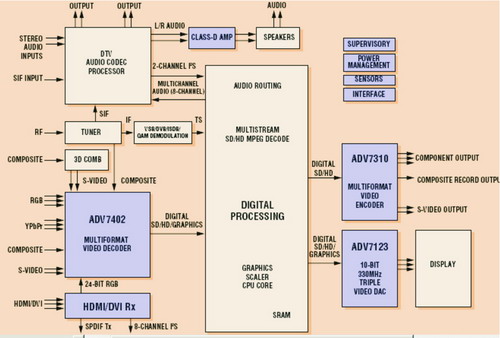

图2 混频解码器的位置

图2是一个LCD TV/HDTV视频解码器与相邻芯片之间的关系。它具有下列的主要功能:

1. 可编程化的像素(Pixel)输出端口:由8到30位来决定像素的YCbCr/RGB的比例,例如:4:2:2或4:4:4。

2. 支持外部的射频调谐器,具有10-bit的数字基频合成(Composite)视频输入单元。

3. 自动辨识和处理VCR或数字电视信号。

4. 通过像素输出端口支持“垂直空白间隔(Vertical Blank Interval;VBI)”数据的输出,可以用来传送“字幕(Closed Caption;CC)”数据,例如:传输实时的股市行情。其它VBI数据可以通过I2C接口传输,例如:版权产生管理系统(Copy Generation Management System;CGMS)、宽屏幕信号(Wide Screen Signalling)、强清晰度电视(Enhanced Definition Television;EDTV)、CC字幕、延伸数据服务(Extended Data Service;XDS)。

5. 支持全球现有的多种色彩格式:

*PAL B/D/I/G/H、PAL60、PAL M、PAL N、PAL Nc

*NTSC M/J、NTSC 4.43

*SECAM B/D/G/K/L

*NTSC方形像素(square pixel)

6. 支持HDTV的所有输入信号,例如:525p、625p、720p和1080i,以及其它高分辨率(HD)和SMPTE(Society of Motion Picture Engineers)标准。也支持标准分辨率(SD)。

7. 除支持CVBS、S-Video、YPbPr、RGB以外,还支持5线的YPbPrHV/RGBHV和CSync,如图3。

图3 支持多种视频输入格式

视频串流的路径

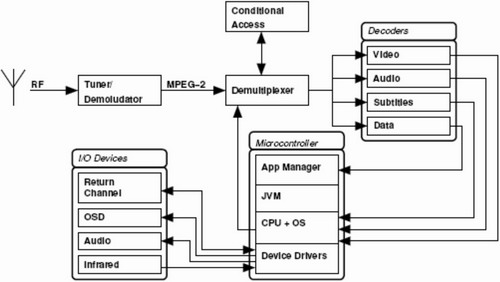

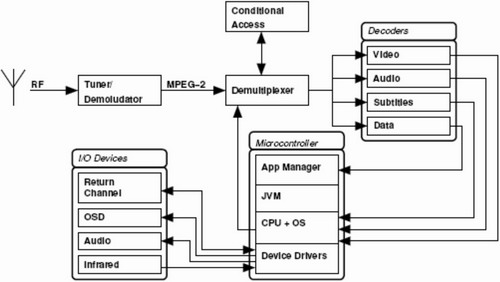

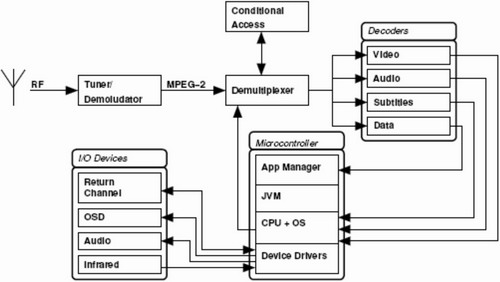

附图四是一个简易的LCD TV或数字电视接收系统之架构。它包含了上述的硬件架构,也包括了必需的软件。

图4 简易的LCD TV系统架构

从解码器、解调器传来的MPEG-2传输串流(transport stream;TS),经过”解多复用器(Demultiplexer)”之后,可以得到视频、音频、数据、对白(subtitle)或字幕…。。等不同的信号,再经过视频解码器(例如:MPEG-2/4或H.264)、音频解码器,得到的数据是最原始的(raw)数据。这些数据会被中央处理器送到适当的通信协议层,例如:V4L2、RTP/RTCP/RTSP、HTTP、Java应用程序……等,之后通过“回传信道(return channel)”,例如:以太网络,将这些数据送到因特网上;或送至OSD、音频DAC,交给LCD和扬声器播放。

没错,数字机顶盒也具有上述的类似功能。它和LCD TV一样也都具有“条件访问(CA)”的功能。只不过,LCD TV的屏幕都是内建的,而且,一般的数字机顶盒只能通过单一的路径来获取视频,但是,LCD TV可以通过4种不同的路径来取得视频,这包含:卫星数字、数字地面、因特网、有线数据网络。不过,就交互式电视的软件而言,数字机顶盒和LCD TV的软件是非常类似的,甚至是一样的。

在“设备驱动程序(device driver)”层,为了能播放数字电视信号,LCD TV的I/O端口必须要有LCD驱动程序(能够设定OSD和Scalar)和音频驱动程序。为了能将互动信息传送至因特网上,它也需要以太驱动程序和DSL(或缆线)调制解调器驱动程序。外部装置也可以通过IrDA或I2C、SPI、UART……等接口,将数据送给LCD TV处理。此外,接收端的视频/音频解码器的驱动程序也位于这一层。

有许多工程师不了解LCD TV或数字机顶盒的视频数据流(data flow)的行动路径,因此经常造成消错上的困扰,尤其是在经过视频解码器之后,信号应交给中央处理器处理,而不是其它组件。同理,如果在附图四中的信号来源换成是以太网络,而不是射频天线,在经过视频解码器解码之后的信号仍应交给中央处理器。此外,在图四中,不管是MPEG-2 TS或PS/PES,都可以将它们视为最底层的数字数据封包,其地位和角色皆如同以太封包一样,有别于模拟信号。

解码引擎

由于视频、音频格式的多样化,使用单一的解码器已经无法满足这么多的需求。于是有所谓的“解码引擎(decode engine)”,它可能是一颗RISC或DSP,负责重置、停止、加载和启动固件或“微码(microcode)”,并处理所有与串流解码无关的工作,例如:输出声音。

每个解码引擎内部具有数个解码器,负责下列的工作:1. 开启或关闭单一串流。2. 传送命令。例如:初始化、解除初始化、播放、暂停、停止等。3. 取得目前的状态信息。例如:播放中、已暂停等。4. 各种串流独有的特性。例如:数据格式等。

在这些RISC或DSP内部都具有许多个硬件模块,而每一个模块都具有特定的实体功能;这些功能通常可以利用缓存器(Register)来设定。一般而言,这些RISC或DSP会包含下列的硬件模块:1. 解多任务(Demux)引擎:同时对视频和音频分工。2. MPEG引擎:是一个视频DSP,内含一个视频解码器和一个“子图像(Subpicture)解码器”。3. 音频引擎:是一个音频DSP,内含两个音频解码器和一个混频器(mixer)。4. 中央处理器:CPU核心、DMA、中断处理单元。

这些RISC或DSP的软件模块是利用硬件模块来产生“执行绪(task)”。例如下列的软件模块:1. 系统区块:PLL初始化、DRAM设定……等。2. 图形加速引擎:使用图形加速命令所控制的FIFO,来加快处理速度。3. 字幕解码模块:软件的字幕解码单元。4. I2C:软件的I2C接口,为可程序化的输出入端口(PIO)。5. 内存管理模块:DRAM的配置。

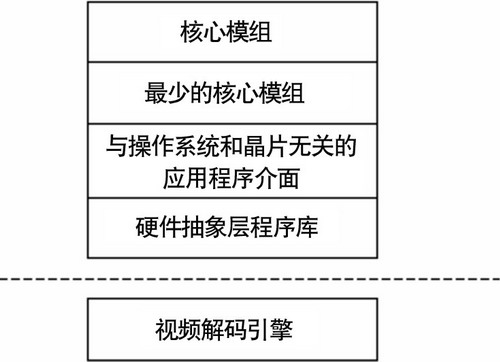

解码引擎的驱动程序

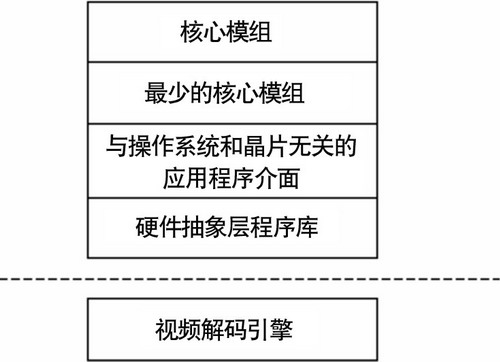

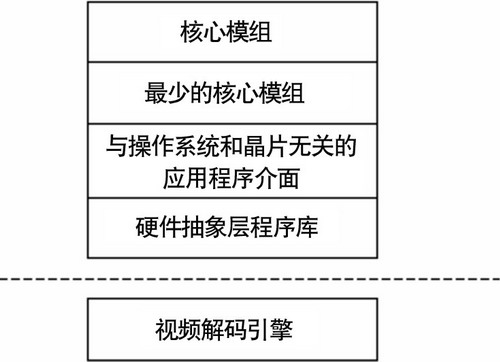

图5 视频解码引擎的驱动程序架构

通常,视频解码引擎的驱动程序会包含下列几个单元(如附图五):1. 与操作系统和芯片无关的应用程序接口(API):控制缓存器和DRAM的存取。2. 硬件抽象层链接库:与硬件相关,可通过XML语言来设定它,以适应特定的芯片。它不包含与操作系统相关的API,只会呼叫与操作系统和芯片无关的API。3. 最少的核心模块:它在上述1.的上方,负责存取缓存器和处理DMA,并且处理OS核心的全部作业,例如:IRQ处理、DMA配置…等。4. 核心模块:它呼叫“最少的核心模块”,以存取硬件。

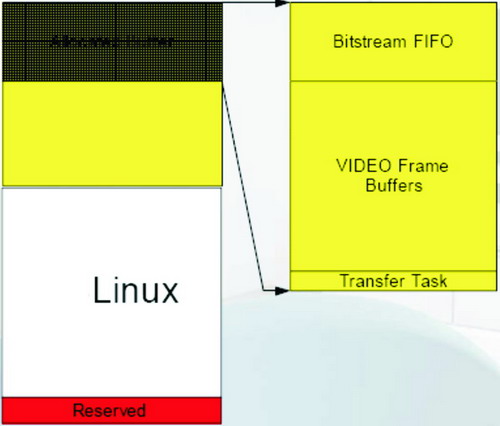

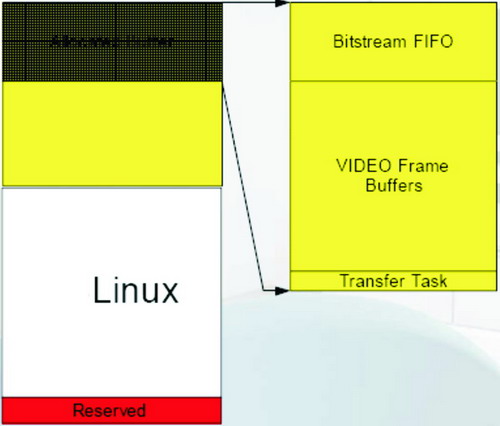

内存的配置

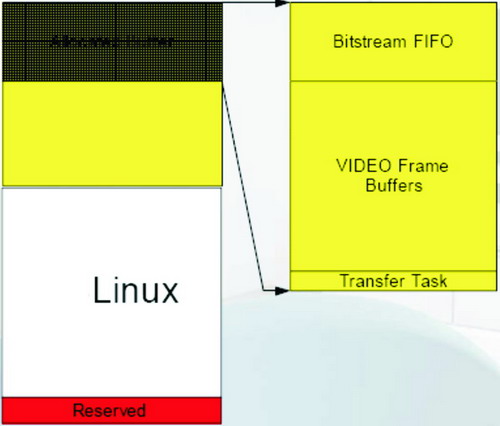

图6 视频解码器的内存配置

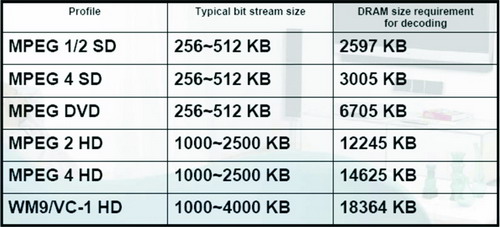

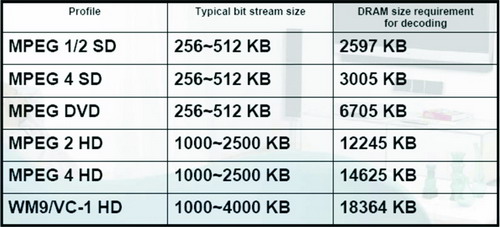

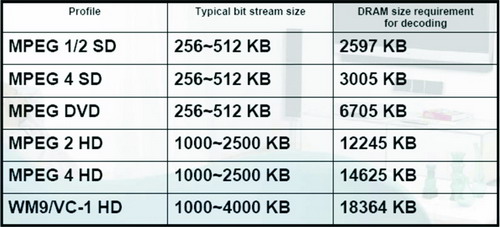

内存配置是在开发视频解码装置时,必须特别考虑的。图6是典型的视频解码器之内存配置;附表一是各种视频格式在解码时所需要的内存大小。

表1 各种视频格式的内存需求

配置内存时,必须避免分割太小和太多。务必先配置大的、长时间使用的缓冲空间(buffer);在进行多信道播放时,应避免不必要的配置或释放缓冲空间。

就技术层面而言,LCD TV是属于高整合电子产品。它涵盖了算法、软件、硬件、芯片、无线射频等领域,而且有许多专利是属于国外公司或机构所拥有。目前国内很缺乏熟悉这块领域的系统整合人才。目前即使在先进国家,由于LCD TV或HDTV仍然属于最新的产品,熟悉这块领域的技术人才,其实也不多。与之相近的,应该是数位机顶盒(Digital STB),不过,前者的技术复杂度又远远超过后者,因为LCD TV或HDTV除了包含了网络通信的功能以外,还包括OSD(On Screen Display)和“缩放控制器(Scalar)”、屏幕驱动等功能。所以,即使设计过STB的人,也不敢随便说LCD TV或HDTV的技术很简单。

LCD TV的硬件架构

图1 LCD TV的硬件架构

图1是LCD TV的硬件架构示意图。其中,比较重要的音视频部件有:中央处理器、视频解码器(Video Decoder)、射频调谐器(RF tuner)、信道解调器(Channel Demodulator/Decoder)、音频编解码器(Audio Codec)。此外,还可能包含一般常见的I/O接口与装置,例如:USB、1394、蓝牙、WLAN、IrDA、MMC/SD/CF、以太网络、数字相机、DSL或缆线调制解调器(Cable Modem)、PDA等。

视频解码器

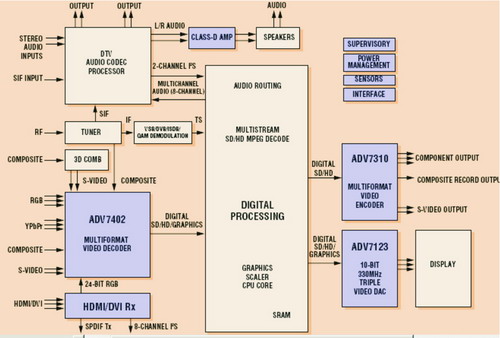

图2 混频解码器的位置

图2是一个LCD TV/HDTV视频解码器与相邻芯片之间的关系。它具有下列的主要功能:

1. 可编程化的像素(Pixel)输出端口:由8到30位来决定像素的YCbCr/RGB的比例,例如:4:2:2或4:4:4。

2. 支持外部的射频调谐器,具有10-bit的数字基频合成(Composite)视频输入单元。

3. 自动辨识和处理VCR或数字电视信号。

4. 通过像素输出端口支持“垂直空白间隔(Vertical Blank Interval;VBI)”数据的输出,可以用来传送“字幕(Closed Caption;CC)”数据,例如:传输实时的股市行情。其它VBI数据可以通过I2C接口传输,例如:版权产生管理系统(Copy Generation Management System;CGMS)、宽屏幕信号(Wide Screen Signalling)、强清晰度电视(Enhanced Definition Television;EDTV)、CC字幕、延伸数据服务(Extended Data Service;XDS)。

5. 支持全球现有的多种色彩格式:

*PAL B/D/I/G/H、PAL60、PAL M、PAL N、PAL Nc

*NTSC M/J、NTSC 4.43

*SECAM B/D/G/K/L

*NTSC方形像素(square pixel)

6. 支持HDTV的所有输入信号,例如:525p、625p、720p和1080i,以及其它高分辨率(HD)和SMPTE(Society of Motion Picture Engineers)标准。也支持标准分辨率(SD)。

7. 除支持CVBS、S-Video、YPbPr、RGB以外,还支持5线的YPbPrHV/RGBHV和CSync,如图3。

图3 支持多种视频输入格式

视频串流的路径

附图四是一个简易的LCD TV或数字电视接收系统之架构。它包含了上述的硬件架构,也包括了必需的软件。

图4 简易的LCD TV系统架构

从解码器、解调器传来的MPEG-2传输串流(transport stream;TS),经过”解多复用器(Demultiplexer)”之后,可以得到视频、音频、数据、对白(subtitle)或字幕…。。等不同的信号,再经过视频解码器(例如:MPEG-2/4或H.264)、音频解码器,得到的数据是最原始的(raw)数据。这些数据会被中央处理器送到适当的通信协议层,例如:V4L2、RTP/RTCP/RTSP、HTTP、Java应用程序……等,之后通过“回传信道(return channel)”,例如:以太网络,将这些数据送到因特网上;或送至OSD、音频DAC,交给LCD和扬声器播放。

没错,数字机顶盒也具有上述的类似功能。它和LCD TV一样也都具有“条件访问(CA)”的功能。只不过,LCD TV的屏幕都是内建的,而且,一般的数字机顶盒只能通过单一的路径来获取视频,但是,LCD TV可以通过4种不同的路径来取得视频,这包含:卫星数字、数字地面、因特网、有线数据网络。不过,就交互式电视的软件而言,数字机顶盒和LCD TV的软件是非常类似的,甚至是一样的。

在“设备驱动程序(device driver)”层,为了能播放数字电视信号,LCD TV的I/O端口必须要有LCD驱动程序(能够设定OSD和Scalar)和音频驱动程序。为了能将互动信息传送至因特网上,它也需要以太驱动程序和DSL(或缆线)调制解调器驱动程序。外部装置也可以通过IrDA或I2C、SPI、UART……等接口,将数据送给LCD TV处理。此外,接收端的视频/音频解码器的驱动程序也位于这一层。

有许多工程师不了解LCD TV或数字机顶盒的视频数据流(data flow)的行动路径,因此经常造成消错上的困扰,尤其是在经过视频解码器之后,信号应交给中央处理器处理,而不是其它组件。同理,如果在附图四中的信号来源换成是以太网络,而不是射频天线,在经过视频解码器解码之后的信号仍应交给中央处理器。此外,在图四中,不管是MPEG-2 TS或PS/PES,都可以将它们视为最底层的数字数据封包,其地位和角色皆如同以太封包一样,有别于模拟信号。

解码引擎

由于视频、音频格式的多样化,使用单一的解码器已经无法满足这么多的需求。于是有所谓的“解码引擎(decode engine)”,它可能是一颗RISC或DSP,负责重置、停止、加载和启动固件或“微码(microcode)”,并处理所有与串流解码无关的工作,例如:输出声音。

每个解码引擎内部具有数个解码器,负责下列的工作:1. 开启或关闭单一串流。2. 传送命令。例如:初始化、解除初始化、播放、暂停、停止等。3. 取得目前的状态信息。例如:播放中、已暂停等。4. 各种串流独有的特性。例如:数据格式等。

在这些RISC或DSP内部都具有许多个硬件模块,而每一个模块都具有特定的实体功能;这些功能通常可以利用缓存器(Register)来设定。一般而言,这些RISC或DSP会包含下列的硬件模块:1. 解多任务(Demux)引擎:同时对视频和音频分工。2. MPEG引擎:是一个视频DSP,内含一个视频解码器和一个“子图像(Subpicture)解码器”。3. 音频引擎:是一个音频DSP,内含两个音频解码器和一个混频器(mixer)。4. 中央处理器:CPU核心、DMA、中断处理单元。

这些RISC或DSP的软件模块是利用硬件模块来产生“执行绪(task)”。例如下列的软件模块:1. 系统区块:PLL初始化、DRAM设定……等。2. 图形加速引擎:使用图形加速命令所控制的FIFO,来加快处理速度。3. 字幕解码模块:软件的字幕解码单元。4. I2C:软件的I2C接口,为可程序化的输出入端口(PIO)。5. 内存管理模块:DRAM的配置。

解码引擎的驱动程序

图5 视频解码引擎的驱动程序架构

通常,视频解码引擎的驱动程序会包含下列几个单元(如附图五):1. 与操作系统和芯片无关的应用程序接口(API):控制缓存器和DRAM的存取。2. 硬件抽象层链接库:与硬件相关,可通过XML语言来设定它,以适应特定的芯片。它不包含与操作系统相关的API,只会呼叫与操作系统和芯片无关的API。3. 最少的核心模块:它在上述1.的上方,负责存取缓存器和处理DMA,并且处理OS核心的全部作业,例如:IRQ处理、DMA配置…等。4. 核心模块:它呼叫“最少的核心模块”,以存取硬件。

内存的配置

图6 视频解码器的内存配置

内存配置是在开发视频解码装置时,必须特别考虑的。图6是典型的视频解码器之内存配置;附表一是各种视频格式在解码时所需要的内存大小。

表1 各种视频格式的内存需求

配置内存时,必须避免分割太小和太多。务必先配置大的、长时间使用的缓冲空间(buffer);在进行多信道播放时,应避免不必要的配置或释放缓冲空间。

举报

举报

举报

举报