随着计算机技术、多媒体技术以及通信技术的发展,数字视频技术得到了越来越广泛的应用。在数字视频技术的研究中,视频数据传输是一个技术关键。本文针对视频数据流数据量大、实时性要求高的特点,采用流模式传输,将视频采集数据通过DMA从存储资源紧张的片内缓存区搬运至片外sDRAM帧缓冲区,实现图像的高速传输。

利用SoPC(System on Programmable Chip)片上可编程系统技术,将处理器、多口SDRAM控制器、DMAC、I2C接口等模块集成到一块FPGA上,实现视频图像的采集、存储、传输和显示。采用自定制组件的办法,将多口sDRAM控制器封装成符合流模式规范的一个外设挂在Avalon总线上,非常方便DMAC进行数据的搬运,并大大提高了系统的性能。

1 流模式传输规范

流模式传输是Altera Nios II嵌入式系统中的一种高级Avalon总线传输方式。这种传输模式在流模式主外设和流模式从外设之间建立一个开放的信道,以提供连续的数据传输。这个信道使得只要存在有效数据就能进行数据的流动,主设备不需要不断地对从外设的状态寄存器进行访问。这样使得主从端口之间的数据吞吐量达到最大,同时也避免了从外设的数据上溢或下溢。流传输模式最适合DMA传输。一个只包含流控制信号和一个计数器的*基金项目:深圳市科技计划资助项目(200708)。DMA控制器就可以用来在一个从外设和一个存储器之间连续地传输数据。

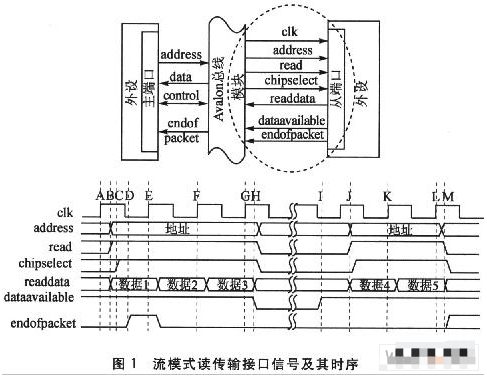

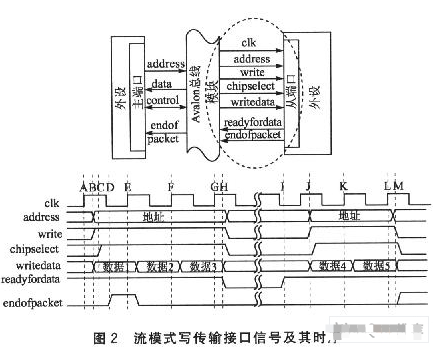

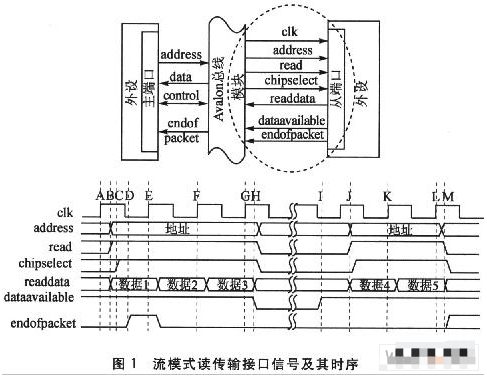

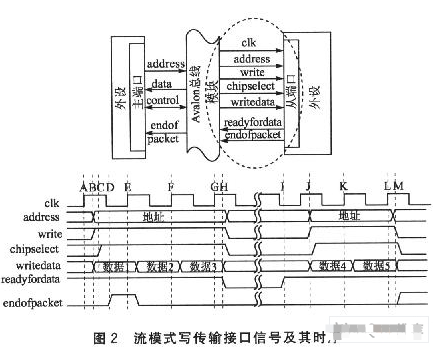

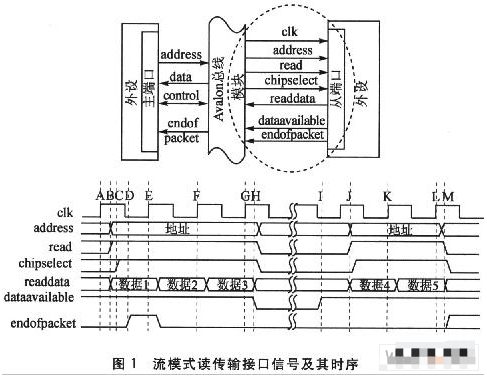

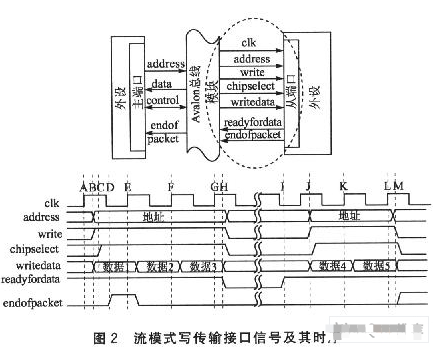

本设计采用流传输模式的从端口读传输和从端口写传输的方法。从端口读传输中,除了要设计接收主端口发出的clk信号、address信号、read信号、chipselect信号和readdata信号之外,从外设还需要设置dataavailable信号有效来表示它能够接收读传输。从端口读传输接口信号及其时序如图1所示,由从外设发出的dataavailable有效时启动流模式读传输,数据通过DMA的搬运,开始连续不断地由从外设流向主端口直至传输完成,传输的停止或中断也由从外设来决定。同样的道理,在写传输中,要设计接收主端口发出的clk信号、address信号、write信号等基本从端口写传输信号之外,从外设则需要设置ready-fordata信号有效来表示它能够接收写传输,图2为从端口写传输接口信号及其时序。此外,读传输和写传输中的endofpacket信号取决于用户设计。

2 SoPC系统结构

如图3所示,SoPC系统以32位Nios II处理器为核心,将所有的接口模块集成到一块FPGA内。其中,多口SDRAM控制器作为一个自定制外设与其他通用外设(DMA控制器、SRAM控制器、Flash接口等)一同挂在Avalon总线上,并与图像采集模块、VGA显示控制模块以及12C通信模块等一起构成SoPC视频采集系统。本设计中,片外SDRAM容量较大,作为视频数据源缓冲区以及显示缓冲区;片外SRAM速度快但资源有限,可用于视频处理缓冲区。从SDRAM(数据源)到SRAM(处理缓冲区)以及从SRAM(处理缓冲区)到SDRAM(显示缓冲区)的传输,则由DMAC采用流模式的方法来实现数据的搬运。

3 流模式接口的设计

(1)四口SDRAM控制器

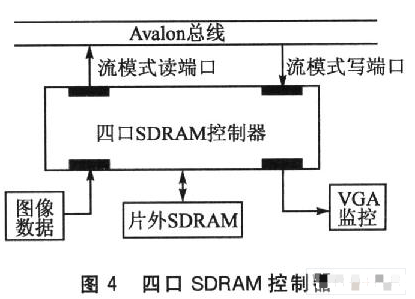

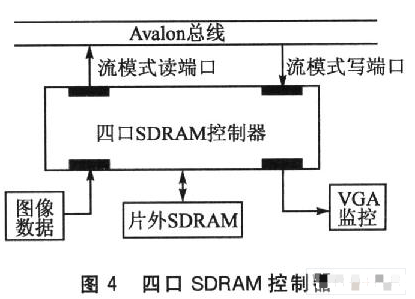

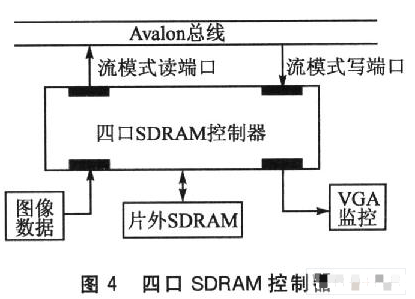

本系统采用片外SDRAM作为帧缓冲区,而对SDRAM使用的关键在于其控制接口的设计。在SoPCBuilder集成开发软件中,可直接使用系统元件库提供的单口SDRAM控制器,但是该控制器IP核无法满足采集、传输和显示同时进行的要求。因此,自定制了一个四口SDRAM控制器。如图4所示,该四口SDRAM控制器中的2个端口用于流模式的读和写,另外2个端口一个作为图像数据源输入,还有一个作为VGA显示输出。

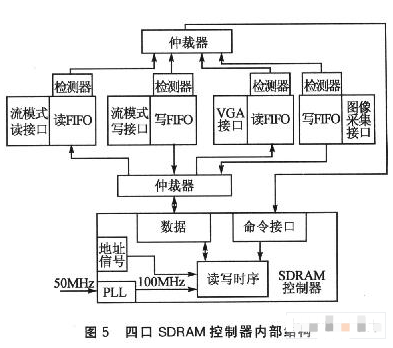

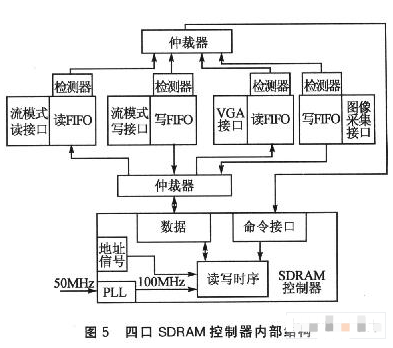

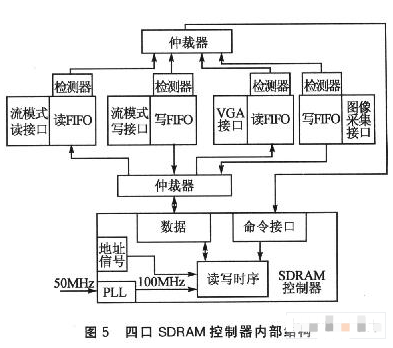

由于数据采集、VGA监控、流模式传输数据流速度与SDRAM控制器存取不匹配,因此,对于这四口中的任何一个口,都用FIFO来对数据进行缓冲,以协调数据的同步而不至于错位。而每个FIFO都有个水位检测器,当水位到半满时根据仲裁电路判断的优先级启用SDRAM读写命令,以100 MHz(系统时钟频率50 MHz)的频率根据用户给定的地址信号进行批量数据的存取,从而满足了四口并用的要求。该SDRAM控制器的内部结构如图5所示。

(2)数据流的传输

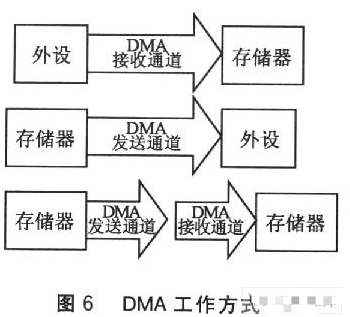

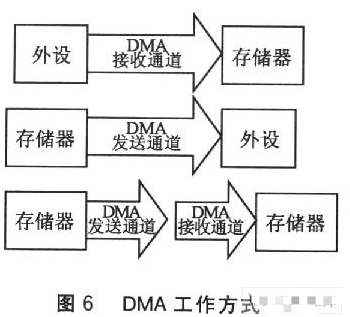

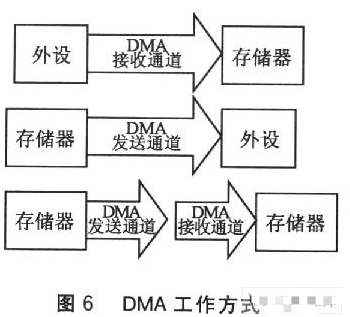

用DMA来搬运数据不仅速度非常快,而且整个操作不需要CPU的干预,可把CPU从繁重的数据传送中解放出来。DMA控制器将数据从源地址空间传输到目的地址空间,数据源或目的地可以是Avalon从外设(一个固定地址),也可以是存储器的一段地址范围。对DMA控制器的使用,需要Nios II处理器对源地址和目的地址进行初始化配置,同时也要预先给定传输长度以及传输模式等。本系统使用了Altera公司提供的HAL DMA设备驱动程序。该驱动程序把DMA传输抽象成两种数据通道:数据发送通道和数据接收通道,如图6所示。

如此,便可通过Nios II用软件控制DMA以流模式进行数据传输,具体搬运的数据路径如图7所示。其中缓冲区1是采集数据的源缓冲区。缓冲区2是传输后显示缓冲区,缓冲区3是处理缓冲区。对视频的处理不是本文讨论的范围,故这里只将原图像传回。

(3)流模式接口的硬件设计

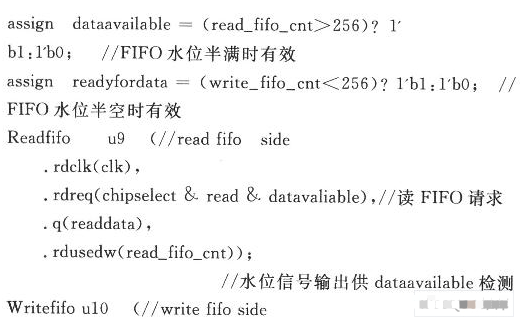

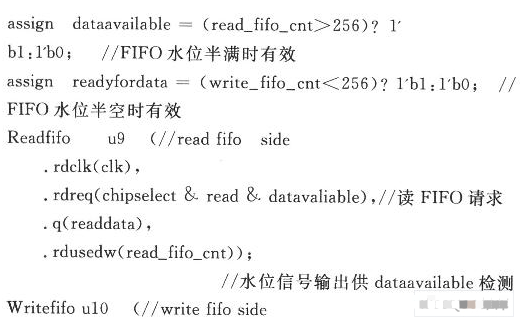

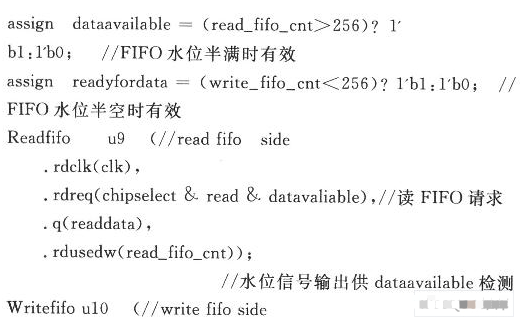

对流模式接口的硬件设计实际上就是把上述四口SDRAM控制器封装成一个Avalon自定制组件,且这个组件的其中两端口满足流模式读写规范。根据Avalon总线流模式传输规范,该自定制外设需要设置dataavailable、readyfordata信号有效表示已经准备好流模式传输,同时接收主设备发出clk、read/write、chipse-lect等信号,并根据这些信号对上述FIFO进行数据的存取。以下给出了该接口的部分Verilog HDL代码(u9、u10为FIFO的端口信号连接情况):

(4)数据路径的软件控制

作为自定义的组件,除了硬件接口以外,还需要编写驱动层软件(固件)。SoPC Builder生成的外设信息都保存在system.h文件里,固件的编写主要是基于这个文件信息。

对数据路径的控制是通过Nios II软件配置DMA控制器来实现的。这种软硬件协同设计的办法,既兼顾了传输的速度又兼顾了数据路径的灵活性。对数据传输的设置,首先需要在SoPC Builder中设定DMA控制器的read_master和write_master,也就是数据搬运的源和目的地。具体设置如图8所示。

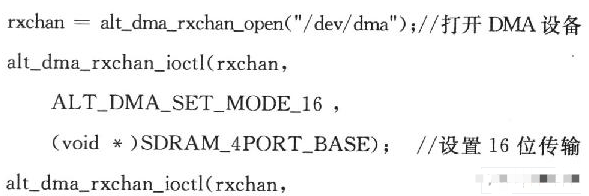

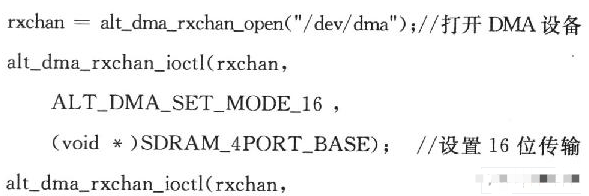

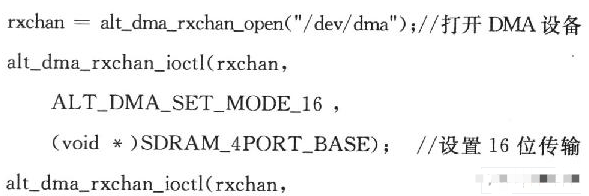

除此之外,还要在软件上具体设置DMA传输的源地址、目的地址、传输长度以及传输模式等。这里给出部分调用HAL DMA驱动的软件代码:

4 系统测试

(1)流模式接口仿真

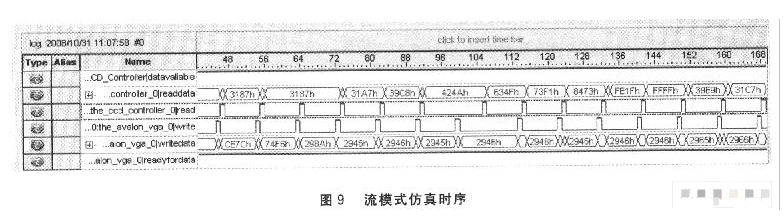

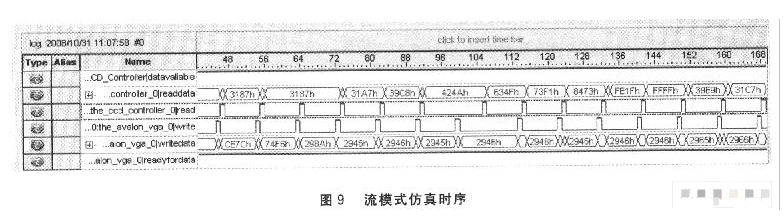

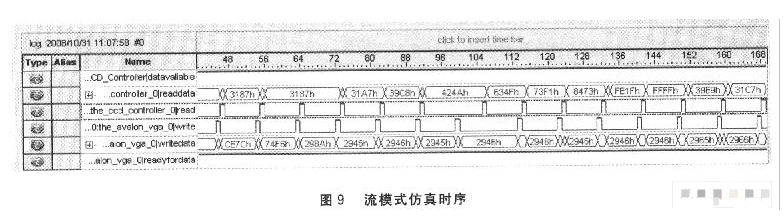

用Quartus II自带的Signaltap II逻辑分析仪对自定制的流模式接口信号进行观察,图9为相关信号波形。经过分析,此波形与流模式的传输规范吻合。

(2)系统测试

整个SOPC系统在Altera DEl的Cyclone II FPGA上实现。采用友晶科技公司的摄像头进行图像数据源输入,用VGA显示终端进行输出观察,用DEl设计平台和该SoPC视频采集系统对某一场景进行拍摄截图。结果表明,该流模式接口工作流畅。

5 总 结

本设计采用以Nios II为核心的SoPC系统实现了视频采集信号的流模式传输,并将其做成一个自定义外设,非常方便重复利用。另外,利用了DMAC硬件实现传输,且数据采集、存储和显示全硬件实现,速度非常快;同时,可以将SRAM作为图像处理缓冲区,将处理后的图像读回,这样就搭建了一个图像处理的硬件系统。当需要实现某种视频处理的算法时,只需要修改图像处理模块,再放进系统中就可以实现。

随着计算机技术、多媒体技术以及通信技术的发展,数字视频技术得到了越来越广泛的应用。在数字视频技术的研究中,视频数据传输是一个技术关键。本文针对视频数据流数据量大、实时性要求高的特点,采用流模式传输,将视频采集数据通过DMA从存储资源紧张的片内缓存区搬运至片外sDRAM帧缓冲区,实现图像的高速传输。

利用SoPC(System on Programmable Chip)片上可编程系统技术,将处理器、多口SDRAM控制器、DMAC、I2C接口等模块集成到一块FPGA上,实现视频图像的采集、存储、传输和显示。采用自定制组件的办法,将多口sDRAM控制器封装成符合流模式规范的一个外设挂在Avalon总线上,非常方便DMAC进行数据的搬运,并大大提高了系统的性能。

1 流模式传输规范

流模式传输是Altera Nios II嵌入式系统中的一种高级Avalon总线传输方式。这种传输模式在流模式主外设和流模式从外设之间建立一个开放的信道,以提供连续的数据传输。这个信道使得只要存在有效数据就能进行数据的流动,主设备不需要不断地对从外设的状态寄存器进行访问。这样使得主从端口之间的数据吞吐量达到最大,同时也避免了从外设的数据上溢或下溢。流传输模式最适合DMA传输。一个只包含流控制信号和一个计数器的*基金项目:深圳市科技计划资助项目(200708)。DMA控制器就可以用来在一个从外设和一个存储器之间连续地传输数据。

本设计采用流传输模式的从端口读传输和从端口写传输的方法。从端口读传输中,除了要设计接收主端口发出的clk信号、address信号、read信号、chipselect信号和readdata信号之外,从外设还需要设置dataavailable信号有效来表示它能够接收读传输。从端口读传输接口信号及其时序如图1所示,由从外设发出的dataavailable有效时启动流模式读传输,数据通过DMA的搬运,开始连续不断地由从外设流向主端口直至传输完成,传输的停止或中断也由从外设来决定。同样的道理,在写传输中,要设计接收主端口发出的clk信号、address信号、write信号等基本从端口写传输信号之外,从外设则需要设置ready-fordata信号有效来表示它能够接收写传输,图2为从端口写传输接口信号及其时序。此外,读传输和写传输中的endofpacket信号取决于用户设计。

2 SoPC系统结构

如图3所示,SoPC系统以32位Nios II处理器为核心,将所有的接口模块集成到一块FPGA内。其中,多口SDRAM控制器作为一个自定制外设与其他通用外设(DMA控制器、SRAM控制器、Flash接口等)一同挂在Avalon总线上,并与图像采集模块、VGA显示控制模块以及12C通信模块等一起构成SoPC视频采集系统。本设计中,片外SDRAM容量较大,作为视频数据源缓冲区以及显示缓冲区;片外SRAM速度快但资源有限,可用于视频处理缓冲区。从SDRAM(数据源)到SRAM(处理缓冲区)以及从SRAM(处理缓冲区)到SDRAM(显示缓冲区)的传输,则由DMAC采用流模式的方法来实现数据的搬运。

3 流模式接口的设计

(1)四口SDRAM控制器

本系统采用片外SDRAM作为帧缓冲区,而对SDRAM使用的关键在于其控制接口的设计。在SoPCBuilder集成开发软件中,可直接使用系统元件库提供的单口SDRAM控制器,但是该控制器IP核无法满足采集、传输和显示同时进行的要求。因此,自定制了一个四口SDRAM控制器。如图4所示,该四口SDRAM控制器中的2个端口用于流模式的读和写,另外2个端口一个作为图像数据源输入,还有一个作为VGA显示输出。

由于数据采集、VGA监控、流模式传输数据流速度与SDRAM控制器存取不匹配,因此,对于这四口中的任何一个口,都用FIFO来对数据进行缓冲,以协调数据的同步而不至于错位。而每个FIFO都有个水位检测器,当水位到半满时根据仲裁电路判断的优先级启用SDRAM读写命令,以100 MHz(系统时钟频率50 MHz)的频率根据用户给定的地址信号进行批量数据的存取,从而满足了四口并用的要求。该SDRAM控制器的内部结构如图5所示。

(2)数据流的传输

用DMA来搬运数据不仅速度非常快,而且整个操作不需要CPU的干预,可把CPU从繁重的数据传送中解放出来。DMA控制器将数据从源地址空间传输到目的地址空间,数据源或目的地可以是Avalon从外设(一个固定地址),也可以是存储器的一段地址范围。对DMA控制器的使用,需要Nios II处理器对源地址和目的地址进行初始化配置,同时也要预先给定传输长度以及传输模式等。本系统使用了Altera公司提供的HAL DMA设备驱动程序。该驱动程序把DMA传输抽象成两种数据通道:数据发送通道和数据接收通道,如图6所示。

如此,便可通过Nios II用软件控制DMA以流模式进行数据传输,具体搬运的数据路径如图7所示。其中缓冲区1是采集数据的源缓冲区。缓冲区2是传输后显示缓冲区,缓冲区3是处理缓冲区。对视频的处理不是本文讨论的范围,故这里只将原图像传回。

(3)流模式接口的硬件设计

对流模式接口的硬件设计实际上就是把上述四口SDRAM控制器封装成一个Avalon自定制组件,且这个组件的其中两端口满足流模式读写规范。根据Avalon总线流模式传输规范,该自定制外设需要设置dataavailable、readyfordata信号有效表示已经准备好流模式传输,同时接收主设备发出clk、read/write、chipse-lect等信号,并根据这些信号对上述FIFO进行数据的存取。以下给出了该接口的部分Verilog HDL代码(u9、u10为FIFO的端口信号连接情况):

(4)数据路径的软件控制

作为自定义的组件,除了硬件接口以外,还需要编写驱动层软件(固件)。SoPC Builder生成的外设信息都保存在system.h文件里,固件的编写主要是基于这个文件信息。

对数据路径的控制是通过Nios II软件配置DMA控制器来实现的。这种软硬件协同设计的办法,既兼顾了传输的速度又兼顾了数据路径的灵活性。对数据传输的设置,首先需要在SoPC Builder中设定DMA控制器的read_master和write_master,也就是数据搬运的源和目的地。具体设置如图8所示。

除此之外,还要在软件上具体设置DMA传输的源地址、目的地址、传输长度以及传输模式等。这里给出部分调用HAL DMA驱动的软件代码:

4 系统测试

(1)流模式接口仿真

用Quartus II自带的Signaltap II逻辑分析仪对自定制的流模式接口信号进行观察,图9为相关信号波形。经过分析,此波形与流模式的传输规范吻合。

(2)系统测试

整个SOPC系统在Altera DEl的Cyclone II FPGA上实现。采用友晶科技公司的摄像头进行图像数据源输入,用VGA显示终端进行输出观察,用DEl设计平台和该SoPC视频采集系统对某一场景进行拍摄截图。结果表明,该流模式接口工作流畅。

5 总 结

本设计采用以Nios II为核心的SoPC系统实现了视频采集信号的流模式传输,并将其做成一个自定义外设,非常方便重复利用。另外,利用了DMAC硬件实现传输,且数据采集、存储和显示全硬件实现,速度非常快;同时,可以将SRAM作为图像处理缓冲区,将处理后的图像读回,这样就搭建了一个图像处理的硬件系统。当需要实现某种视频处理的算法时,只需要修改图像处理模块,再放进系统中就可以实现。

举报

举报

举报

举报