CCD(电荷藕合组件)

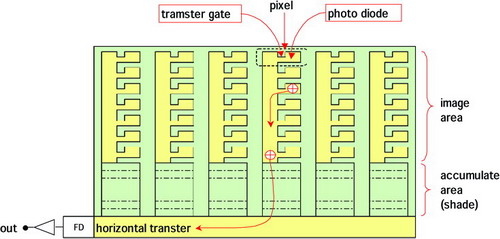

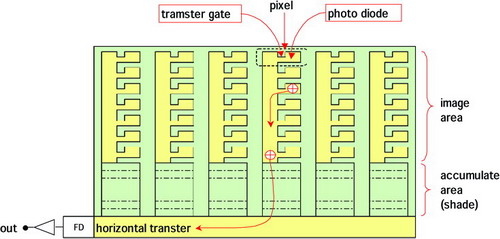

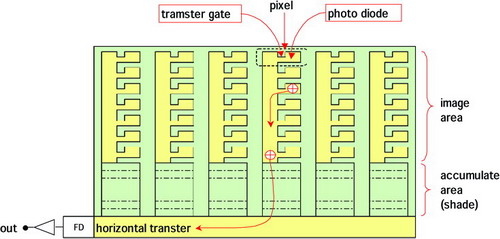

因不同种类的工作需求,业界发展出不同的类型的CCD:Line(线型),Interline(扫描), Full-Frame(全景)和Frame-Transfer(全传)。线型CCD是以一维感光点构成,通过步进马达扫描图像,由于照片是一行行组成,所以速度较二维的数码相机来得慢,这种CCD大多用在平台式扫描仪上。扫描型的CCD曝光后所产生的电荷都被转移到附近的移位寄存器,通过垂直传送向下转移到底部,按一定排序输出,它的优点在于曝光后即可将电荷储存在寄存器,继续拍照速度较快, 缺点是寄存器占用了感光面的面积, 相应地牺牲了动态范围,这种CCD成本较低,多用在监视器、拍照手机、或低档数码相机上。全景CCD是一种架构更简单的感光设计,鉴于扫描型的缺点,全景型可以利用整个感光区域(没有寄存区的设计),有效增大感光面积,同时也适应长时间曝光,其曝光过程和线型相同, 不过感光和电荷输出过程是分开的。因此全景CCD的数码相机在传送电荷时必须使用机械快门(无法使用电子快门),同时,也限制了全景CCD的连续拍照的能力。全景型大多用在专业级相机上。全传CCD的架构介于扫描和全景之间, 有时也叫全扫描型,它分成上、下部分,上半部分是感光区,下半部是暂时存储区。整体来说全传CCD非常类似全景CCD,它的特点在于直接规划一个大型寄存区。一旦全传CCD工作,它可以迅速将电荷转移到下方的寄存区中,本身可以继续曝光拍照。这种设计,让全传同扫描一样可以使用电子快门, 同时也可以增加感光面积和速度, 兼顾动态和静态的拍摄能力。大多数数码相机采用此类CCD。

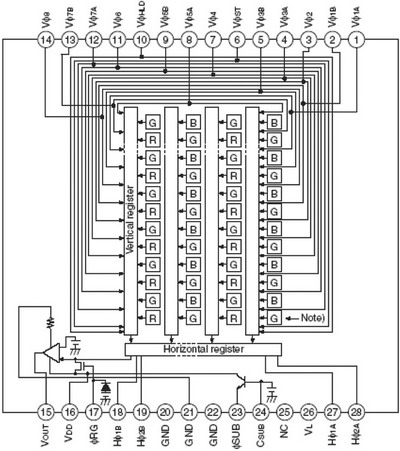

图1 全扫描CCD的内部结构

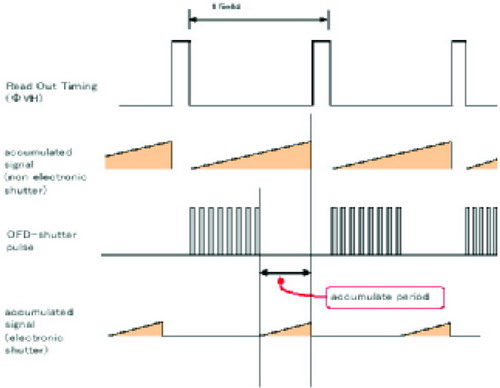

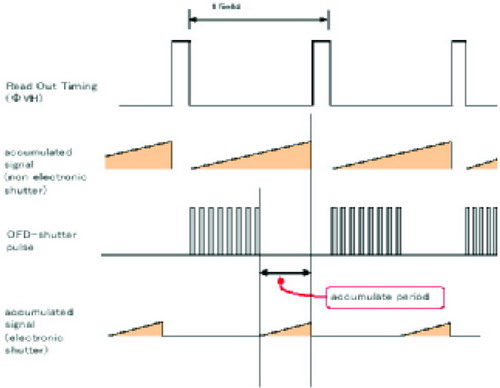

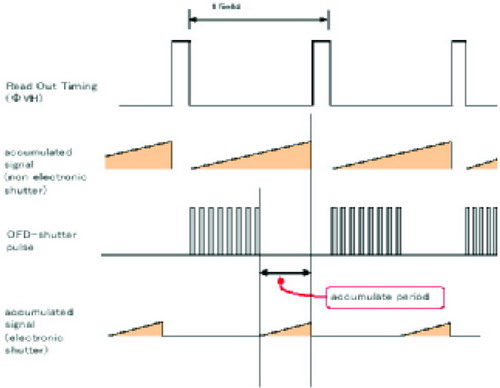

一般数码相机都带有预览(Preview)和录像(Rec)功能,在这里电子快门就起到了关键的作用。图2为电子快门控制像素的曝光过程。

图2 电子快门控制像素的曝光

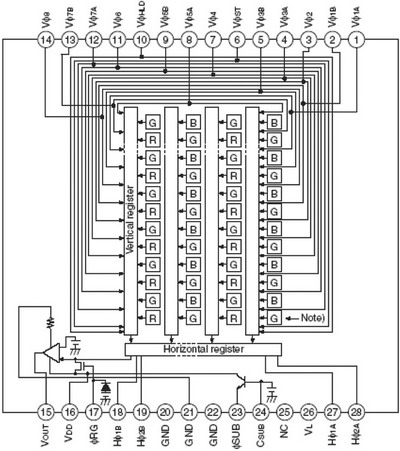

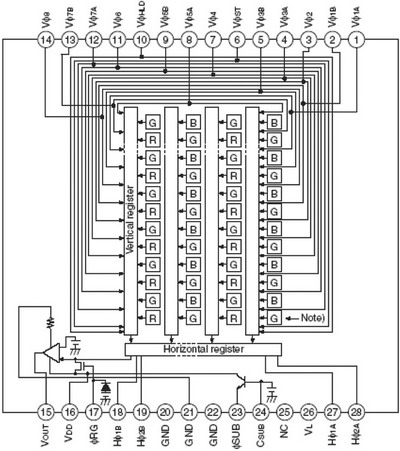

图3为CCD内部示意图,当一幅图像曝光后,就需要将感光电荷从CCD输出,为了让感光的电荷输出,电荷先到垂直寄存器,通过垂直驱动脉冲(Φ1~Φ9)将每一行的电荷转移到水平寄存器,水平寄存器在水平驱动脉冲(ΦH1,ΦH2)驱动下,往CCD OUT方向移动,在末段有一放大器,ΦRS,ΦH1,ΦH2脉冲的作用下将电荷转换为电压,从CCD OUT 输出。

图3 CCD内部等效电路图

CDS(相关两次取样)

业界所称的CDS 是由时序发生器(Timing IC)、垂直驱动器(V-driver)、模拟信号处理器(AFE IC)集成的IC。它提供CCD的工作时序、电平并将CCD输出的模拟信号进行取样、放大、模数转换,将图像数据传给DSP进行图像处理。

时序发生器有一个寄存器,通过3根串口线进行各种设定:模式设定(拍照、录像或预览),电子快门和速度,ΦRS,ΦFR,ΦFCDS,ΦFS,ΦADCK,ΦDCLK相位调整,等等。

模拟信号处理器(AFE IC)有一个寄存器,通过3根串口线进行各种设定:CCD输出信号放大倍数(GAIN),默认“全黑”时电平,等等进行设定。

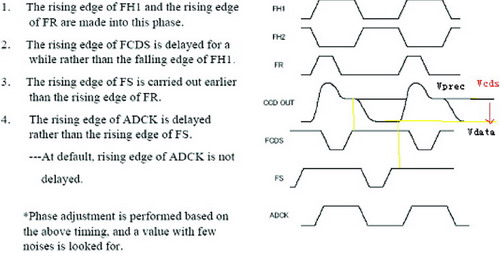

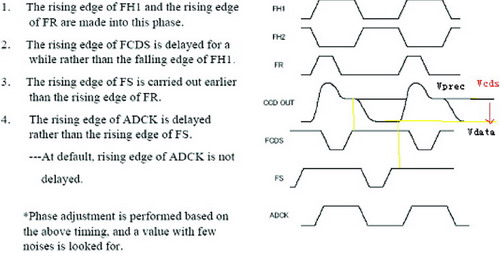

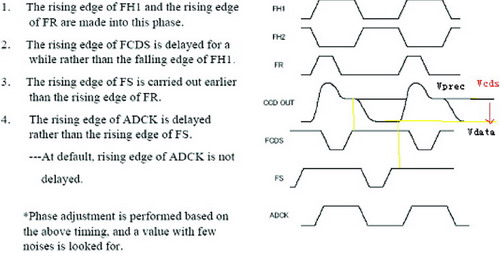

相关两次取样:在ΦRS,ΦH1,ΦH2脉冲的作用下CCD信号输出,当复位(RS)完成, 由于CCD暗电流的存在,CCD OUT不是为“0”,FCDS脉冲取样Vprec。当H2为高电平时,图像信号输出,FS脉冲取样Vdata,两者的差值就是图像信号Vcds,这就是相关两次取样,如图4所示。

图4 CCD的相关两次取样

电路设计

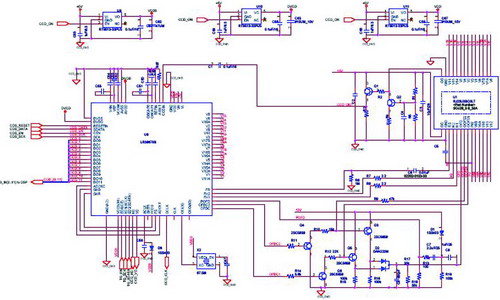

本文以某款7百万像素的数码相机设计作为说明,CCD采用SHARP公司的RJ23U3BA0FT,尺寸为1/2.5英寸,像素总数为水平3098×垂直2328,有效像素为3088×2320(共716万像素),像素单元为1.9mm×1.9mm,支持视频模式(30帧/s,15帧/s)。CDS采用SHARP公司推荐搭配此CCD的LR38678,工作电压为3.3V,TG主频67.5MHz,提供CCD的驱动频率为33.75MHz。

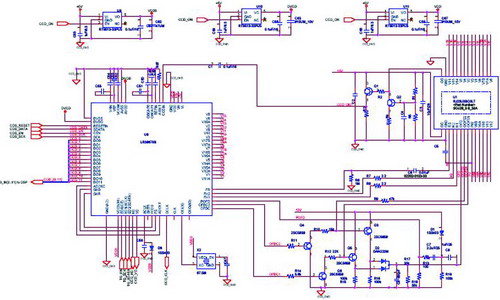

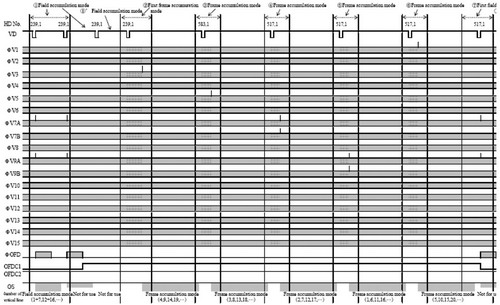

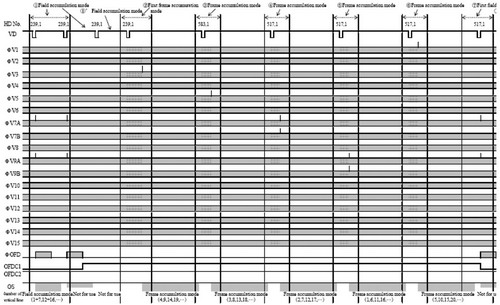

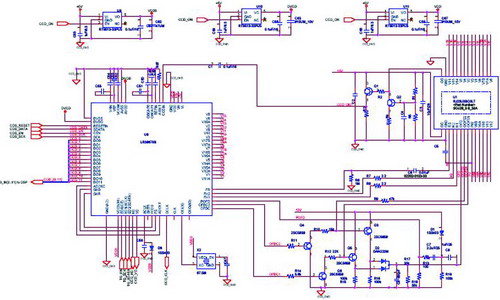

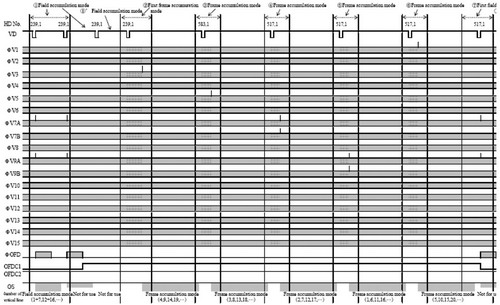

图5为电路原理图, 基本按照厂商推荐值进行设计。CDS的POFD输出电子快门信号经电平转换在CCD OFD输入。此CCD可以工作在不同的模式,见表1(A,B,C,取样的条数不同),通过串口设定OFDC,OFDC2电位来达到不同的工作模式表2(录像、监视和拍照),在录像、监视模式,图像是按一场输出,1VD一幅图像,但每幅图像只是抽取CCD部分条数。当在拍照模式,CCD上全部像素信号都要输出,一幅图像是由5帧输出,1VD对应1帧,具体时序见图6 CCD时序。CDS将CCD信号AD转换成D0~D11数字数据传输给DSP,同时伴随时钟信号,VD,HD信号。

图5 电路原理图

图6 CCD时序

相机的前端系统对电源要求很高,很容易将电源噪声反应在图像信号上,一般都选用低压稳压器(LDO),本文使用RT9013-33 LDO,具有极低的自有噪声和较高的电源抑制比,电流最大值达到500mA。CDS 3组电源中,以TG电源负载最大,工作时负载变化很大,一般选用较低ESR 47uF以上的钽电容,假如此路电源处理不当,会出现竖条纹。-7V和+13V也要求较低的纹波。

本文采用晶振电路能够满足要求

零件摆放和走线(LAYOUT),CCD前端系统是数码相机的心脏,是像的来源,在系统设计中处于优先考虑的位置。CCD和CDS按尽量靠近的原则。CCD输出的信号,工作频率达到33.75MHz,路径要短,最好在同一层,线周围不但要包地,PCB板上、下层也要铺地,避免受其它信号源的干扰和干扰其它信号源。CCD其它信号线H1,H2,RS,工作频率33.75MHz,也要同CCD输出信号一样处理。前端系统的CCD GND,同相机系统的GND要单独分开, 避免数字地的影响。相机尺寸朝小型化发展,在系统的设计中, 前端系统尽量远离其它干扰源,或预先屏蔽。

由于LAYOUT 和零件差异性,CCD前端系统需对高速信号H1,H2,RS,ACLK,DCLK,FCDS,FS相位调整,以便正常工作,获得最佳的图像信号。用示波器观察波形调整, 要注意选择合适探头测试。

调整CDS的DCLK相位,使传输DSP的时钟数据线同步。假如不能同步,DSP接收不到正确的图像信息。此CDS上没有对H1,H2相位的调整,只能通过外部电路调整串联电阻阻值。厂商对H1,H2,RS提供建议值,假如H1,H2偏离标准值,会造成图像信号传输不完整,影响图像质量。

调整RS,ACLK,DCLK,FCDS,FS相位,都是通过串口改变TG寄存器的数据。一种方法用示波器观察波形,使RS和H1在同一上升沿,FCDS的上升沿比H1的下降沿稍迟一点,RS的上升沿比FS的上升沿稍迟一点, ADCK的上升沿比FS的上升沿稍迟一点。另一种方法是固定好光圈,快门速度,Gain(增益)值,光源,改变不同的相位值对色板拍照, 用PHOTOSHOP打开照片,记录色阶分布中的“平均值”和“标准偏差”,“平均值”指的是照片的亮度,反应CCD的输出能力,数值越大,CCD的信号输出越大,“标准偏差”(描述亮度范围的单位)数值越大,杂讯越大。取“平均值”和“标准偏差”数值绘制图表曲线,取“平均值”和“标准偏差”平衡点,即较大的亮度和较小的杂讯。照片对应的相位值就是比较理想的调整值。或此两种方法相互运用,再加上实拍,求得调整值。

结语

数码相机的CCD的前端系统设计是整台相机设计的关键, 随着相机向高像素,高图像品质发展,工作频率越来越高,对元器件特性和前端系统要求更高。

CCD(电荷藕合组件)

因不同种类的工作需求,业界发展出不同的类型的CCD:Line(线型),Interline(扫描), Full-Frame(全景)和Frame-Transfer(全传)。线型CCD是以一维感光点构成,通过步进马达扫描图像,由于照片是一行行组成,所以速度较二维的数码相机来得慢,这种CCD大多用在平台式扫描仪上。扫描型的CCD曝光后所产生的电荷都被转移到附近的移位寄存器,通过垂直传送向下转移到底部,按一定排序输出,它的优点在于曝光后即可将电荷储存在寄存器,继续拍照速度较快, 缺点是寄存器占用了感光面的面积, 相应地牺牲了动态范围,这种CCD成本较低,多用在监视器、拍照手机、或低档数码相机上。全景CCD是一种架构更简单的感光设计,鉴于扫描型的缺点,全景型可以利用整个感光区域(没有寄存区的设计),有效增大感光面积,同时也适应长时间曝光,其曝光过程和线型相同, 不过感光和电荷输出过程是分开的。因此全景CCD的数码相机在传送电荷时必须使用机械快门(无法使用电子快门),同时,也限制了全景CCD的连续拍照的能力。全景型大多用在专业级相机上。全传CCD的架构介于扫描和全景之间, 有时也叫全扫描型,它分成上、下部分,上半部分是感光区,下半部是暂时存储区。整体来说全传CCD非常类似全景CCD,它的特点在于直接规划一个大型寄存区。一旦全传CCD工作,它可以迅速将电荷转移到下方的寄存区中,本身可以继续曝光拍照。这种设计,让全传同扫描一样可以使用电子快门, 同时也可以增加感光面积和速度, 兼顾动态和静态的拍摄能力。大多数数码相机采用此类CCD。

图1 全扫描CCD的内部结构

一般数码相机都带有预览(Preview)和录像(Rec)功能,在这里电子快门就起到了关键的作用。图2为电子快门控制像素的曝光过程。

图2 电子快门控制像素的曝光

图3为CCD内部示意图,当一幅图像曝光后,就需要将感光电荷从CCD输出,为了让感光的电荷输出,电荷先到垂直寄存器,通过垂直驱动脉冲(Φ1~Φ9)将每一行的电荷转移到水平寄存器,水平寄存器在水平驱动脉冲(ΦH1,ΦH2)驱动下,往CCD OUT方向移动,在末段有一放大器,ΦRS,ΦH1,ΦH2脉冲的作用下将电荷转换为电压,从CCD OUT 输出。

图3 CCD内部等效电路图

CDS(相关两次取样)

业界所称的CDS 是由时序发生器(Timing IC)、垂直驱动器(V-driver)、模拟信号处理器(AFE IC)集成的IC。它提供CCD的工作时序、电平并将CCD输出的模拟信号进行取样、放大、模数转换,将图像数据传给DSP进行图像处理。

时序发生器有一个寄存器,通过3根串口线进行各种设定:模式设定(拍照、录像或预览),电子快门和速度,ΦRS,ΦFR,ΦFCDS,ΦFS,ΦADCK,ΦDCLK相位调整,等等。

模拟信号处理器(AFE IC)有一个寄存器,通过3根串口线进行各种设定:CCD输出信号放大倍数(GAIN),默认“全黑”时电平,等等进行设定。

相关两次取样:在ΦRS,ΦH1,ΦH2脉冲的作用下CCD信号输出,当复位(RS)完成, 由于CCD暗电流的存在,CCD OUT不是为“0”,FCDS脉冲取样Vprec。当H2为高电平时,图像信号输出,FS脉冲取样Vdata,两者的差值就是图像信号Vcds,这就是相关两次取样,如图4所示。

图4 CCD的相关两次取样

电路设计

本文以某款7百万像素的数码相机设计作为说明,CCD采用SHARP公司的RJ23U3BA0FT,尺寸为1/2.5英寸,像素总数为水平3098×垂直2328,有效像素为3088×2320(共716万像素),像素单元为1.9mm×1.9mm,支持视频模式(30帧/s,15帧/s)。CDS采用SHARP公司推荐搭配此CCD的LR38678,工作电压为3.3V,TG主频67.5MHz,提供CCD的驱动频率为33.75MHz。

图5为电路原理图, 基本按照厂商推荐值进行设计。CDS的POFD输出电子快门信号经电平转换在CCD OFD输入。此CCD可以工作在不同的模式,见表1(A,B,C,取样的条数不同),通过串口设定OFDC,OFDC2电位来达到不同的工作模式表2(录像、监视和拍照),在录像、监视模式,图像是按一场输出,1VD一幅图像,但每幅图像只是抽取CCD部分条数。当在拍照模式,CCD上全部像素信号都要输出,一幅图像是由5帧输出,1VD对应1帧,具体时序见图6 CCD时序。CDS将CCD信号AD转换成D0~D11数字数据传输给DSP,同时伴随时钟信号,VD,HD信号。

图5 电路原理图

图6 CCD时序

相机的前端系统对电源要求很高,很容易将电源噪声反应在图像信号上,一般都选用低压稳压器(LDO),本文使用RT9013-33 LDO,具有极低的自有噪声和较高的电源抑制比,电流最大值达到500mA。CDS 3组电源中,以TG电源负载最大,工作时负载变化很大,一般选用较低ESR 47uF以上的钽电容,假如此路电源处理不当,会出现竖条纹。-7V和+13V也要求较低的纹波。

本文采用晶振电路能够满足要求

零件摆放和走线(LAYOUT),CCD前端系统是数码相机的心脏,是像的来源,在系统设计中处于优先考虑的位置。CCD和CDS按尽量靠近的原则。CCD输出的信号,工作频率达到33.75MHz,路径要短,最好在同一层,线周围不但要包地,PCB板上、下层也要铺地,避免受其它信号源的干扰和干扰其它信号源。CCD其它信号线H1,H2,RS,工作频率33.75MHz,也要同CCD输出信号一样处理。前端系统的CCD GND,同相机系统的GND要单独分开, 避免数字地的影响。相机尺寸朝小型化发展,在系统的设计中, 前端系统尽量远离其它干扰源,或预先屏蔽。

由于LAYOUT 和零件差异性,CCD前端系统需对高速信号H1,H2,RS,ACLK,DCLK,FCDS,FS相位调整,以便正常工作,获得最佳的图像信号。用示波器观察波形调整, 要注意选择合适探头测试。

调整CDS的DCLK相位,使传输DSP的时钟数据线同步。假如不能同步,DSP接收不到正确的图像信息。此CDS上没有对H1,H2相位的调整,只能通过外部电路调整串联电阻阻值。厂商对H1,H2,RS提供建议值,假如H1,H2偏离标准值,会造成图像信号传输不完整,影响图像质量。

调整RS,ACLK,DCLK,FCDS,FS相位,都是通过串口改变TG寄存器的数据。一种方法用示波器观察波形,使RS和H1在同一上升沿,FCDS的上升沿比H1的下降沿稍迟一点,RS的上升沿比FS的上升沿稍迟一点, ADCK的上升沿比FS的上升沿稍迟一点。另一种方法是固定好光圈,快门速度,Gain(增益)值,光源,改变不同的相位值对色板拍照, 用PHOTOSHOP打开照片,记录色阶分布中的“平均值”和“标准偏差”,“平均值”指的是照片的亮度,反应CCD的输出能力,数值越大,CCD的信号输出越大,“标准偏差”(描述亮度范围的单位)数值越大,杂讯越大。取“平均值”和“标准偏差”数值绘制图表曲线,取“平均值”和“标准偏差”平衡点,即较大的亮度和较小的杂讯。照片对应的相位值就是比较理想的调整值。或此两种方法相互运用,再加上实拍,求得调整值。

结语

数码相机的CCD的前端系统设计是整台相机设计的关键, 随着相机向高像素,高图像品质发展,工作频率越来越高,对元器件特性和前端系统要求更高。

举报

举报

举报

举报